#### 3.16.4 WD\_REGS Registers

Table 3-62 lists the memory-mapped registers for the WD\_REGS registers. All register offset addresses not listed in Table 3-62 should be considered as reserved locations and the register contents should not be modified.

Table 3-62. WD\_REGS Registers

| Offset | Acronym | Register Name                      | Write Protection | Section |

|--------|---------|------------------------------------|------------------|---------|

| 22h    | SCSR    | System Control & Status Register   | EALLOW           | Go      |

| 23h    | WDCNTR  | Watchdog Counter Register          | EALLOW           | Go      |

| 25h    | WDKEY   | Watchdog Reset Key Register        | EALLOW           | Go      |

| 29h    | WDCR    | Watchdog Control Register          | EALLOW           | Go      |

| 2Ah    | WDWCR   | Watchdog Windowed Control Register | EALLOW           | Go      |

Complex bit access types are encoded to fit into small table cells. Table 3-63 shows the codes that are used for access types in this section.

Table 3-63. WD\_REGS Access Type Codes

| Access Type              | Code    | Description                                                                                                                                                                                                                                                                          |  |  |

|--------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Read Type                |         |                                                                                                                                                                                                                                                                                      |  |  |

| R                        | R       | Read                                                                                                                                                                                                                                                                                 |  |  |

| R-0                      | R<br>-0 | Read<br>Returns 0s                                                                                                                                                                                                                                                                   |  |  |

| Write Type               |         |                                                                                                                                                                                                                                                                                      |  |  |

| W                        | W       | Write                                                                                                                                                                                                                                                                                |  |  |

| W1S                      | W<br>1S | Write<br>1 to set                                                                                                                                                                                                                                                                    |  |  |

| Reset or Default Value   |         |                                                                                                                                                                                                                                                                                      |  |  |

| -n                       |         | Value after reset or the default value                                                                                                                                                                                                                                               |  |  |

| Register Array Variables |         |                                                                                                                                                                                                                                                                                      |  |  |

| i,j,k,l,m,n              |         | When these variables are used in a register name, an offset, or an address, they refer to the value of a register array where the register is part of a group of repeating registers. The register groups form a hierarchical structure and the array is represented with a formula. |  |  |

| У                        | 77-3    | When this variable is used in a register name, an offset, or an address it refers to the value of a register array.                                                                                                                                                                  |  |  |

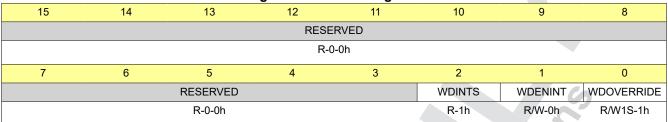

#### 3.16.4.1 SCSR Register (Offset = 22h) [Reset = 0005h]

SCSR is shown in Figure 3-52 and described in Table 3-64.

Return to the Summary Table.

System Control & Status Register

#### Figure 3-52. SCSR Register

Table 3-64. SCSR Register Field Descriptions

|      | Table 3-04. 3CSK Register Fleid Descriptions |       |       |                                                                                                                                                                                                                                                                                                                                                                                      |  |

|------|----------------------------------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit  | Field                                        | Type  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                          |  |

| 15-3 | RESERVED                                     | R-0   | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                             |  |

| 2    | WDINTS                                       | R     | 1h    | Watchdog Interrupt Status This bit indicates the state of the active-low watchdog interrupt signal (synchronized to SYSCLK). If the watchdog interrupt is used to wake the system from a low-power mode, then that mode should only be entered while this bit is high. Likewise, this bit must go high before the watchdog can be safely disabled and re-enabled. Reset type: SYSRSn |  |

| 1    | WDENINT                                      | R/W   | Oh    | Watchdog Interrupt Enable/Reset Disable This bit determines whether the watchdog triggers an interrupt (WAKE/WDOG) or a reset (WDRS) when the counter expires. Reset type: SYSRSn                                                                                                                                                                                                    |  |

| 0    | WDOVERRIDE                                   | R/W1S | 1h    | Watchdog Enable Lock Writing a 1 to this bit clears it and locks the WDDIS bit in the WDCR register. The bit will remain in this state until the next system reset. Reads of this bit return its current value. Writing a 0 to this bit has no effect. Reset type: SYSRSn                                                                                                            |  |

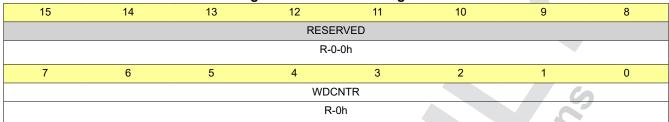

### 3.16.4.2 WDCNTR Register (Offset = 23h) [Reset = 0000h]

WDCNTR is shown in Figure 3-53 and described in Table 3-65.

Return to the Summary Table.

Watchdog Counter Register

#### Figure 3-53. WDCNTR Register

### **Table 3-65. WDCNTR Register Field Descriptions**

| Bit  | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                       |

|------|----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-8 | RESERVED | R-0  | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                          |

| 7-0  | WDCNTR   | R    | Oh    | Watchdog Counter These bits contain the current value of the watchdog counter. This counter increments with each WDCLK (INTOSC1) cycle. If the counter overflows, either an interrupt or a reset is generated based on the value of the WDINTEN bit in the SCSR register. If the correct value is written to the WDKEY register, this counter is reset to zero. Reset type: IORSn |

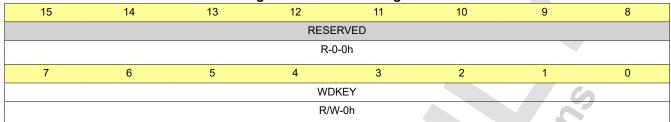

## 3.16.4.3 WDKEY Register (Offset = 25h) [Reset = 0000h]

WDKEY is shown in Figure 3-54 and described in Table 3-66.

Return to the Summary Table.

Watchdog Reset Key Register

#### Figure 3-54. WDKEY Register

**Table 3-66. WDKEY Register Field Descriptions**

| Bit  | Field    | Туре | Reset | Description                                                                                                                                                                                                                                        |

|------|----------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-8 | RESERVED | R-0  | 0h    | Reserved                                                                                                                                                                                                                                           |

| 7-0  | WDKEY    | R/W  | 0h    | Watchdog Counter Reset Writing 0x55 followed by 0xAA will cause the watchdog counter to reset to zero, preventing an overflow. Writing other values has no effect. Reads of this register return the value of the WDCR register. Reset type: IORSn |

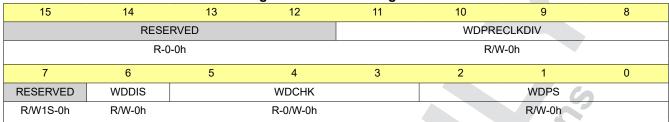

#### 3.16.4.4 WDCR Register (Offset = 29h) [Reset = 0000h]

WDCR is shown in Figure 3-55 and described in Table 3-67.

Return to the Summary Table.

Watchdog Control Register

# Figure 3-55. WDCR Register

Table 3-67. WDCR Register Field Descriptions

| Table 3-67. WDCR Register Field Descriptions |             |       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|-------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                                          | Field       | Туре  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15-12                                        | RESERVED    | R-0   | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11-8                                         | WDPRECLKDIV | R/W   | Oh    | Watchdog Clock Pre-divider These bits determine the watchdog clock pre-divider, which is the first of the two dividers between INTOSC1 and the watchdog counter clock (WDCLK). The frequency of WDCLK is given by the formulas: PREDIVCLK = INTOSC1 / Pre-divider WDCLK = PREDIVCLK / Prescaler The watchdog reset or interrupt pulse is 512 INTOSC1 cycles long, so the counter period must be longer. To guarantee this, the product of the prescaler and pre-divider must be greater than or equal to four. The default pre-divider value is 512. Reset type: IORSn |

| 7                                            | RESERVED    | R/W1S | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6                                            | WDDIS       | R/W   | 0h    | Watchdog Disable Setting this bit disables the watchdog module. Clearing this bit enables the watchdog module. This bit can be locked by the WDOVERRIDE bit in the SCSR register. The watchdog is enabled on reset. Reset type: IORSn                                                                                                                                                                                                                                                                                                                                  |

| 5-3                                          | WDCHK       | R-0/W | 0h    | Watchdog Check Bits During any write to this register, these bits must be written with the value 101 (binary). Writing any other value will immediately trigger the watchdog reset or interrupt.  Reset type: IORSn                                                                                                                                                                                                                                                                                                                                                    |

| 2-0                                          | WDPS        | R/W   | Oh    | Watchdog Clock Prescaler These bits determine the watchdog clock prescaler, which is the second of the two dividers between INTOSC1 and the watchdog counter clock (WDCLK). The frequency of WDCLK is given by the formulas: PREDIVCLK = INTOSC1 / Pre-divider WDCLK = PREDIVCLK / Prescaler The watchdog reset or interrupt pulse is 512 INTOSC1 cycles long, so the counter period must be longer. To guarantee this, the product of the prescaler and pre-divider must be greater than or equal to four. The default prescaler value is 1. Reset type: IORSn        |

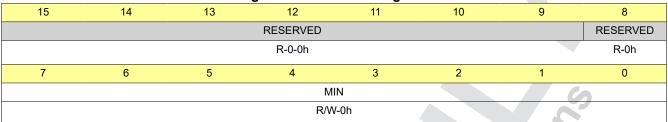

## 3.16.4.5 WDWCR Register (Offset = 2Ah) [Reset = 0000h]

WDWCR is shown in Figure 3-56 and described in Table 3-68.

Return to the Summary Table.

Watchdog Windowed Control Register

#### Figure 3-56. WDWCR Register

## Table 3-68. WDWCR Register Field Descriptions

| Bit  | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                              |

|------|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-9 | RESERVED | R-0  | 0h    | Reserved                                                                                                                                                                                                                                                                                 |

| 8    | RESERVED | R    | 0h    | Reserved                                                                                                                                                                                                                                                                                 |

| 7-0  | MIN      | R/W  |       | Watchdog Window Threshold These bits specify the lower limit of the watchdog counter reset window. If the counter is reset via the WDKEY register before the counter value reaches the value in this register, the watchdog immediately triggers a reset or interrupt. Reset type: IORSn |