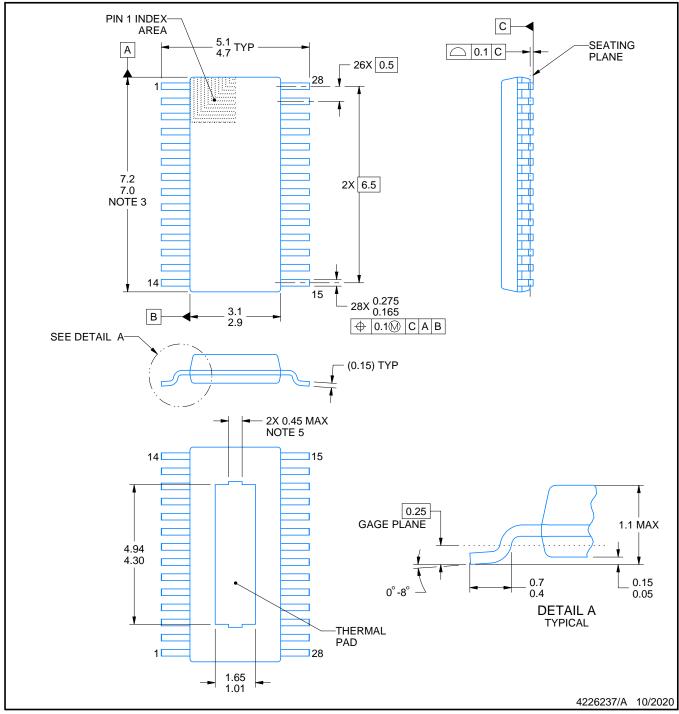

## PowerPAD<sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

## NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. No JEDEC registration as of September 2020.5. Features may differ or may not be present.

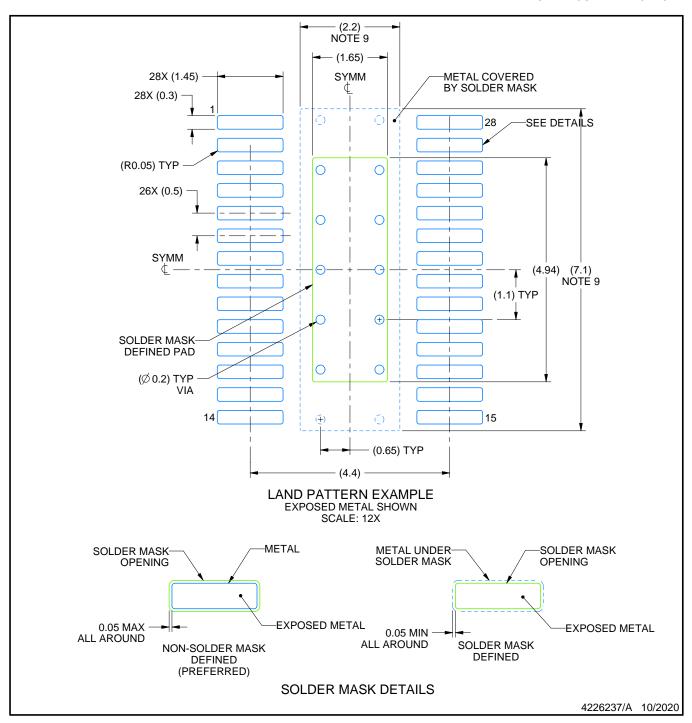

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

- 10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

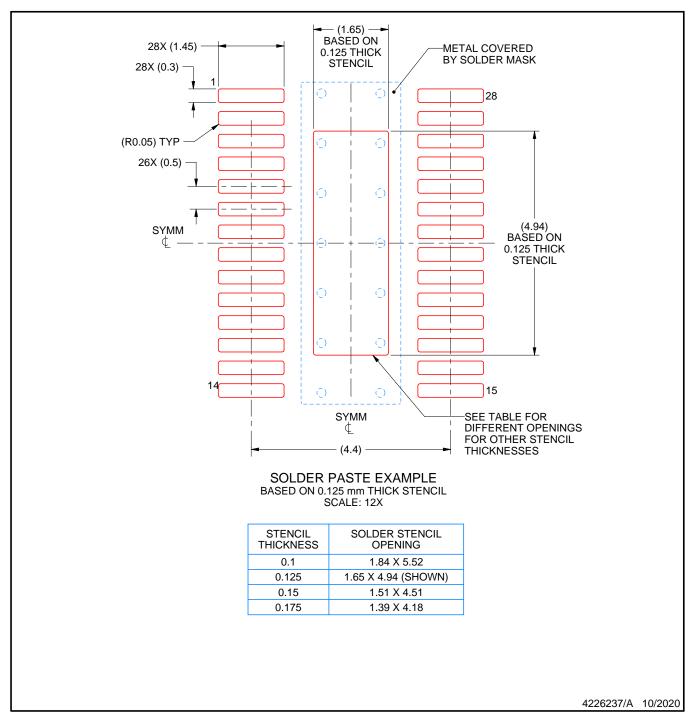

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.