**Power Supply Design Seminar**

# Common Mistakes in DC/DC Converters and How to Fix Them

Reproduced from

2018Texas Instruments Power Supply Design Seminar SEM2300

TI Literature Number: SLUP385

© 2018 Texas Instruments Incorporated

Power Supplyt Design Seminar resources are available at: www.ti.com/psds

# Common Mistakes in DC/DC Converters and How to Fix Them

Pradeep Shenoy Anthony Fagnani

### **Agenda**

- Quick review

- 10 common mistakes and how to fix them

- Converter capabilities and part selection

- Component selection

- Feature settings

- Board layout

- Measurement techniques

- Summary

"Learn from the mistakes of others. You can't live long enough to make them all yourself."

- Unknown

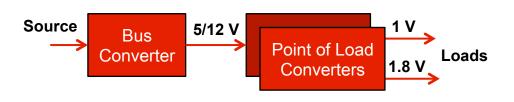

#### **Quick Review**

- DC/DC converters used as point-ofload voltage regulators

- Buck converter is most common topology

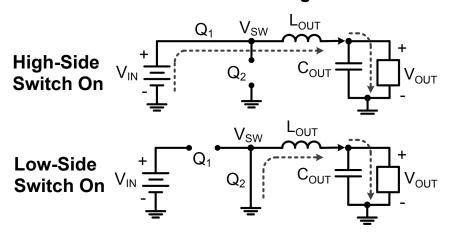

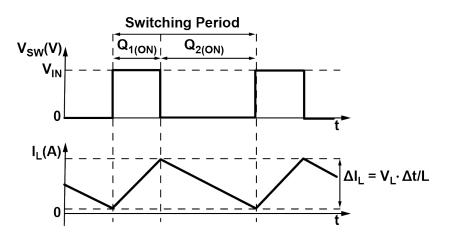

#### **Buck Converter Switching States**

#### **Steady State Waveforms**

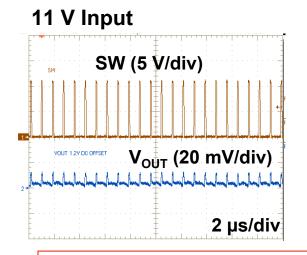

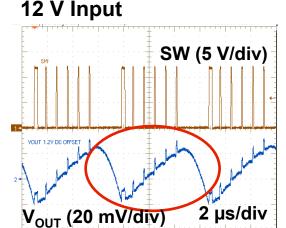

## 1) Why Are There Jumps in the Output Voltage?

Conditions: 1.2 V/0 A output, switching frequency ( $f_{SW}$ ) = 1.2 MHz, Forced continuous conduction mode (FCCM)

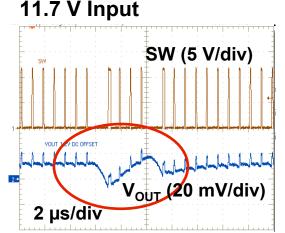

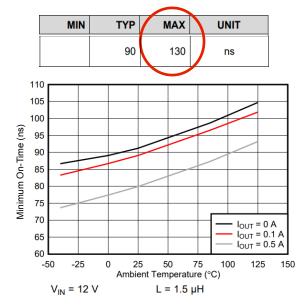

High-side switch **minimum on-time** (t<sub>ON</sub>) **violation** cannot output narrow enough SW node pulses

$$t_{ON} = \frac{1}{f_{SW}} \cdot \frac{V_{OUT}}{V_{IN}}$$

$$t_{ON} = 83 \text{ ns}$$

### 1) Duty-Cycle Limits Considerations

- Select switching frequency (f<sub>SW</sub>) based on:

- Maximum minimum on-time

- Maximum input voltage

$$f_{SW} \le \frac{1}{t_{ON(MIN)}} \cdot \frac{V_{OUT}}{V_{I(MAX)}}$$

- If min on-time is violated converters will either:

- Skip pulses

- Change switching frequency

- Output will become unregulated

Minimum on-time varies with temperature, with load and from part to part

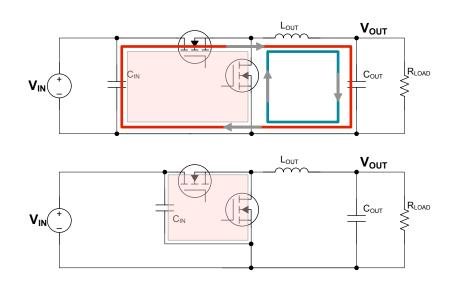

#### 2) Which Part Is Rated for 8 A?

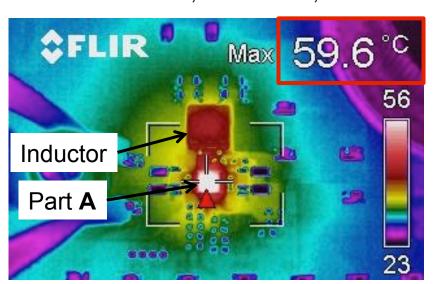

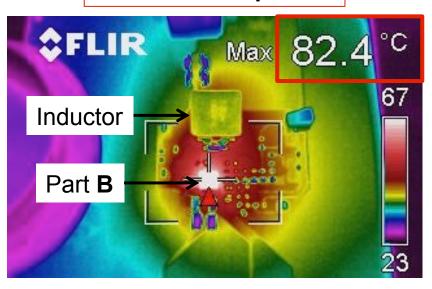

Conditions: 12 V, 1.8 V at 8 A, 700 kHz

**Both are 8 A parts!**

Part B gets over 20°C hotter and has a larger thermal footprint

Part B has little margin if 85°C ambient temperature due to 60°C temperature rise

### 2) Thermal Derating - Part Comparison

| Spec                      | Part A<br>(TPS54824) | Part B<br>(TPS54821) |

|---------------------------|----------------------|----------------------|

| V <sub>IN</sub> range     | 4.5 – 17 V           | 4.5 – 17 V           |

| Current                   | 8 A                  | 8 A                  |

| Size                      | 3.5 x 3.5 mm         | 3.5 x 3.5 mm         |

| R <sub>DS(ON)</sub>       | 14/6 mΩ              | 26/19 mΩ             |

| Modeled P <sub>LOSS</sub> | 1.69 W               | 2.38 W               |

| Simulated die temp        | 64 °C                | 81 °C                |

| Price                     | \$\$                 | \$                   |

- Part B can be used if 8 A is a short transient condition or low ambient temp

- Consider average current for thermals

- TI's WebTHERM<sup>™</sup> online tool estimates thermal performance on EVMs

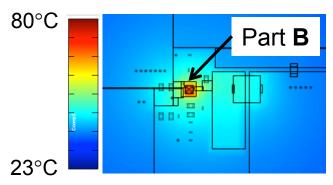

Part B Thermal Simulation Result

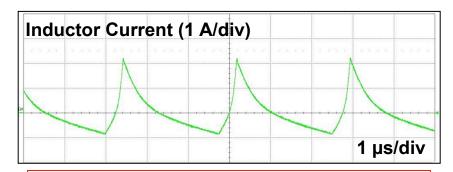

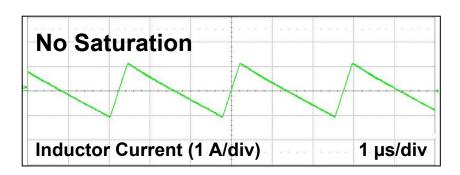

#### 3A) What's Wrong with the Inductor Current?

#### **Inductor Current Saturation!**

- Inductor current slope sharply increases when core saturates

- Saturation → low core permeability

- Causes peaking in current waveform of hard saturating cores

- Saturation can cause problems

- Can damage converter

- Leads to premature overcurrent protection

- Limits converter output current

- Consider using an inductor with a soft saturating core

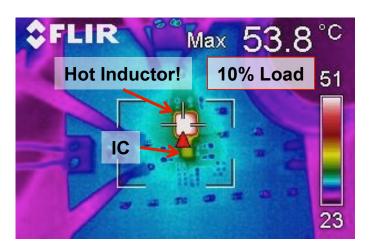

### 3B) Why Is the Inductor so Hot?

L = 240 nH  $\rightarrow$  large inductor current ripple ( $\Delta I_L$ )! (over 100%)

L = 1  $\mu$ H, has ~30% ripple

$$P_{CORE} \approx k_0 f_{SW} B_{PK}^2 \propto k_0 f_{SW} \Delta I_L^2$$

High core loss due to low inductance and high current ripple

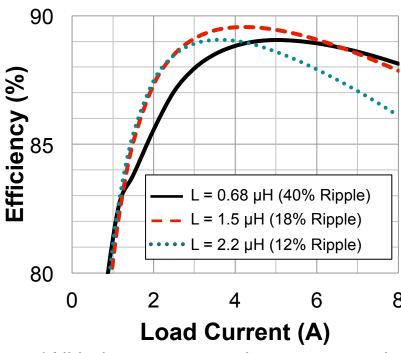

#### 3) Inductor Selection Guidelines

\*All inductors: same size, same vendor

Rule of thumb: current ripple between 15% and 40% of max load current

$$L = \left(\frac{V_{IN(MAX)} - V_{OUT}}{K \cdot I_{OUT}}\right) \left(\frac{V_{OUT}}{V_{IN(MAX)} \cdot f_{SW}}\right)$$

- For converters, use rated load current of device

- Higher inductance tends to increase peak efficiency

- Lower core loss/RMS currents

- Slower transient response

- Lower inductance has higher full load efficiency

- Lower winding resistance

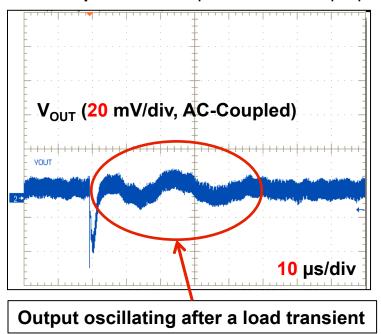

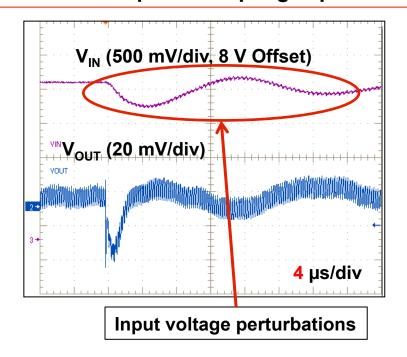

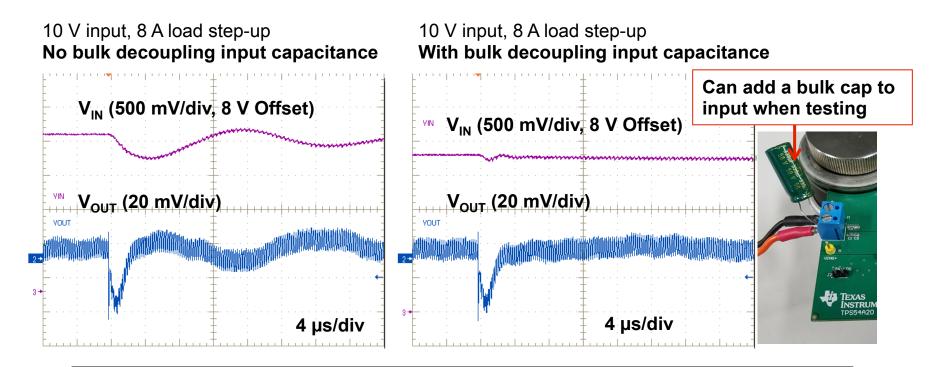

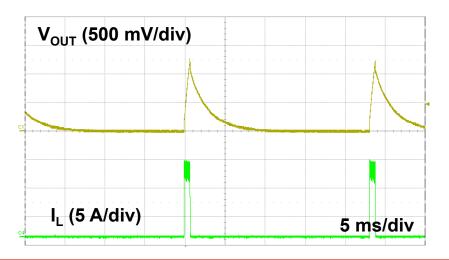

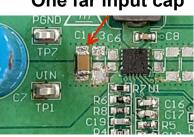

### 4A) What's Causing the Output Oscillation?

10 V input, 1.2 V output, 8 A load step-up

Insufficient input decoupling capacitance!

### 4A) Input Capacitance Comparison

Ensure bus converter is designed correctly to handle large load transients

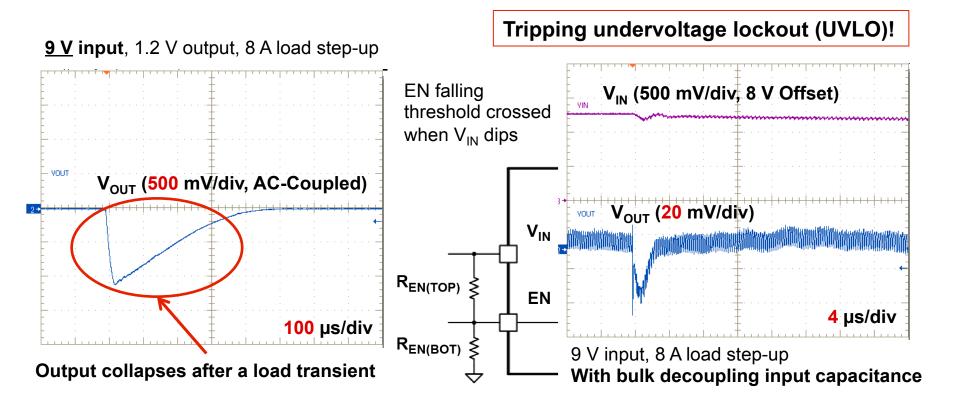

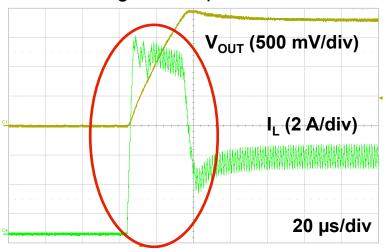

# 4B) Why Does the Output Voltage Collapse?

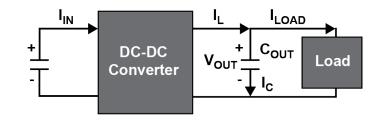

#### 4) Input/Output Capacitor Guidelines

- Ensure sufficient decoupling capacitance

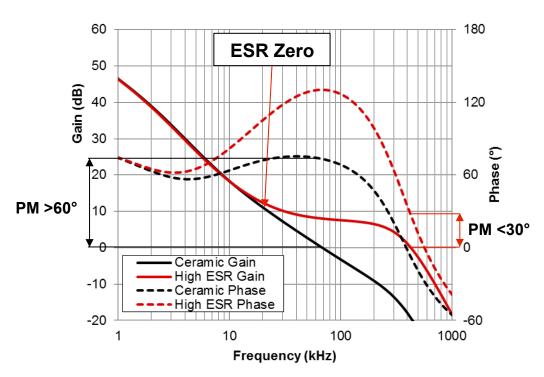

- Don't replace a low ESR cap with a "cheap" high ESR cap

- Can cause instability!

- ESR increases by factor

4 to 15 at -40 °C!

- Select output capacitance with load transient requirements accounted for

- Check RMS current rating

Different compensation is needed!

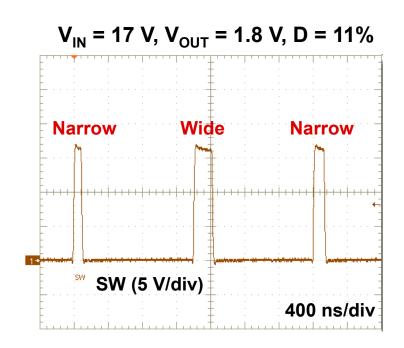

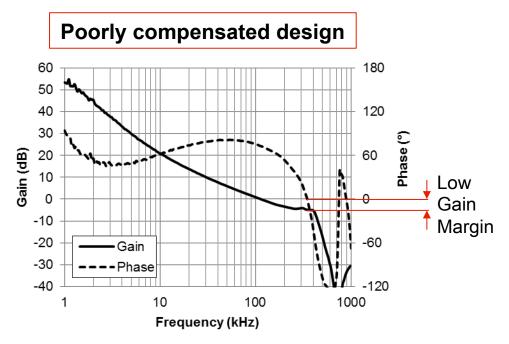

#### 5A) What Caused Wide/Narrow SW Node Pulses?

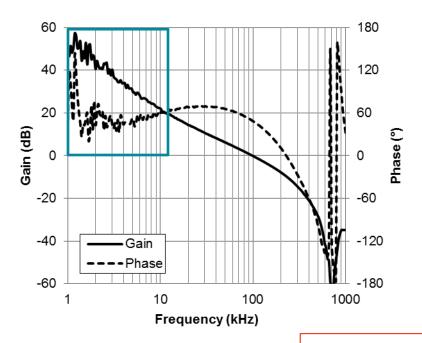

# Low gain margin! <5 dB! (Gain when phase crosses 0)

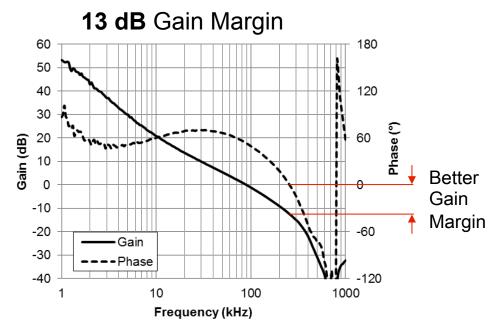

### 5A) Design for More Gain Margin

Design rule of thumb: >10 dB gain margin (across ALL operating conditions)

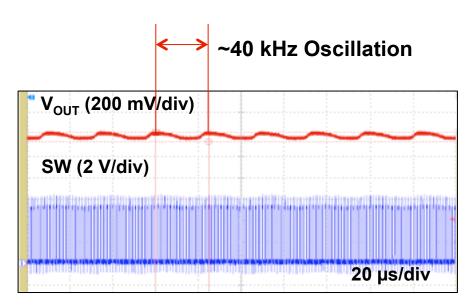

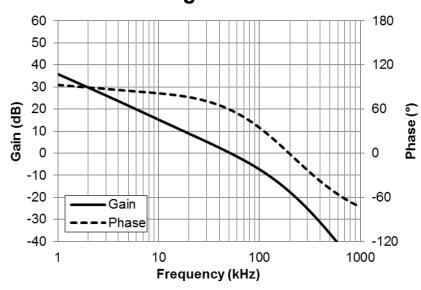

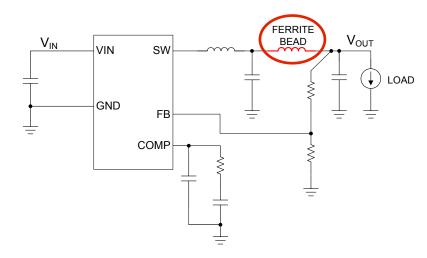

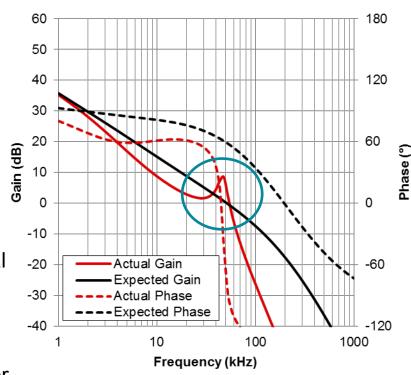

## 5B) Why Is the Output Oscillating?

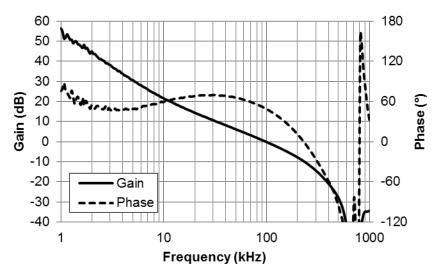

Design is stable on an EVM but output oscillates in real application

Phase Margin: 60° Gain Margin: 16.7 dB

Simulation shows sufficient phase margin and gain margin

#### 5B) Compensate for System Level Output Filter

- Second stage LC filter not included in original design and causes instability!

- Resonance frequency is ~40 kHz

- Same frequency as oscillation

- Design compensation for the actual output filter

### 6) Why Doesn't the Converter Start Up?

A very **large output capacitance** is causing the converter to hit its **overcurrent limit** during startup. The hiccup auto-restart process continues indefinitely.

### 6) Pick an Appropriate Soft Start Time

- Avoid input voltage sag due to inrush current

- Estimate converter input and output current

$$I_C = C \frac{\Delta V}{\Delta T} \qquad \qquad \bigvee_{\text{OUT}} \qquad \qquad \bigvee_{\text{Tss}} \qquad \Delta V_{\text{OUT}}$$

$$I_L = I_{LOAD} + I_C \qquad \qquad \bigvee_{\text{I}_{IN}} \Delta V_{\text{OUT}}$$

- Avoid overcurrent protection limit

- Sequence startup of supply rails

Current surge: startup time is too short

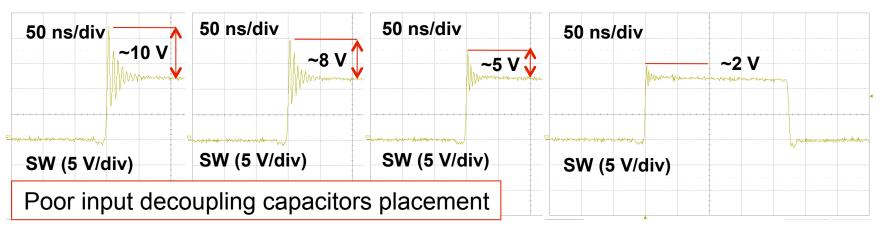

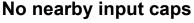

# 7) Why Is There Large SW Node Ringing?

One far input cap

10 μF, 1206

#### Two close caps

10 μF, 1206 0.1 μF, 0603

#### Two-sided, close caps

2 x 10 µF, 1206 2 x 0.1 µF, 0603

### 7) Understand Layout Parasitics

- Minimize loop area and keep components close

- Optimize grounding/return paths

- Avoid large SW node → EMI

- Keep noise sensitive analog pins/ traces (e.g. FB, COMP) away from noisy power pins/traces (e.g. SW, BOOT)

- Can add a snubber or a boot resistor to control/slow down SW node slew rate

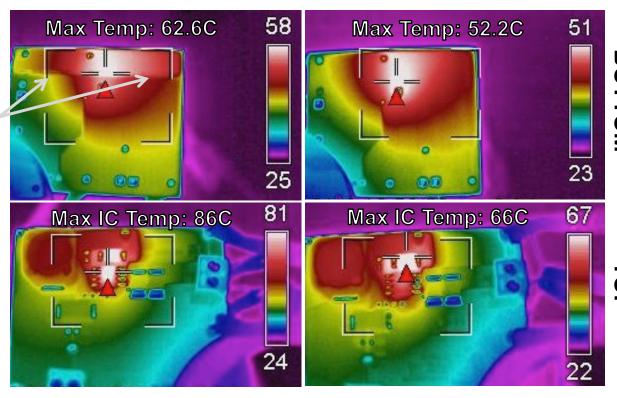

#### **Board A**

#### **Board B**

# Traces cutting through the ground plane

- Traces on the bottom layer prevent heat from spreading effectively

- Removing horizontal trace for a more solid bottom layer reduces IC temp on Board B

- Hottest component on B is the catch diode

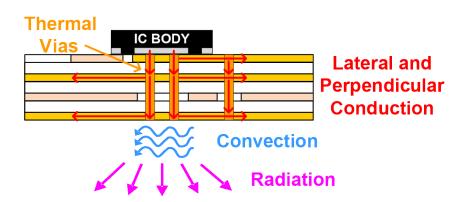

## 8) Layout PCB Considering Thermals

- Have solid ground planes to better spread heat across the layer

- Use thermal vias to spread heat to other layers

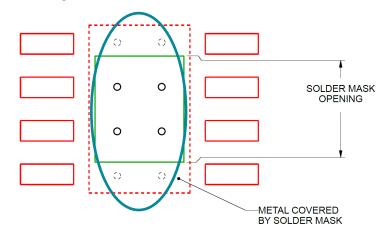

Thermal pads help to get the heat out of the IC into the PCB

#### **Footprint with Thermal Via Pattern**

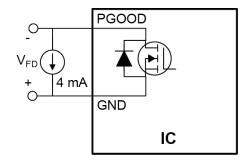

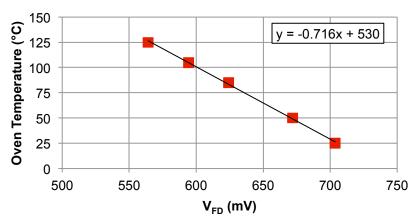

#### 8) In Situ Junction Temperature Measurement

- Common question: How much thermal margin is there in my design?

- Difficult to accurately measure IC junction temp in operation

- One option: Use the internal diode on PGOOD or similar pin

- First characterize diode voltage versus temperature

- Measure diode voltage in operation

- View <u>app note slva397</u> for more details

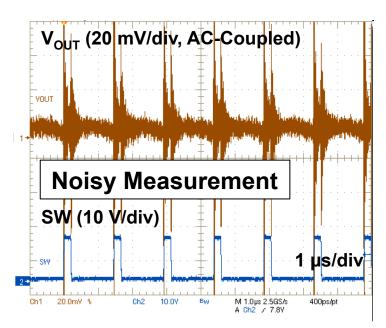

### 9) Which Output Measurement Is Right?

- Switching noise picked up from channel 2

- No bandwidth limiting

- 20 MHz bandwidth limiting

- Switch node probe removed

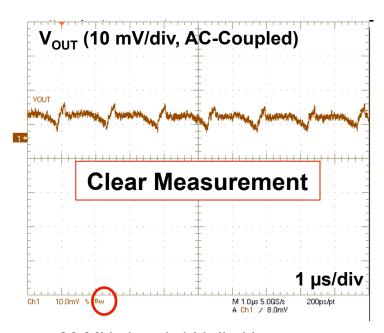

### 9) Correct Measurement Techniques

- Measure right across the output capacitor

- Use a "tip and barrel" approach

- Probe sockets for prototypes

- Don't have a flying ground lead

- Limit the bandwidth 20 MHz

- Use scope full Y-axis scale

- Consider 1:1 probes or active probes

"Tip and Barrel"

Flying Ground Lead

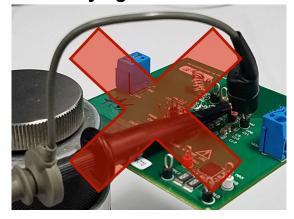

## 10A) Why Is the Bode Plot Not Smooth?

Signal injection too large

#### 10B) Why Is the Bode Plot Not Smooth?

- Signal-to-noise ratio is too low to make an accurate measurement

- At low frequencies, gain of loop attenuates injected signal

- Increasing integration time or using lower frequency IF bandwidth helps to filter noise

Signal injection too small

### 10) Optimal Small Signal Injection

- Too large → glitches at higher frequency

- Too small → inaccurate measurement

- Shape injected signal amplitude vs frequency

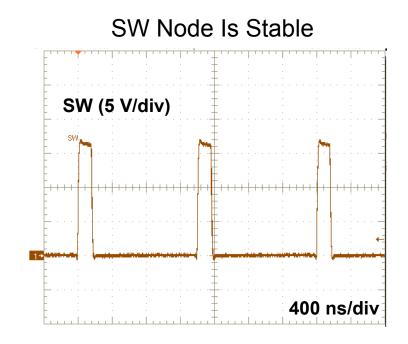

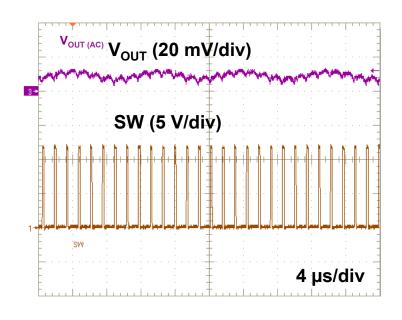

Good measurement: visible oscillation on V<sub>OUT</sub> and SW waveform is stable

#### **Summary**

- Reviewed common mistakes in point of load DC/DC converters

- Minimum on-time limitation and converter ratings

- Inductor and capacitor selection

- Compensation and startup

- Converter PCB layout to minimize parasitics and improve thermal dissipation

- Output voltage and bode plot measurement techniques

- Explained why these mistakes occur and how to avoid them

- Use this presentation as a reference when debugging and working on new designs

#### References

- Switch-mode power converter compensation made easy <a href="https://www.ti.com/seclit/ml/slup340/slup340.pdf">https://www.ti.com/seclit/ml/slup340/slup340.pdf</a>

- Power Tips: Designing a two-stage LC filter

<a href="https://e2e.ti.com/blogs\_/b/powerhouse/archive/2015/02/24/power-tips-designing-a-two-stage-lc-filter">https://e2e.ti.com/blogs\_/b/powerhouse/archive/2015/02/24/power-tips-designing-a-two-stage-lc-filter</a>

- Junction temperature measurement <u>http://www.ti.com/lit/an/slva397/slva397.pdf</u>

- Parts used in presentation

- <a href="http://www.ti.com/product/TPS54824">http://www.ti.com/product/TPS54824</a>

- http://www.ti.com/product/TPS54a20

- <a href="http://www.ti.com/product/TPS54821">http://www.ti.com/product/TPS54821</a>

#### TI Worldwide Technical Support

#### **TI Support**

Thank you for your business. Find the answer to your support need or get in touch with our support center at

www.ti.com/support

China:

http://www.ti.com.cn/guidedsupport/cn/docs/supporthome.tsp

Japan:

http://www.tij.co.jp/guidedsupport/jp/docs/supporthome.tsp

#### **Technical support forums**

Search through millions of technical questions and answers at TI's E2E<sup>TM</sup> Community (engineer-to-engineer) at

e2e.ti.com

China:

http://www.deyisupport.com/

Japan:

http://e2e.ti.com/group/jp/

#### **TI Training**

From technology fundamentals to advanced implementation, we offer on-demand and live training to help bring your next-generation designs to life. Get started now at

training.ti.com

China:

http://www.ti.com.cn/general/cn/docs/gencontent.tsp?contentId=71968

Japan:

https://training.ti.com/jp

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

B011617

The platform bar and E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated