| RULES | COMPONENTS                                                                                       | FUNCTION             | IMPACT                                   | GUIDELINES                                                                                                                                                                                                                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------|----------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     |                                                                                                  | PCB layer<br>stackup | Thermal, efficiency, signal integrity    | Multi-layer PCB is suggested. Allocate<br>at least one ground layer. The<br>BQ24800EVM and BQ24780SEVM<br>uses a 4-layer PCB (top layer, power<br>ground layer, signal layer and bottom<br>layer).                                                                                                                                           |

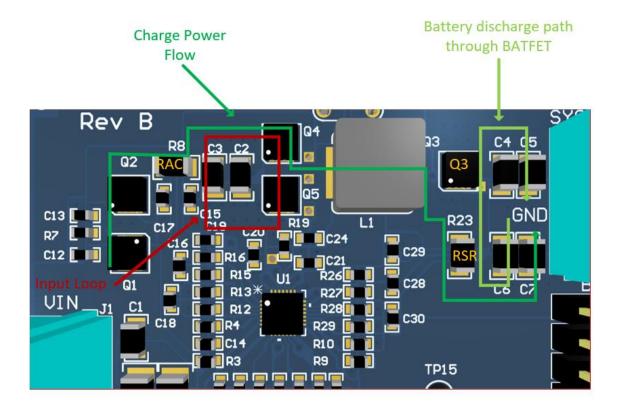

| 2     | CBUS, Q4<br>(Buck high<br>side), Q5<br>(buck low<br>side)                                        | Input Loop           | High frequency<br>noise, ripple          | Input capacitors, Q4, Q5 forms the<br>input loop of a buck converter. It is<br>best to put them on the same side.<br>Connect them with large copper to<br>reduce the parasitic resistance. Move<br>part of CBUS to the other side of PCB<br>for high density design.                                                                         |

| 3     | Q1 (ACFET),<br>Q2 (RBFET),<br>RAC,<br>Q4 (Buck high<br>side),<br>L1 (power<br>stage<br>inductor) | Current<br>path      | Efficiency                               | The current path from input to<br>battery would need to be optimized<br>for efficiency. Wider trace width<br>reduces copper loss. Pay attention to<br>via resistance if they are not<br>on the same side. The number of vias<br>can be estimated as 1 to<br>2A/via for a 10-mil via with 1 oz.<br>copper thickness.                          |

| 4     | RSR, Q3<br>(BATFET)                                                                              | Current<br>path      | Efficiency, battery<br>voltage detection | Place Q3 and RSR near the battery<br>terminal. The current path from<br>battery to output would need to be<br>optimized for efficiency. Wider trace<br>width reduces copper loss.<br>Pay attention to via resistance if they<br>are not on the same side.<br>The device detects the battery<br>voltage through SRN near battery<br>terminal. |

| 5     | Q4 (Buck high<br>side), Q5<br>(buck low<br>side), L1<br>(power stage<br>inductor)                | Power<br>stage       | Thermal, efficiency                      | Place Q4, Q5, L1 next to each other.<br>Allow enough copper area for<br>thermal dissipation. The copper area<br>is suggested to be 2x to 4x of the pad<br>size. Multiple thermal vias can be<br>used to connect more copper layers<br>together and dissipate more heat.                                                                      |

| 6     | RAC, RSR                                                                                         | Current<br>sense     | Regulation accuracy                      | Use Kelvin-sensing technique for RAC<br>and RSR current sense resistors.<br>Connect the current sense traces to<br>the center of the pads, and run<br>current sense traces as differential<br>pairs.                                                                                                                                         |

| 7 | Small      | IC bypass           | Noise, jittering, ripple                                            | Place VCC cap, REGN caps, and other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|------------|---------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | capacitors | caps                |                                                                     | filtering caps near IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8 |            | Ground<br>partition | Measurement<br>accuracy, regulation<br>accuracy, jitters,<br>ripple | Separate analog ground(GND on<br>EVM) and power ground(PGND on<br>EVM) is preferred. PGND should be<br>used for all power stage related<br>ground net. GND should be used for<br>all sensing networks. Some example<br>of sensing networks include ACP,<br>ACN, SRP, SRN, ILIM, etc. Connect all<br>analog grounds to a dedicated low-<br>impedance copper plane, which is<br>tied to the power ground underneath<br>the IC exposed pad. Connect analog<br>ground and power ground together<br>using power pad as the single ground<br>connection point. |

Sample Layout