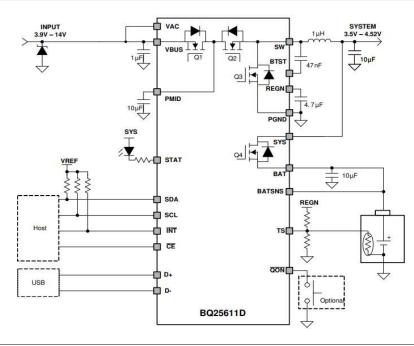

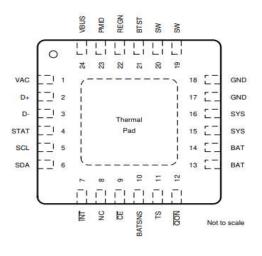

|           |          |                            |                             |       |        |                                                                                                                                                                  | BQ25611D SCHMATIC CHECKLIST                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|----------|----------------------------|-----------------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME  |          | REQUIREMENT                | COMPONENT                   | MIN   | TYP    | MAX                                                                                                                                                              | DESCRIPTION                                                                                              | COMMENTS AND RELEVANT EQUATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D+/D-     | 2,3      | Optional                   |                             |       |        |                                                                                                                                                                  | USB data line pair<br>Positive line of the USB data line pair.                                           | D+/D- based USB host/charging port detection. The detection includes data contact detection (DCD), pr/mary and secondary detection in BC1.2 and non-standard adaptors.                                                                                                                                                                                                                                                                                                                                                                                                |

|           |          | Optional                   |                             |       |        |                                                                                                                                                                  | Negative line of the USB data line pair.                                                                 | primary and secondary detection in best 2 and non-standard ddaptors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |          |                            |                             |       |        |                                                                                                                                                                  | Open drain charge status output                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| STAT      | 4        | Optional                   | STAT resistor               |       | 2.2 kΩ | 10 kΩ                                                                                                                                                            | Connect to the pull up rail via 2.2-k $\Omega$ or 10-k $\Omega$ resistor.                                | 1. If not used, leave it floating. 2. The STAT pin indicates charger status. Connect a current limiting resistor<br>and an LED from a rail to this pin. 3. Charge in progress: LOW; Charge complete or charger in SLEEP mode:<br>HIGH; Charge suspend (fault response): 1.Hz, 50% duty cycle Pulses                                                                                                                                                                                                                                                                   |

|           |          |                            |                             |       |        |                                                                                                                                                                  | I2C Interface clock and data                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SCL/SDA   | 5-6      | Optional                   | SCL resistor                |       | 10 kΩ  |                                                                                                                                                                  | Connect SCL to the logic rail through a $10-k\Omega$ resistor.                                           | If I2C communication is not used, leave it floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |          | Optional                   | SDA resistor                |       | 10 kΩ  |                                                                                                                                                                  | Connect SDA to the logic rail through a 10-kΩ resistor.                                                  | If I2C communication is not used, leave it floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INT       | 7        | Optional                   | INT resistor                |       | 10 kΩ  |                                                                                                                                                                  | Open-drain Interrupt Output<br>Connect the INT to a logic rail via 10-kΩ resistor.                       | 1. If not used, leave it floating, 2. The INT pin sends an active low, 256-µs pulse to host to report charger device status and fault.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NC        | 8        |                            |                             |       |        |                                                                                                                                                                  | No connect                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |          | Optional                   |                             |       |        |                                                                                                                                                                  |                                                                                                          | Float this pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| /CE       | 9        |                            |                             |       |        |                                                                                                                                                                  | Active low Charge Enable pin                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| /02       |          | Required                   |                             |       |        |                                                                                                                                                                  |                                                                                                          | 1. /CE pin must be pulled High or Low. 2. Battery charging is enabled when REG01[4] = 1 and CE pin = Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |          |                            |                             |       |        |                                                                                                                                                                  | Battery voltage sensing pin for charge voltage regulation                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DATCHC    | 10       |                            |                             |       |        |                                                                                                                                                                  |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BATSNS 10 | Optional |                            |                             |       |        | In order to minimize the parasitic trace resistance during<br>charging, BATSNS pin is connected to the positive<br>terminal of battery pack as close as possible | If BATSNS pin is open, BATSNS_STAT bit is set to 1 and charger regulates the battery voltage through BAT |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |          |                            |                             |       |        |                                                                                                                                                                  | Temperature qualification voltage inputs for JEITA                                                       | pin. If BATSNS is unused, this pin should be floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TS        | 11       | Optional if<br>TS_IGNORE=1 | TS resistors and thermistor |       |        |                                                                                                                                                                  | Connect a negative temperature coefficient thermistors.<br>Recommend 103AT-2 thermistors.                | 1. If thermistor is not used, set TS pin voltage within normal range or set TS_IGNORE to 1 2. If thermistor is used, program temperature window with a resistor divider from REGN to TS to GND. Charge suspends when TS pin is out of range.                                                                                                                                                                                                                                                                                                                          |

|           |          |                            |                             |       |        |                                                                                                                                                                  | BATFET enable/reset control input                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| /QON      | 12       | Optional                   |                             |       | Switch |                                                                                                                                                                  |                                                                                                          | 1.If not used, leave it floating. 2.The pin contains an internal pull-up to maintain default high logic. 3.When<br>BATFET is in ship mode, a logic low of tSHIPMODE duration turns on BATFET to exit ship mode. When the<br>BATFET is not in ship mode, a logic LOW of tQON_RST (minimum 8 s) duration resets SYS (system power) b<br>turning BATFET off for tBATFET_RST (minimum 250ms) and then re-enables BATFET to provide full system<br>power reset. The host chooses the BATFET reset function with VBUS unplugged or not through I2C bit<br>BATFET_RST_WNBUS. |

| VAC       | 1        |                            |                             |       |        |                                                                                                                                                                  | Charge input voltage sense                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VAC       | <u> </u> | Required                   |                             |       |        |                                                                                                                                                                  |                                                                                                          | Charge input voltage sense. This pin must be connected to VBUS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |          |                            |                             |       |        |                                                                                                                                                                  | Charge input voltage                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VBUS      | 24       | Required                   | VBUS caps                   | 1uF   |        |                                                                                                                                                                  |                                                                                                          | <ol> <li>Place a 1-μF ceramic capacitor from VBUS to PGND and place it as close as possible to IC. 2. It is recommended to have a total of ~10uF capacitance at VBUS &amp; PMID for USB input compliance.</li> </ol>                                                                                                                                                                                                                                                                                                                                                  |

|           |          |                            |                             |       |        |                                                                                                                                                                  | Actual input source to the charger                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PMID      | 23       | Required                   | PMID caps                   | 8.2uF | 10uF   |                                                                                                                                                                  |                                                                                                          | Connected to the drain of the reverse blocking MOSFET (RBFET) and the drain of HSFET. Put 10 $\mu F$ ceramic capacitor on PMID to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |          | Optional                   | PMID caps                   |       | 1nF    |                                                                                                                                                                  |                                                                                                          | For optimal EMC add a 1nF, 0402 capacitor with a minimal loop to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BAT       | 13-14    | Required                   | BAT caps                    | 10uF  | 10uF   |                                                                                                                                                                  | Positive battery connection point                                                                        | Battery connection point to the positive terminal of the battery pack. The internal BATFET and current sensing is connected between SYS and BAT. 1. Connect a 10 µF closely to the BAT pin. 2. Charger may operate normally when battery is not connected.                                                                                                                                                                                                                                                                                                            |

|           |          |                            |                             |       |        |                                                                                                                                                                  | Converter output connection point                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SYS       | 15-16    | Required                   | SYS caps                    | 10uF  | 20uF   | 20uF                                                                                                                                                             |                                                                                                          | Connect a 20 μF closely to the SYS pin. The preferred ceramic capacitor is 10V or higher rating, X7R or X5R.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |       |          |                 |         |         |        | Switching node connecting to output inductor |                                                                                                                                                                                                                                               |

|-------------|-------|----------|-----------------|---------|---------|--------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW          | 19-20 | Required | Output inductor | 1uH     |         | 2.2uH  |                                              | Switching node output. Connected to output inductor. The charger device has internal loop compensator.                                                                                                                                        |

|             |       | Optional | SW Resistor     |         | *Ω      |        | Contraction and a south has also alt         | Snubber circuit values empirically determined if required. Recommend unpopulated footprint on new                                                                                                                                             |

|             |       | Optional | SW Cap          |         | * F     |        | Switching converter snubber circuit          | designs.                                                                                                                                                                                                                                      |

|             |       |          |                 |         |         |        | PWM high side driver positive supply.        |                                                                                                                                                                                                                                               |

| BTST        | 21    | Required | BTST-SW cap     | 0.047uF | 0.047uF | 0.047u | F                                            | Connect the 0.047µF, 25V rated bootstrap capacitor from SW to BTST.                                                                                                                                                                           |

|             |       | Optional | BTST resistor   |         | *Ω      |        | Bootstrap capacitor series snubbing resistor | Helps with EMI performance. Recommend a 0ohm, 0402 on new designs.                                                                                                                                                                            |

|             |       |          |                 |         |         |        | PWM low side driver positive supply output.  |                                                                                                                                                                                                                                               |

| REGN        | 22    | Required | REGN cap        | 4.7uF   | 4.7uF   | 4.7uF  |                                              | Connect a 4.7 µF (10V rating) ceramic capacitor from REGN to analog GND. The capacitor should be placed                                                                                                                                       |

|             |       | Required | KEGN cap        | 4.70    | 4.7ur   | 4.7uF  |                                              | close to the IC. REGN must serve as the bias rail of the TS pin.                                                                                                                                                                              |

|             |       |          |                 |         |         |        | Power ground                                 |                                                                                                                                                                                                                                               |

| GND         | 17-18 | Required |                 |         |         |        |                                              | On the PCB layout, connect the input and output capacitors of the charger directly to GND. A single point<br>connection is recommended between power GND and the analog GND near the IC PGND pin.                                             |

| Thermal PAD |       | Required |                 |         |         |        |                                              | Thermal pad and ground reference. This pad is ground reference for the device and it is also the thermal<br>pad used to conduct heat from the device. This pad should be tied externally to a ground plane through PCB<br>vias under the pad. |

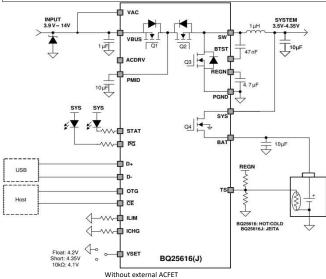

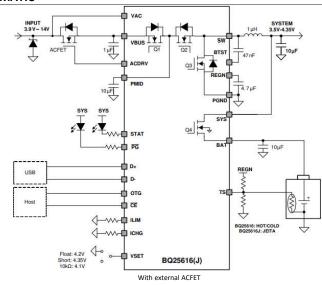

## BQ25616(J) TYPICAL SCHEMATIC

|          |          |                      |                             |         |          |         | BQ25616(J) SCHMATIC CHECKLIST                                                             | г                                                                                                                                                                                                                                                                                                                      |

|----------|----------|----------------------|-----------------------------|---------|----------|---------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME |          | REQUIREMENT          | COMPONENT                   | MIN     | ТҮР      | MAX     | DESCRIPTION                                                                               | COMMENTS AND RELEVANT EQUATIONS                                                                                                                                                                                                                                                                                        |

|          |          |                      |                             |         |          |         | USB data line pair                                                                        |                                                                                                                                                                                                                                                                                                                        |

| D+/D-    | 3,4      | Optional             |                             |         |          |         | Positive line of the USB data line pair.                                                  | <ol> <li>D+/D- based USB host/charging port detection. The detection includes data contact detection (DCD),<br/>primary and secondary detection in BC1.2 and non-standard adaptors.</li> </ol>                                                                                                                         |

|          |          | Optional             |                             |         |          |         | Negative line of the USB data line pair.                                                  | printery and secondary detection in bears and non-standard dalaptors.                                                                                                                                                                                                                                                  |

|          |          |                      |                             |         |          |         | Open drain charge status output                                                           |                                                                                                                                                                                                                                                                                                                        |

| STAT     | 5        | Optional             | STAT resistor               |         | 2.2 kΩ   | 10 kΩ   | Connect to the pull up rail via 2.2-kΩ or 10-kΩ resistor.                                 | <ol> <li>If not used, leave it floating. 2. The STAT pin indicates charger status. Connect a current limiting resistor<br/>and an LED from a rail to this pin. 3. Charge in progress: LOW; Charge complete or charger in SLEEP mode:<br/>HIGH; Charge suspend (fault response): 1-Hz, 50% duty cycle Pulses</li> </ol> |

| OTG      | 6        | Optional             |                             |         |          |         | Active high boost mode enable pin                                                         | 1. If OTG boost mode is not used, short it to ground. 2. When this pin is pulled HIGH, OTG is enabled. 3. OTG cannot be floating                                                                                                                                                                                       |

|          |          |                      |                             |         |          |         | Open drain active low power good indicator.                                               |                                                                                                                                                                                                                                                                                                                        |

| /PG      | 7        | Optional             | PG resistor                 |         | 2.2 kΩ   | 10 kΩ   | Connect to the pull up rail via $10\text{-}k\Omega$ resistor.                             | LOW indicates a good input source if the input voltage is between UVLO and ACOV, above SLEEP mode<br>threshold, and current limit is above 30 mA.                                                                                                                                                                      |

|          |          |                      |                             |         |          |         | Charge pump output to drive external N-channel<br>MOSFET (ACFET)                          |                                                                                                                                                                                                                                                                                                                        |

| ACDRV    | 2        | Optional             | ACFET                       |         |          |         |                                                                                           | It provides 6V voltage above VBUS as gate drive to turn on ACFET when VAC voltage is below ACOV                                                                                                                                                                                                                        |

|          |          | Optional             | ACLET                       |         |          |         |                                                                                           | threshold (14.2- V) and above UVLO. Leave ACDRV floating if external OVP is not being used.                                                                                                                                                                                                                            |

| /CE      | 9        | Description          |                             |         |          |         | Active low Charge Enable pin                                                              | When this size is driven law, bettern shareing is enabled                                                                                                                                                                                                                                                              |

|          |          | Required             |                             |         |          |         | Input current limit setting                                                               | When this pin is driven low, battery charging is enabled.                                                                                                                                                                                                                                                              |

|          |          |                      |                             |         |          |         | input current init betting                                                                |                                                                                                                                                                                                                                                                                                                        |

| ILIM     | 8        | Required             | ILIM resistor               |         | *Ω       |         | input current limit                                                                       | 1. The acceptable range for ILIM current is 500 mA - 3200 mA. 2. The resistor based input current limit is<br>effective only when the input adapter is detected as unknown. Otherwise, the input current limit is<br>determined by D+/D– detection outcome. IINDPM = KILIM/RILIM                                       |

|          |          |                      |                             |         |          |         | Charge current limit setting                                                              |                                                                                                                                                                                                                                                                                                                        |

| ICHG     | 10       | Required             | ICHG resistor               |         | *Ω       |         | A resistor is connected from ICHG pin to ground to set<br>charge current limit            | The acceptable range for charge current is 300 mA – 3000 mA. ICHG = KICHG/RICHG.                                                                                                                                                                                                                                       |

|          |          |                      |                             | 1       |          |         | Temperature qualification voltage inputs for JEITA                                        |                                                                                                                                                                                                                                                                                                                        |

| TS       | 11       | Required             | TS resistors and thermistor |         |          |         | Connect a negative temperature coefficient thermistors.<br>Recommend 103AT-2 thermistors. | 1. If thermistor is not used, set TS pin voltage within normal range. 2. If thermistor is used, program temperature window with a resistor divider from REGN to TS to GND. Charge suspends when TS pin is out of range.                                                                                                |

|          |          |                      |                             |         |          |         | Default battery charge voltage setting                                                    |                                                                                                                                                                                                                                                                                                                        |

| VSET     | 12       | Required             | VSET resistor               |         | *Ω       |         | Program battery regulation voltage with a resistor pull-<br>down from VSET to GND.        | RPD > 50kΩ (float pin) = 4.2V<br>RPD < 500Ω (short to GND) = 4.35V<br>5kΩ < RPD < 25kΩ = 4.1V                                                                                                                                                                                                                          |

|          |          |                      |                             |         |          |         | Charge input voltage sense                                                                |                                                                                                                                                                                                                                                                                                                        |

| VAC      | 1        | Required             |                             |         |          |         |                                                                                           | Optional external n-channel ACFET is placed between VAC and VBUS. When VAC voltage is below ACOV<br>threshold (14.2-V) and above UVLO, ACFET turns on to connect VAC to VBUS, and power up the charger IC.<br>Short VAC and VBUS if ACFET is not to be used.                                                           |

| VBUS     | 24       |                      |                             |         |          |         | Charge input voltage                                                                      | 1. Place a 1-µF ceramic capacitor from VBUS to PGND and place it as close as possible to IC. 2. It is                                                                                                                                                                                                                  |

| *503     | 24       | Required             | VBUS caps                   | 1uF     |          |         |                                                                                           | 1. Place a 1-µF ceramic capacitor from VBUS to PolyD and place it as close as possible to it. 2. It is recommended to have a total of ~10µF capacitance at VBUS & PMID for USB input compliance.                                                                                                                       |

|          |          |                      |                             |         |          |         | Actual input source to the charger                                                        | Connected to the drain of the reverse blocking MOSFET (RBFET) and the drain of HSFET. Put 10 µF ceramic                                                                                                                                                                                                                |

| PMID     | 23       | Required             | PMID caps                   | 8.2uF   | 10uF     |         |                                                                                           | capacitor on PMID to GND.                                                                                                                                                                                                                                                                                              |

|          |          | Optional             | PMID caps                   |         | 1nF      |         |                                                                                           | For optimal EMC add a 1nF, 0402 capacitor with a minimal loop to GND                                                                                                                                                                                                                                                   |

|          |          |                      |                             |         |          |         | Positive battery connection point                                                         |                                                                                                                                                                                                                                                                                                                        |

| BAT      | 13-14    | Required             | BAT caps                    | 10uF    | 10uF     |         |                                                                                           | Battery connection point to the positive terminal of the battery pack. The internal BATFET and current<br>sensing is connected between SYS and BAT. 1. Connect a 10 µF closely to the BAT pin. 2. Charger may<br>operate normally when battery is not connected.                                                       |

|          |          |                      |                             |         |          |         | Converter output connection point                                                         |                                                                                                                                                                                                                                                                                                                        |

| SYS      | 15-16    | Required             | SYS caps                    | 10uF    | 20uF     | 20uF    |                                                                                           | Connect a 20 µF closely to the SYS pin. The preferred ceramic capacitor is 10V or higher rating, X7R or X5R.                                                                                                                                                                                                           |

|          |          |                      |                             |         |          |         | Switching node connecting to output inductor                                              |                                                                                                                                                                                                                                                                                                                        |

| SW       | 19-20    | Required             | Output inductor             | 1uH     |          | 2.2uH   |                                                                                           | Switching node output. Connected to output inductor. The charger device has internal loop compensator.                                                                                                                                                                                                                 |

|          |          | Optional<br>Optional | SW Resistor<br>SW Cap       |         | *Ω<br>*F |         | Switching converter snubber circuit                                                       | Snubber circuit values empirically determined if required. Recommend unpopulated footprint on new designs.                                                                                                                                                                                                             |

|          |          |                      |                             |         |          |         | PWM high side driver positive supply.                                                     |                                                                                                                                                                                                                                                                                                                        |

| BTST     | 21       | Required             | BTST-SW cap                 | 0.047uF | 0.047uF  | 0.047uF |                                                                                           | Connect the 0.047µF, 25V rated bootstrap capacitor from SW to BTST.                                                                                                                                                                                                                                                    |

|          |          | Optional             | BTST resistor               |         | *Ω       |         | Bootstrap capacitor series snubbing resistor                                              | Helps with EMI performance. Recommend a 0ohm, 0402 on new designs.                                                                                                                                                                                                                                                     |

| REGN     | 22       |                      |                             |         |          |         | PWM low side driver positive supply output.                                               | Connect a 4.7 µF (10 Vrating) ceramic capacitor from REGN to analog GND. The capacitor should be placed                                                                                                                                                                                                                |

| NLON     | <u> </u> | Required             | REGN cap                    | 4.7uF   | 4.7uF    | 4.7uF   |                                                                                           | close to the IC. REGN also serves as bias rail of the TS pin.                                                                                                                                                                                                                                                          |

|          |          |                      |                             |         |          |         | 1                                                                                         | I                                                                                                                                                                                                                                                                                                                      |

|             |       |          |  | Power ground |                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------|----------|--|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND         | 17-18 | Required |  |              | On the PCB layout, connect the input and output capacitors of the charger directly to GND. A single point<br>connection is recommended between power GND and the analog GND near the IC PGND pin.                                                                                                                                         |

| Thermal PAD |       | Required |  |              | Ground reference for the device that is also the thermal pad used to conduct heat from the device. This<br>connection serves two purposes. 1) Provide an electrical ground connection for the device. 2. Provide a low<br>thermal-impedance path from the device die to the PCB. This pad should be tied externally to a ground<br>plane. |

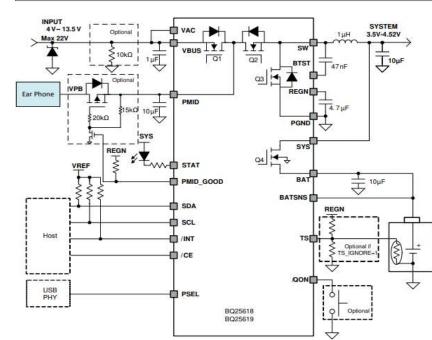

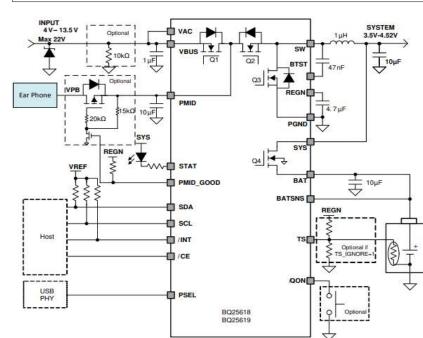

## **BQ25618 TYPICAL SCHEMATIC**

|   |       | 1 | 2     | 3        | 4      | 5      |

|---|-------|---|-------|----------|--------|--------|

| A | GND   | ( | sw    |          | (VBUS) |        |

| В |       | C | sw    | (PMID)   | (VBUS) |        |

| c | (BAT) | ( | SYS   | (BTST)   | REGN   | (PSEL) |

| D | BAT   | ( | SYS)  |          | (/QN)  |        |

| E | (BAT) |   | SYS   | ( /CE )  | (SDA)  | (STAT) |

| F | (BAT) | ( | sys ) | (BATSNS) |        | SCL    |

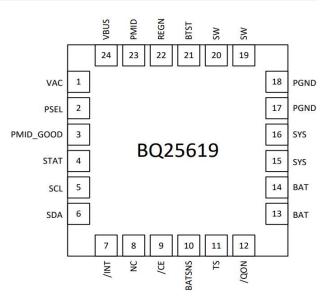

|           |                 |                            |                             |       |        |       | BQ25618 SCHMATIC CHECKLIST                                                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------|-----------------|----------------------------|-----------------------------|-------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN NAME  |                 | REQUIREMENT                | COMPONENT                   | MIN   | TYP    | MAX   | DESCRIPTION                                                                                                                                                      | COMMENTS AND RELEVANT EQUATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| PSEL      | C5              | Required                   |                             |       |        |       | Power Source Selection Input                                                                                                                                     | HIGH indicates 500 mA input current limit. LOW indicates 2.4A input current limit. Once the device gets into<br>host mode, the host can program a different input current limit to the IINDPM register.                                                                                                                                                                                                                                                                                                                                                            |  |  |

|           |                 |                            |                             |       |        |       | Open drain active high PMID good output                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| PMID_GOOD | D5              | Optional                   |                             |       |        |       | Connect to the pull up rail REGN through 10 kΩ resistor                                                                                                          | HIGH indicates PMID voltage is below 5.2V and the current through Q1 is below 110% of input current limit.<br>This signal can be used to drive external PMOS FET to disconnect the PMID under charging load when boost<br>mode output voltage is too high or output current is too high.                                                                                                                                                                                                                                                                           |  |  |

|           |                 |                            |                             |       |        |       | Open drain charge status output                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| STAT      | E5              | Optional                   | STAT resistor               |       | 2.2 kΩ | 10 kΩ | Connect to the pull up rail via 2.2-k $\Omega$ or 10-k $\Omega$ resistor.                                                                                        | 1. If not used, leave it floating. 2. The STAT pin indicates charger status. Connect a current limiting resistor<br>and an LED from a rail to this pin. 3. Charge in progress: LOW; Charge complete or charger in SLEEP mode:<br>HIGH; Charge suspend (fault response): 1-Hz, 50% duty cycle Pulses                                                                                                                                                                                                                                                                |  |  |

|           |                 |                            |                             |       |        |       | I2C Interface clock and data                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SCL/SDA   | F5,E4           | Optional                   | SCL resistor                |       | 10 kΩ  |       | Connect SCL to the logic rail through a 10- $k\Omega$ resistor.                                                                                                  | If I2C communication is not used, leave it floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|           |                 | Optional                   | SDA resistor                |       | 10 kΩ  |       | Connect SDA to the logic rail through a 10-k $\Omega$ resistor.                                                                                                  | If I2C communication is not used, leave it floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|           |                 |                            |                             |       |        |       | Open-drain Interrupt Output                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| INT       | F4              | Optional                   | INT resistor                |       | 10 kΩ  |       | Connect the INT to a logic rail via 10-k $ \Omega$ resistor.                                                                                                     | 1. If not used, leave it floating. 2. The INT pin sends an active low, 256-µs pulse to host to report charger device status and fault.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| NC        | B5              | Optional                   |                             |       |        |       | No connect                                                                                                                                                       | Float this pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|           |                 | optional                   |                             |       |        |       | Active low Charge Enable pin                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| /CE       | E3              | Required                   |                             |       |        |       |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|           |                 |                            |                             |       |        |       |                                                                                                                                                                  | 1. /CE pin must be pulled High or Low. 2. Battery charging is enabled when REG01[4] = 1 and CE pin = Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|           |                 |                            |                             |       |        |       | Battery voltage sensing pin for charge voltage regulation                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| BATSNS    | F3              | Optional                   |                             |       |        |       | In order to minimize the parasitic trace resistance during<br>charging, BATSNS pin is connected to the positive<br>terminal of battery pack as close as possible | If BATSNS pin is open, BATSNS_STAT bit is set to 1 and charger regulates the battery voltage through BAT<br>pin. If BATSNS is unused, this pin should be floating.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|           |                 |                            |                             |       |        |       | Temperature qualification voltage inputs for JEITA                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| TS        | D3              | Optional if<br>TS_IGNORE=1 | TS resistors and thermistor |       |        |       | Connect a negative temperature coefficient thermistors.<br>Recommend 103AT-2 thermistors.                                                                        | 1. If thermistor is not used, set TS pin voltage within normal range or set TS_IGNORE to 1 2. If thermistor is used, program temperature window with a resistor divider from REGN to TS to GND. Charge suspends when TS pin is out of range.                                                                                                                                                                                                                                                                                                                       |  |  |

|           |                 |                            |                             |       |        |       | BATFET enable/reset control input                                                                                                                                | 1.If not used, leave it floating. 2.The pin contains an internal pull-up to maintain default high logic. 3.When                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| /QON      | D4              | Optional                   |                             |       | Switch |       |                                                                                                                                                                  | BATTET is not in ship mode, a logic low of SHIPMODE duration turns on BATTET to exit ship mode. When the<br>BATTET is not in ship mode, a logic low of SHIPMODE duration turns on BATTET to exit ship mode. When the<br>BATTET is not in ship mode, a logic LOW of tQON_RST (minimum 8 s) duration resets SYS (system power) by<br>turning BATTET off for tBATTET_RST (minimum 250ms) and then re-enables BATTET to provide full system<br>power reset. The host chooses the BATTET reset function with VBUS unplugged or not through I2C bit<br>BATTET_RST_WVBUS. |  |  |

| VAC       | A5              |                            |                             |       |        |       | Charge input voltage sense                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |