## **BQ25756 Charge Controller IC**

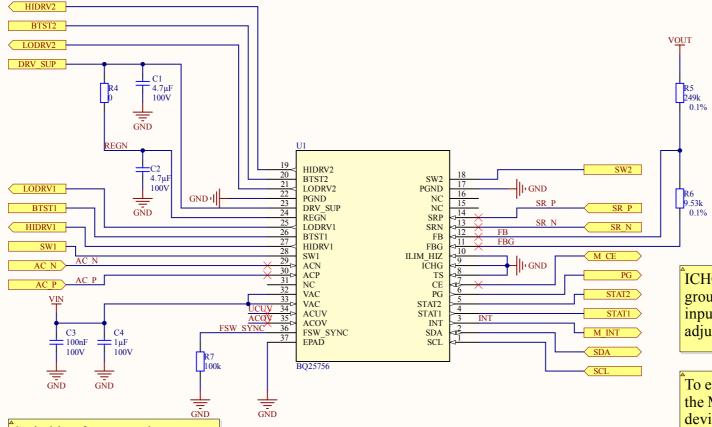

A 0R resistors connects DRV\_SUP to REGN. This is done to keep these traces separate so each can have their own 4.7 uF cap.

ICHG and ILIM\_HIZ are shorted to ground for disabling hardware limit for input and charge currents. These can be adjusted through the registers.

42.13V.

FB and FBG pins are used for setting up the charge voltage

voltage limit is set to 41.66V. To remedy this, we need to increase VFB REG to 1.548V, which sets the threshold to

For 14 cell charge (58.8V max), this resistor needs to be

be set to 1.56, which sets the threshold ot 58.96V

replaced with a 6.8kR 0.1% resistor. And the VFB REG should

limit. The charge voltage threshold is set by VFB\_REG, whose nominal value is 1.536V. With the current resistor choices, the

To enable charging, CE Pin is set low by the MCU and EN\_CHG is set to 1 in the device config. CE pin has a pull-up on the MCU side.

We need a 1uF and a 100nF cap for the VAC line. Datasheet only calls for 1uF but all reference designs have both. Switching frequency is set to 300kHz as it is in most of the reference designs. No need for 0.1% accuracy.

These resistor values are computed for 40V-50V operation but then adjusted for available capacitors in the library. We ended up with 41.39V - 51.37V as the window.

Since BMS is already responsible for temperature based protection, charger does not need this functionality. The NTC monitoring window can be disabled by clearing the EN\_TS register bit. In this case, the TS pin voltage is ignored, and the device always reports normal TS status. If EN\_TS is set to 0, TS pin can be floated or connected to PGND.