| UCC28070 Controller Setup Tool                                                      | 20/11/2018                                      |          |       |

|-------------------------------------------------------------------------------------|-------------------------------------------------|----------|-------|

| Preliminary                                                                         |                                                 |          |       |

| Notes:                                                                              |                                                 |          |       |

| This design tool is designed to work with the UCC28070 Appli                        | cation Note SLUA                                | 479      |       |

| This design tool is optimized for a Universal Input and can be                      |                                                 |          |       |

| used for designs were the input voltage is anywhere between                         |                                                 |          |       |

| 85V to 265V RMS.                                                                    |                                                 |          |       |

| Please enter design parameters into the                                             |                                                 | cells;   |       |

| Calculated results will be in                                                       | GRAY                                            |          |       |

| Design Parameters:                                                                  | Variable Names                                  |          | Units |

| Minimum RMS Input Voltage                                                           | V <sub>IN_MIN</sub>                             | 85       | V     |

| Maximum RMS Input Voltage                                                           | V <sub>IN_MAX</sub>                             | 265      | V     |

| Minimum Line Frequency                                                              | f <sub>LINE</sub>                               | 47       | Hz    |

| Maximum Line Frequency                                                              | _                                               | 63       | Hz    |

| Maximum Output Power                                                                | P <sub>out</sub>                                | 600      | W     |

| Full Load Efficiency (Must be less than 0.99)                                       | η                                               | 0,97     |       |

| Switching Frequency                                                                 | f <sub>S</sub>                                  | 6,50E+04 | Hz    |

| Output Voltage                                                                      | V <sub>OUT</sub>                                | 390      | V     |

| Maximum Duty Cycle                                                                  | D <sub>MAX</sub>                                | 0,97     |       |

| Soft Start Time                                                                     | t <sub>SS</sub>                                 | 0,50     | s     |

| Optional Frequency Dither Magnitude (Total ∆fs)                                     | f <sub>DM</sub>                                 | 3,00E+04 | Hz    |

| Optional Frequency Dither Rate                                                      | $f_{DR}$                                        | 1,00E+04 | Hz    |

| VCC                                                                                 | VCC                                             | 15       | V     |

| Component Selection, Trip Points and Calculated Values                              |                                                 |          |       |

| From the UCC28070 Design Example  Duty Cycle at the Peak the Peak of Low Line Input | D <sub>PLL</sub>                                | 0,69     |       |

|                                                                                     |                                                 |          | -     |

| Inductor Ripple Current Cancellation at the Peak of Low Line                        | K(D <sub>PLL</sub> )                            | 0,55     | -     |

| Inductor Ripple Current                                                             | $\Delta l_{L1}$                                 | 5,57     |       |

| Calculated Boost Inductors L <sub>1_MIN</sub> , L <sub>2_MIN</sub>                  | L <sub>1_MIN</sub> , L <sub>2_MIN</sub>         | 2,30E-04 | H     |

| Enter the Lowest Inductance Value of the Real Inductor                              | L <sub>1_MIN</sub> , L <sub>2_MIN</sub>         | 2,00E-04 | H     |

| Enter the Highest Inductance Value of the Real Inductor                             | L <sub>1_MAX</sub> , L <sub>2_MAX</sub>         | 3,50E-04 | Н     |

| Average Inductance Value                                                            | L <sub>1_AVG</sub> , L <sub>2_AVG</sub>         | 2,75E-04 | Н     |

| Inductor RMS Current                                                                | I <sub>L1_RMS</sub> , I <sub>L2_RMS</sub>       | 3,898    | Α     |

| Output Capacitance Calculated Based on Holdup Time                                  | C <sub>OUT</sub>                                | 3,84E-04 | F     |

| Output Capacitance Selected                                                         | C <sub>OUT</sub>                                | 4,70E-04 | F     |

| Output Ripple Voltage                                                               | $V_{RIPPLE}$                                    | 11,4     | V     |

| Low Frequency Output Capacitor RMS Current                                          | I <sub>COUT_LF</sub>                            | 1,122    | Α     |

| High Frequency Output Capacitor RMS Current                                         | I <sub>COUT_HF</sub>                            | 3,079    | А     |

| Peak Diode and FET Current                                                          | I <sub>PEAK</sub>                               | 9,516    | Α     |

| FET RMS Current (Q1 and Q2)                                                         | I <sub>DS</sub>                                 | 3,127    | Α     |

| Diode Average Current (D1 and D2)                                                   | I <sub>D</sub>                                  | 0,769    | Α     |

| Calculated Current Sense Transformer Turns Ratio                                    | N <sub>CT</sub> =N <sub>S</sub> /N <sub>P</sub> | 95       |       |

| Enter Current Sense Transformer Turns Ratio                                         | N <sub>CT</sub> =N <sub>S</sub> /N <sub>P</sub> | 100      |       |

| Minimum Magnetizing Inductance of the Current Sense Transfo    | orm L <sub>M</sub>                 | 2,07E-02 | Н   |

|----------------------------------------------------------------|------------------------------------|----------|-----|

| Select Current Sense Peak Voltage                              | Vs                                 | 3,70     | V   |

| Calculated Current Sense Resistor                              | R <sub>SA</sub> = R <sub>SB</sub>  | 35,0     | ohm |

| Select Standard Current Sense Resistor                         | R <sub>SA</sub> = R <sub>SB</sub>  | 33       | ohm |

| CalculatedReset Resistor                                       | R <sub>R</sub>                     | 1,E+03   | ohm |

| Select a Standard Value                                        | R <sub>R</sub>                     | 1,00E+03 | ohm |

| Calculated Maximum DR Reverse Voltage                          | $V_R$                              | 95       | V   |

| Current Sense Offset Desired                                   | $V_{OFF}$                          | 0,20     | V   |

| Program Offset Bias Current to be added to R <sub>S</sub>      | R <sub>OA</sub> =R <sub>OB</sub>   | 2,44E+03 | ohm |

| Select a Standard Value                                        | R <sub>OA</sub> =R <sub>OB</sub>   | 2,20E+03 | ohm |

| Program Current Sense PWM Ramp Resistor                        | R <sub>TA</sub> =R <sub>TB</sub>   | 3,00E+03 | ohm |

| Select Standard Values                                         | R <sub>TA</sub> =R <sub>TB</sub>   | 2,49E+03 | ohm |

| Program Current Sense PWM Ramp Timing Capacitor                | C <sub>TA</sub> =C <sub>TB</sub>   | 1,55E-07 | F   |

| Select Standard Values                                         | C <sub>TA</sub> =C <sub>TB</sub>   | 4,70E-08 | F   |

| Select High Side Resistor on Peak Current Limit Divider        | R <sub>PK1</sub>                   | 3,60E+03 | ohm |

| Calculated Low Side Resistor on Peak Current Limit Divider     | R <sub>PK2</sub>                   | 5,79E+03 | ohm |

| Select Low Side Resistor on Peak Current Limit Divider         | R <sub>PK2</sub>                   | 5,80E+03 | ohm |

| Calculated Timing Resistor                                     | R <sub>RT</sub>                    | 1,15E+05 | ohm |

| Select Timing Resistor                                         | R <sub>RT</sub>                    | 1,10E+05 | ohm |

| Calculated Programmable Duty Cycle Limit Resistor              | R <sub>DMX</sub>                   | 1,03E+05 | ohm |

| Select Programmable Duty Cycle Limit Resistor                  | R <sub>DMX</sub>                   | 1,00E+05 | ohm |

| Select High Side Resistor for VSENSE Voltage Divider           | R <sub>A</sub>                     | 3,00E+06 | ohm |

| Calculated Low Side Resistor on VSENSE voltage Divider         | R <sub>B</sub>                     | 2,33E+04 | ohm |

| Select Low Side Resistor on VSENSE voltage Divider             | R <sub>B</sub>                     | 2,32E+04 | ohm |

| Calculated Nominal Over Voltage Trip Point                     | V <sub>OVP</sub>                   | 414      | V   |

| Voltage Divider Gain                                           | Н                                  | 7,67E-03 |     |

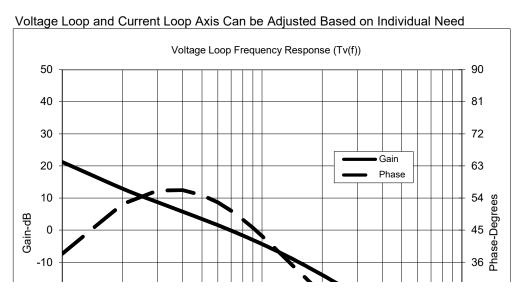

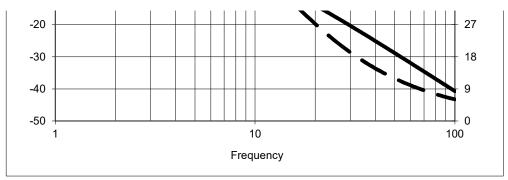

| Voltage Amplifier Output Impedance at double f <sub>LINE</sub> | Z <sub>O</sub>                     | 1,56E+04 | ohm |

| Calculated Pole Capacitance for the Voltage Loop               | C <sub>PV</sub>                    | 1,08E-07 | F   |

| Select a Standard Value                                        | C <sub>PV</sub>                    | 1,50E-07 | F   |

| Calculated Voltage Loop Crossover Frequency                    | f <sub>VC</sub>                    | 9,8      | Hz  |

| Calculated Voltage Loop Zero Compensation Resistor             | $R_{ZV}$                           | 1,08E+05 | ohm |

| Select a Standard Value                                        | $R_{zv}$                           | 1,00E+05 | ohm |

| Calculated Voltage Loop Zero Compensation Capacitor            | C <sub>ZV</sub>                    | 1,62E-06 | F   |

| Select a Standard Value                                        | C <sub>ZV</sub>                    | 1,50E-06 | F   |

| Calculated Current Synthesis Programmable Resistor             | R <sub>SYN</sub>                   | 8,14E+04 | ohm |

| Select a Standard Value                                        | R <sub>SYN</sub>                   | 8,20E+04 | ohm |

| Voltage Calculation for Selecting Multiplier Resistor          | V <sub>1</sub>                     | 70,029   | V   |

| Voltage Calculation for Selecting Multiplier Resistor          | V <sub>2</sub>                     | 2,267    | V   |

| Multiplier Resistor                                            | R <sub>IMO</sub>                   | 1,74E+04 | ohm |

| Select a Standard Value                                        | R <sub>IMO</sub>                   | 1,80E+04 | ohm |

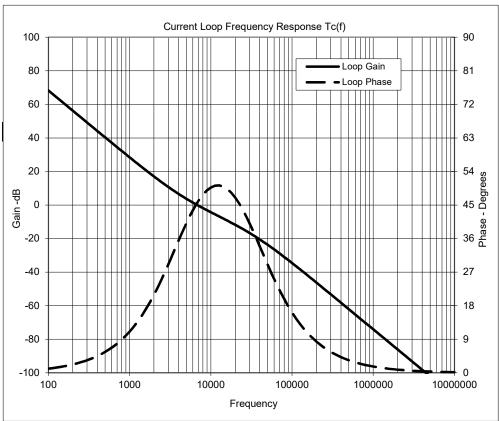

| Current Loop Power Stage Gain at Loop Crossover                | G <sub>PSC</sub>                   | 2,865    |     |

| Current Loop Zero Resistor                                     | R <sub>ZC1</sub> =R <sub>ZC2</sub> | 3,49E+03 | ohm |

| Select a Standard Value                                             | R <sub>ZC1</sub> =R <sub>ZC2</sub> | 3,60E+03   | ohm |

|---------------------------------------------------------------------|------------------------------------|------------|-----|

| Current Loop Zero Capacitor                                         | C <sub>ZC1</sub> =C <sub>ZC2</sub> | 7,01E-09   | F   |

| Select a Standard Value                                             | C <sub>ZC1</sub> =C <sub>ZC2</sub> | 1,00E-08   | F   |

| Current Loop Pole Capacitor                                         | C <sub>PC1</sub> =C <sub>PC2</sub> | 1,40E-09   | F   |

| Select a Standard Value                                             | C <sub>PC1</sub> =C <sub>PC2</sub> | 1,50E-09   | F   |

| Calculated Soft Start Capacitor (Be sure $C_{SS}$ > or = $C_{ZV}$ ) | C <sub>SS</sub>                    | 2,2222E-06 | F   |

| Select a Standard Value (Be sure $C_{SS} > or = C_{ZV}$ )           | C <sub>SS</sub>                    | 2,20E-06   | F   |

| Program Dither Magnitude Resistor                                   | R <sub>RDM</sub>                   | 3,13E+04   | ohm |

| Select a Standard Value                                             | R <sub>RDM</sub>                   | 3,16E+04   | ohm |

| Program Dither Rate Capacitor                                       | C <sub>CDR</sub>                   | 2,08E-10   | F   |

| Select a Standard Value                                             | C <sub>CDR</sub>                   | 2,20E-10   | F   |

| Disclaimer                                                          |                                    | •          | •   |

TI assumes no liability for applications assistance or customer product design. Customer is fully responsible for all design decisions and engineering with regard to its products, including decisions relating to application of TI products. By providing technical information, TI does not intend to offer or provide engineering services or advice concerning Customer's design. If Customer desires engineering services, the Customer should rely on its retained employees and consultants and/or procure engineering services from a licensed professional engineer (LPE).