## Hello Daniel,

There is no way to completely disable burst mode. However, to reduce to the minimum load possible just requires removing the resistor between the RVCC pin and the LL/SS pin.

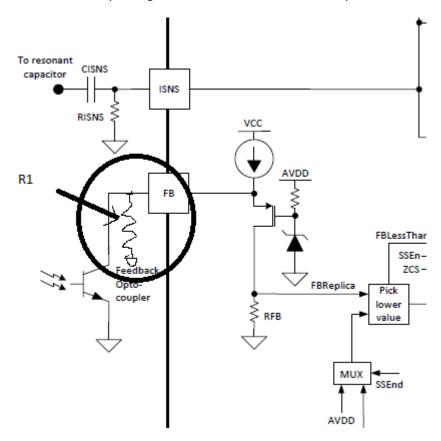

I thought about limiting the minimum maximum frequency. You might be able to do this by tying a resistor from the FB pin to ground. Please see the marked up schematic below.

The FB pin has an internal current source that is used to control the oscillator frequency of 85.1 uA roughly. When the Opto transistor is off the IFB current is going through the internal RFB resistor and the controller is operating at the maximum switching frequency is at the maximum of 1 Mhz to reduce the LLC gain.

| FEEDBACK PIN           |                                       |  |      |       |       |     |

|------------------------|---------------------------------------|--|------|-------|-------|-----|

| R <sub>FBIntemal</sub> | Internal pull down resistor value     |  | 90.7 | 101.5 | 112.3 | kΩ  |

| I <sub>FB</sub>        | FB internal current source            |  | 76.5 | 85.1  | 93.6  | μA  |

| f <sub>-3dB</sub>      | Feedback chain -3dB cut off frequency |  | 1    |       |       | MHz |

As current is drawn out of the FB pin the oscillator frequency will decrease based on how much FB current is drawn out of the pin. There is no information in the data sheet in regards to what exact ratio

of oscillator frequency is vs IFB current is. However, I will make an estimate/guesstimate based on slope the change of FB current (dIFB) vs estimated change in switching frequency (dfsw).

dfsw/IFb  $\approx$  1MHz-35kHz/85.1uA  $\approx$  11.3kHz/uA.

Based on the slope equation above we can estimate the desired current to pull out of the FB pin to get the designer minimum switching frequency (fmind).

IFB@fmin = fmind\*(uA/11.3 kHz)

If we wanted a minimum switching frequency of 50 Khz would require a IFB@fmin of 4.42uA. Please see the calculation below.

IFB@fmin  $\approx 50 \text{ kHz*(uA/11.3kHz)} = 4.42 \text{ uA}.$

I will make an estimate on the FB pin voltage when the FB pin is open with an estimate of a Vds voltage of the internal FET being 0.25V. I estimate the FB voltage would be roughly 9V.

$VFB \approx IFB * RFB internal + Vds \approx 85.1 uA * 101.5K + 0.35V = 9V$

Based on this estimate the resistor from the FB pin to ground would be 2.03M ohm.

R1 = VFB/IFB@fmin =  $9V/4.42uA \approx 2.03 \text{ M ohm}$

I would suggest using a potentiometer of 5 M ohm and dialing down slowly to the exact value. You need 100 turns or more to limit the maximum frequency.

I have not tried this but it should work.

Good luck on your design.

Regards,

Mike