Table 9. Characteristics of the SDA and SCL I/O stages n/a = not applicable.

| Symbol           | Parameter                                                         | Conditions                                                                          | Standard-mode      |                    | Fast-mode                            |                    | Fast-mode Plus                       |                    | Unit |

|------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|--------------------|--------------------------------------|--------------------|--------------------------------------|--------------------|------|

|                  |                                                                   |                                                                                     | Min                | Max                | Min                                  | Max                | Min                                  | Max                |      |

| V <sub>IL</sub>  | LOW-level input voltage[1]                                        |                                                                                     | -0.5               | 0.3V <sub>DD</sub> | -0.5                                 | 0.3V <sub>DD</sub> | -0.5                                 | 0.3V <sub>DD</sub> | ٧    |

| V <sub>IH</sub>  | HIGH-level input voltage[1]                                       |                                                                                     | 0.7V <sub>DD</sub> | [2]                | 0.7V <sub>DD</sub>                   | [2]                | 0.7V <sub>DD</sub> [1]               | [2]                | ٧    |

| V <sub>hys</sub> | hysteresis of Schmitt trigger inputs                              |                                                                                     | -                  | -                  | 0.05V <sub>DD</sub>                  | -                  | 0.05V <sub>DD</sub>                  | -                  | ٧    |

| V <sub>OL1</sub> | LOW-level output voltage 1                                        | (open-drain or open-collector)<br>at 3 mA sink current;<br>V <sub>DD</sub> > 2 V    | 0                  | 0.4                | 0                                    | 0.4                | 0                                    | 0.4                | V    |

| V <sub>OL2</sub> | LOW-level output voltage 2                                        | (open-drain or open-collector)<br>at 2 mA sink current[3];<br>V <sub>DD</sub> ≤ 2 V | -                  | -                  | 0                                    | 0.2V <sub>DD</sub> | 0                                    | 0.2V <sub>DD</sub> | V    |

| I <sub>OL</sub>  | LOW-level output current                                          | V <sub>OL</sub> = 0.4 V                                                             | 3                  | -                  | 3                                    | -                  | 20                                   | -                  | mA   |

|                  |                                                                   | V <sub>OL</sub> = 0.6 V[4]                                                          | -                  | -                  | 6                                    | -                  | -                                    | -                  | mA   |

| t <sub>of</sub>  | output fall time from V <sub>IHmin</sub> to V <sub>ILmax</sub>    |                                                                                     | -                  | 250 <sup>[5]</sup> | 20 ×<br>(V <sub>DD</sub> / 5.5 V)[6] | 250[5]             | 20 ×<br>(V <sub>DD</sub> / 5.5 V)[6] | 120[7]             | ns   |

| t <sub>SP</sub>  | pulse width of spikes that must be suppressed by the input filter |                                                                                     | -                  | -                  | 0                                    | 50[8]              | 0                                    | 50[8]              | ns   |

| lį               | input current each I/O pin                                        | 0.1V <sub>DD</sub> < V <sub>I</sub> < 0.9V <sub>DDmax</sub>                         | -10                | +10                | -10 <sup>[9]</sup>                   | +10 <sup>[9]</sup> | -10 <sup>[9]</sup>                   | +10 <sup>[9]</sup> | μΑ   |

| Ci               | capacitance for each I/O pin[10]                                  |                                                                                     | -                  | 10                 | -                                    | 10                 | -                                    | 10                 | pF   |

- [1] Some legacy Standard-mode devices had fixed input levels of V<sub>IL</sub> = 1.5 V and V<sub>IH</sub> = 3.0 V. Refer to component data sheets.

- [2] Maximum V<sub>IH</sub> = V<sub>DD(max)</sub> + 0.5 V or 5.5 V, which ever is lower. See component data sheets.

- [3] The same resistor value to drive 3 mA at 3.0 V V<sub>DD</sub> provides the same RC time constant when using <2 V V<sub>DD</sub> with a smaller current draw.

- [4] In order to drive full bus load at 400 kHz, 6 mA I<sub>OL</sub> is required at 0.6 V V<sub>OL</sub>. Parts not meeting this specification can still function, but not at 400 kHz and 400 pF.

- [5] The maximum t<sub>f</sub> for the SDA and SCL bus lines quoted in Table 10 (300 ns) is longer than the specified maximum t<sub>of</sub> for the output stages (250 ns). This allows series protection resistors (R<sub>s</sub>) to be connected between the SDA/SCL pins and the SDA/SCL bus lines as shown in Figure 45 without exceeding the maximum specified t<sub>f</sub>.

- [6] Necessary to be backwards compatible with Fast-mode.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] Input filters on the SDA and SCL inputs suppress noise spikes of less than 50 ns.

- [9] If V<sub>DD</sub> is switched off, I/O pins of Fast-mode and Fast-mode Plus devices must not obstruct the SDA and SCL lines.

- [10] Special purpose devices such as multiplexers and switches may exceed this capacitance because they connect multiple paths together.

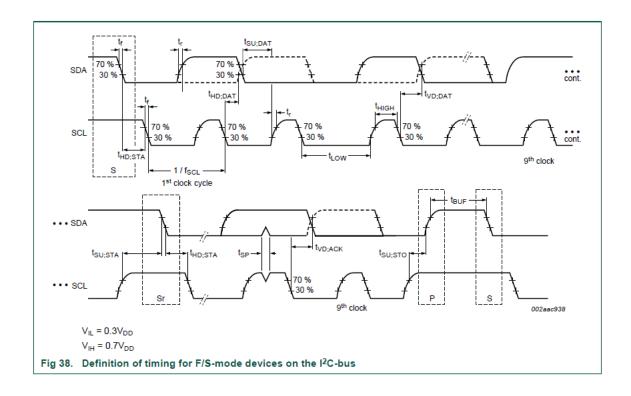

Table 10. Characteristics of the SDA and SCL bus lines for Standard, Fast, and Fast-mode Plus I<sup>2</sup>C-bus devices[1]

| Symbol              | Parameter                                         | Conditions                                             | Standard-mode      |         | Fast-mode                         |            | Fast-mode Plus                       |         | Unit |

|---------------------|---------------------------------------------------|--------------------------------------------------------|--------------------|---------|-----------------------------------|------------|--------------------------------------|---------|------|

|                     |                                                   |                                                        | Min                | Max     | Min                               | Max        | Min                                  | Max     | 1    |

| fscL                | SCL clock frequency                               |                                                        | 0                  | 100     | 0                                 | 400        | 0                                    | 1000    | kHz  |

| t <sub>HD;STA</sub> | hold time (repeated) START condition              | After this period, the first clock pulse is generated. | 4.0                | -       | 0.6                               | -          | 0.26                                 | -       | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                       |                                                        | 4.7                | -       | 1.3                               | -          | 0.5                                  | -       | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                      |                                                        | 4.0                | -       | 0.6                               | -          | 0.26                                 | -       | μs   |

| tsu;sta             | set-up time for a repeated START condition        |                                                        | 4.7                | -       | 0.6                               | -          | 0.26                                 | -       | μs   |

| t <sub>HD;DAT</sub> | data hold time[2]                                 | CBUS compatible masters (see Remark in Section 4.1)    | 5.0                | -       | -                                 | -          | -                                    | -       | μs   |

|                     |                                                   | I <sup>2</sup> C-bus devices                           | 0[3]               | _[4]    | 0[3]                              | <u>[4]</u> | 0                                    | -       | μs   |

| t <sub>SU;DAT</sub> | data set-up time                                  |                                                        | 250                | -       | 100 <sup>[5]</sup>                | -          | 50                                   | -       | ns   |

| tr                  | rise time of both SDA and SCL signals             |                                                        | -                  | 1000    | 20                                | 300        | -                                    | 120     | ns   |

| t <sub>f</sub>      | fall time of both SDA and SCL signals[3][6][7][8] |                                                        | -                  | 300     | 20 ×<br>(V <sub>DD</sub> / 5.5 V) | 300        | 20 ×<br>(V <sub>DD</sub> / 5.5 V)[9] | 120[8]  | ns   |

| t <sub>SU;STO</sub> | set-up time for STOP condition                    |                                                        | 4.0                | -       | 0.6                               | -          | 0.26                                 | -       | μs   |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition  |                                                        | 4.7                | -       | 1.3                               | -          | 0.5                                  | -       | μs   |

| Cb                  | capacitive load for each bus line[10]             |                                                        | -                  | 400     | -                                 | 400        | -                                    | 550     | pF   |

| t <sub>VD;DAT</sub> | data valid time[11]                               |                                                        | -                  | 3.45[4] | -                                 | 0.9[4]     | -                                    | 0.45[4] | μs   |

| t <sub>VD;ACK</sub> | data valid acknowledge time[12]                   |                                                        | -                  | 3.45[4] | -                                 | 0.9[4]     | -                                    | 0.45[4] | μs   |

| V <sub>nL</sub>     | noise margin at the LOW level                     | for each connected device (including hysteresis)       | 0.1V <sub>DD</sub> | -       | 0.1V <sub>DD</sub>                | -          | 0.1V <sub>DD</sub>                   | -       | ٧    |

| V <sub>nH</sub>     | noise margin at the HIGH level                    | for each connected device (including hysteresis)       | 0.2V <sub>DD</sub> | -       | 0.2V <sub>DD</sub>                | -          | 0.2V <sub>DD</sub>                   | -       | ٧    |

All values referred to V<sub>IH(min)</sub> (0.3V<sub>DD</sub>) and V<sub>IL(max)</sub> (0.7V<sub>DD</sub>) levels (see <u>Table 9</u>).

<sup>[2]</sup> the contract is the data hold time that is measured from the falling edge of SCL, applies to data in transmission and the acknowledge.

<sup>[3]</sup> A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>IH(min)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

<sup>[4]</sup> The maximum t<sub>HD:DAT</sub> could be 3.45 µs and 0.9 µs for Standard-mode and Fast-mode, but must be less than the maximum of t<sub>VD:DAT</sub> or t<sub>VD:DAT</sub> or t<sub>VD:DAT</sub> by a transition time. This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [5] A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU:DAT</sub> 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>r(max)</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

- [6] If mixed with Hs-mode devices, faster fall times according to Table 10 are allowed.

- [7] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [8] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [9] Necessary to be backwards compatible to Fast-mode.

- [10] The maximum bus capacitance allowable may vary from this value depending on the actual operating voltage and frequency of the application. <u>Section 7.2</u> discusses techniques for coping with higher bus capacitances.

- [11] tvD:DAT = time for data signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

- [12] t<sub>VD:ACK</sub> = time for Acknowledgement signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).