# **Intel Agilex® 7 Power Management User Guide**

# **Contents**

| 1. Intel Agilex® 7 Power Management Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.1. Power System Design Phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                    |

| 1.1.1. Choosing a Power Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| 1.1.2. Power Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| 1.1.3. Power Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| 1.1.4. Power Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| 1.2. Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

| • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

| 2. Intel Agilex 7 Power Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                    |

| 2.1. Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| 2.2. Power Estimation Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| 2.3. Intel FPGA Power and Thermal Calculator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8                    |

| 2.4. Power Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                    |

| 3. Intel Agilex 7 Power and I/O State Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| 3.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| 3.2. Power-Up Sequence Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                    |

| 3.2.1. Guidelines for I/O Pins in GPIO, HPS, and SDM Banks During Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.7                  |

| Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

| 3.3. Power-Down Sequence Requirements for Intel Agilex 7 Devices with E-Tile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| 3.4. Floating Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| 3.5. Power-On Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

| 3.5.1. Power Supplies Monitored by the POR Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| 4. Intel Agilex 7 Sensor Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                   |

| 4. Intel Agilex 7 Sensor Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                   |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18<br>19             |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18<br>19             |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18<br>19<br>19       |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18<br>19<br>20<br>21 |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18192021             |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1819202121           |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1819202121           |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 4.1. Voltage Sensor Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| 4.1. Voltage Sensor Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| 4.1.1 Voltage Sensor Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| 4.1. Voltage Sensor Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

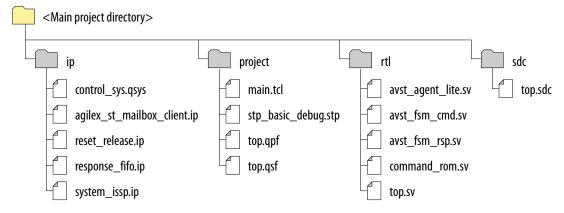

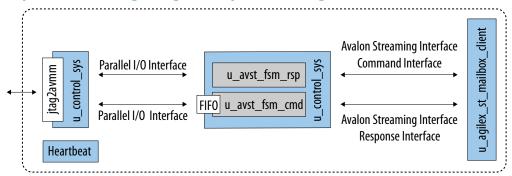

| 4.1. Voltage Sensor Transfer Function 4.2. Temperature Monitoring System 4.2.1. Local Temperature Sensor 4.2.2. Remote Temperature Sensing Diode 4.2.3. Temperature Sensor Locations 4.2.4. Retrieving Local Temperature Sensor Reading 4.2.5. Temperature Sensor Error Codes 4.3.1. Voltage Monitor Design Guidelines 4.3.2. Temperature Monitor Design Guidelines 4.3.3. Transceiver Tile Local Temperature Sensor Design Guidelines 4.3.4. Guidelines: Calibrate Temperature Sensing Chip Interfacing the Intel Agilex 7 Remote TSD 4.3.5. Guidelines: Reading the R-Tile Local Temperature Sensor 4.4.1. Directory Structure                                                                                                                                                                            |                      |

| 4.1. Voltage Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 4.1. Voltage Sensor Transfer Function 4.2. Temperature Monitoring System 4.2.1. Local Temperature Sensor 4.2.2. Remote Temperature Sensing Diode 4.2.3. Temperature Sensor Locations 4.2.4. Retrieving Local Temperature Sensor Reading 4.2.5. Temperature Sensor Error Codes 4.3. Sensors Design Considerations 4.3.1. Voltage Monitor Design Guidelines 4.3.2. Temperature Monitor Design Guidelines 4.3.3. Transceiver Tile Local Temperature Sensor Design Guidelines 4.3.4. Guidelines: Calibrate Temperature Sensing Chip Interfacing the Intel Agilex 7 Remote TSD 4.3.5. Guidelines: Reading the R-Tile Local Temperature Sensor 4.4. Temperature Reading Design Example 4.4.1. Directory Structure 4.4.2. Hardware and Software Requirements 4.4.3. Temperature Reading Design Example Description |                      |

| 4.1. Voltage Sensor Transfer Function.  4.2. Temperature Monitoring System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

| 4.1. Voltage Sensor Transfer Function 4.2. Temperature Monitoring System 4.2.1. Local Temperature Sensor 4.2.2. Remote Temperature Sensing Diode 4.2.3. Temperature Sensor Locations 4.2.4. Retrieving Local Temperature Sensor Reading 4.2.5. Temperature Sensor Error Codes 4.3. Sensors Design Considerations 4.3.1. Voltage Monitor Design Guidelines 4.3.2. Temperature Monitor Design Guidelines 4.3.3. Transceiver Tile Local Temperature Sensor Design Guidelines 4.3.4. Guidelines: Calibrate Temperature Sensing Chip Interfacing the Intel Agilex 7 Remote TSD 4.3.5. Guidelines: Reading the R-Tile Local Temperature Sensor 4.4. Temperature Reading Design Example 4.4.1. Directory Structure 4.4.2. Hardware and Software Requirements 4.4.3. Temperature Reading Design Example Description |                      |

| 5. Intel Agilex 7 Power Optimization Techniques and Features                    | 39 |

|---------------------------------------------------------------------------------|----|

| 5.1. SmartVID Standard Power Devices                                            | 39 |

| 5.1.1. SmartVID Feature Implementation in Intel Agilex 7 Devices                | 40 |

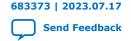

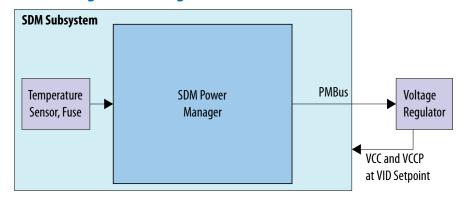

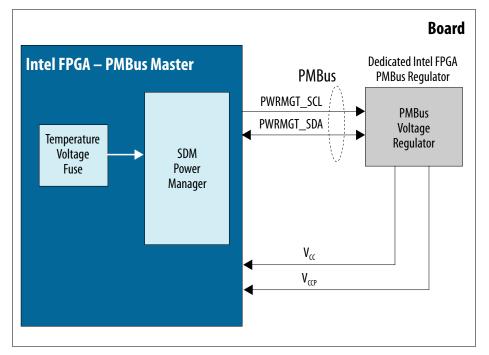

| 5.1.2. SDM Power Manager                                                        |    |

| 5.1.3. Temperature Compensation                                                 | 51 |

| 5.1.4. Intel Agilex 7 Power Management and VID Implementation Guide             | 51 |

| 5.2. DSP and M20K Power Gating                                                  | 55 |

| 5.3. Clock Gating                                                               | 56 |

| 5.4. Power Sense Line                                                           | 56 |

| 5.5. Power Optimization Techniques in the Intel Quartus Prime Software          | 57 |

| 6. Document Revision History for the Intel Agilex 7 Power Management User Guide | 58 |

# 1. Intel Agilex® 7 Power Management Overview

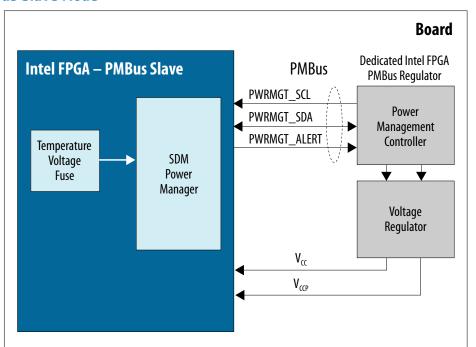

The Intel Agilex<sup>®</sup> 7 devices offer smart voltage identification (SmartVID) standard power devices in all speed grades. Fixed-voltage devices are also available, but only in –4 speed grade. All SmartVID standard power devices must be driven by the Power Management BUS (PMBus\*)-compliant voltage regulator, operating either in the PMBus master or PMBus slave mode.

This user guide describes the power-optimizing features of the Intel Agilex 7 devices, and the power-up and power-down sequencing requirements for the Intel Agilex 7 devices.

### 1.1. Power System Design Phases

Power system design is done in the following logical phases.

#### 1.1.1. Choosing a Power Tree

A power tree topology is chosen based on the requirements of your device.

The requirements of the power supply may not yet be known, but you can access the supply voltage and connection requirements from the *Intel Agilex 7 Device Family Pin Connection Guidelines: F-Series and I-Series*.

#### **Related Information**

Intel Agilex 7 Device Family Pin Connection Guidelines: F-Series and I-Series Provides more information about the supply voltage and connection guidelines of each pin for F-Series and I-Series FPGAs.

#### 1.1.2. Power Estimation

The amount of electrical power required by the various device power supplies is estimated using the Intel® FPGA Power and Thermal Calculator tool and the Power Analyzer tool.

As the design evolves to the final configuration, the quality and type of information available improve and the estimation becomes more accurate.

#### **Related Information**

Intel FPGA Power and Thermal Calculator User Guide

#### 1.1.3. Power Optimization

The device configuration can be optimized to reduce power.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

This step involves the Intel Quartus<sup>®</sup> Prime software power optimization wizard, the SmartVID feature (available in all Intel Agilex 7 devices except for –4F speed grade), system cooling decisions, and dynamic workload management strategies. This phase may occur several times during the evolution of the system and device design.

#### 1.1.4. Power Generation

Voltage regulator modules (VRMs) are selected based on the power tree and electrical power estimates. VRM selection is critical to producing high-quality power systems with the minimum number and cost of bypass elements.

### 1.2. Power Supplies

For more information about the supported power supplies and the nominal voltages, refer to the device data sheet.

#### **Related Information**

- Intel Agilex 7 FPGAs and SoCs Device Data Sheet: F-Series and I-Series

Provides more information about the supported power supplies and the

nominal voltages for F-Series and I-Series FPGAs.

- Intel Agilex 7 FPGAs and SoCs Device Data Sheet: M-Series

Provides more information about the supported power supplies and the

nominal voltages for M-Series FPGAs.

# 2. Intel Agilex 7 Power Basics

### 2.1. Power Consumption

The total power consumption of the Intel Agilex 7 device consists of the following components:

- Static power—the power that the configured device consumes when powered up but no user clocks are operating, excluding DC bias power of analog blocks, such as I/O and transceiver analog circuitry.

- Dynamic power—the additional power consumption of the device due to signal activity or toggling. Dynamic power is dependent on the operating frequency of your design, applied voltage, and load capacitance, which depends on design connectivity.

- Standby power—the component of active power that is independent of signal activity or toggling. Standby power includes, but is not limited to, I/O and transceiver DC bias power.

Intel Agilex 7 devices minimize static and dynamic power using advanced process optimizations. These optimizations allow Intel Agilex 7 designs to meet specific performance requirements with the lowest possible power.

#### 2.2. Power Estimation Basics

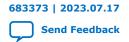

The Intel power analysis features, including the Intel FPGA Power and Thermal Calculator tool and the Intel Quartus Prime software Power Analyzer, give you the ability to estimate power consumption from early design concept through design implementation, as shown in the following figure.

As you provide more details about your design characteristics, estimation accuracy is improved. Intel recommends that you switch from the Intel FPGA Power and Thermal Calculator to the Power Analyzer in the Intel Quartus Prime software once your design is available. The Power Analyzer produces more accurate results because it has more detailed information about your design, including routing and configuration information about all the resources in your design.

The accuracy of the power model is determined on a per-power-rail basis for both the Power Analyzer and the Intel FPGA Power and Thermal Calculator. For most designs, the Power Analyzer and the Intel FPGA Power and Thermal Calculator have the following accuracies, with final power models:

- Power Analyzer—within 10% of silicon for the majority of power rails and the highest power rails, assuming accurate inputs and toggle rates.

- Intel FPGA Power and Thermal Calculator—within 15% of silicon for the majority of power rails and the highest power rails, assuming accurate inputs and toggle rates. Recommended margins are shown in the **Report** tab, only after device power model status is final.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

Figure 1. Power Analysis from Design Concept Through Design Implementation

**Design Stages**

Table 1. Comparison of Intel FPGA Power and Thermal Calculator and Intel Quartus Prime Power Analyzer Capabilities

| Characteristic        | Characteristic Intel FPGA Power and Thermal Calculator                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| When to use           | Any time  Note: For post-fit power analysis, you get better results with the Intel Quartus Prime Power Analyzer.                                                                                                                                          | Post-fit                                                                                                                                                                                                                                                                          |

| Software requirements | The Intel Quartus Prime software  The Intel FPGA Power and Thermal Calculator  Available in a standalone version which offers the same features as the Intel FPGA Power and Thermal Calculator version integrated within the Intel Quartus Prime software | The Intel Quartus Prime software                                                                                                                                                                                                                                                  |

| Accuracy              | Medium                                                                                                                                                                                                                                                    | Medium to very high                                                                                                                                                                                                                                                               |

| Data inputs           | <ul> <li>Resource usage estimates</li> <li>Clock requirements</li> <li>Environmental conditions</li> <li>Toggle rates</li> </ul>                                                                                                                          | Post-fit design     Clock requirements     Signal activity defaults     Environmental conditions     Register transfer level (RTL) simulation results (optional)     Post-fit simulation results (optional)     Signal activities per node or entity (optional)                   |

| Data outputs          | Total thermal power dissipation Thermal static power Thermal dynamic power Off-chip power dissipation Current drawn from voltage supplies                                                                                                                 | Total thermal power dissipation Thermal static power Thermal dynamic power Thermal I/O power Thermal power by design hierarchy Thermal power by block type Thermal power dissipation by clock domain Off-chip (non-thermal) power dissipation Current drawn from voltage supplies |

#### 2.3. Intel FPGA Power and Thermal Calculator

The Intel FPGA Power and Thermal Calculator results for Intel Agilex 7 devices are based on preliminary simulated data.

The Intel FPGA Power and Thermal Calculator for Intel Agilex 7 devices provides a current and power estimate based on various conditions such as room temperature and nominal voltage.

The Intel FPGA Power and Thermal Calculator calculations are estimates only and shall not be construed as a specification or a guarantee of any kind. The actual currents must be verified during device operation, as this measurement is sensitive to the design implemented in the device and the environmental operating conditions.

#### **Related Information**

- Intel FPGA Power and Thermal Calculator User Guide

- Intel FPGA Power and Thermal Calculator Standalone

Provides standalone Intel FPGA Power and Thermal Calculator tool. This standalone version is available for download from the Intel Download Center for FPGA page under the Additional Software tab.

### 2.4. Power Analyzer

The Intel Quartus Prime Power Analyzer allows you to estimate power consumption for a post-fit design.

To estimate power consumption before you compile the design, use the Intel FPGA Power and Thermal Calculator.

#### **Related Information**

Intel Quartus Prime Pro Edition User Guide: Power Analysis and Optimization

# 3. Intel Agilex 7 Power and I/O State Sequencing

#### 3.1. Overview

The Intel Agilex 7 devices require a specific power sequence.

This section describes several power management options and discusses proper I/O management during device power up and power down. Design your power supply solution to properly control the complete power sequence. The requirements in this section must be followed to prevent unpredictable current draw to the FPGA device, which can potentially impact the I/O functionality.

**Table 2.** Power Rails Status for Intel Agilex 7 Devices

| Tile   | Status      |

|--------|-------------|

| E-Tile | Final       |

| P-Tile | Final       |

| F-Tile | Preliminary |

| R-Tile | Preliminary |

The following descriptors designate the status level currently applicable to the relevant variant:

- Preliminary: Information in this document is **subject to change**. Intended for pre-production development, for production designs use with caution.

- Final: Information in this document is intended for use in production design.

### 3.2. Power-Up Sequence Requirements

The power rails in the Intel Agilex 7 devices are divided into three groups.

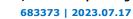

The following figure shows the voltage groups of the Intel Agilex 7 F-Series and I-Series devices and their required power-up sequence.

Figure 2. Power-Up Sequence for the Intel Agilex 7 F-Series and I-Series Devices

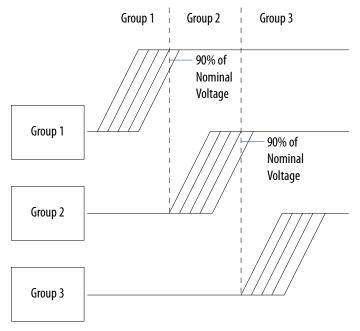

The following figure shows the voltage groups of the Intel Agilex 7 M-Series devices and their required power-up sequence.

Figure 3. Power-Up Sequence for the Intel Agilex 7 M-Series Devices

Note:

$V_{CCBAT}$  is not in any of the groups below.  $V_{CCBAT}$  does not have any sequence requirements.  $V_{CCBAT}$  holds the content of the security keys.

For more information about the  $V_{CCBAT}$  connection guidelines and power supply sharing guidelines, refer to the *Intel Agilex 7 Device Family Pin Connection Guidelines: F-Series and I-Series*.

Table 3. Voltage Rails Group for the Intel Agilex 7 F-Series and I-Series Devices

| Power Group | FPGA Core and                                                                                             | Additional Voltage Rails                                                    |                                                |                                                                      |                                                  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------|--|--|

|             | Hard Processor<br>System (HPS)                                                                            | E-Tile                                                                      | P-Tile                                         | F-Tile                                                               | R-Tile                                           |  |  |

| Group 1     | VCC VCCP VCCH VCCL_SDM VCCH_SDM VCCPLLDIG_SDM VCCPLLDIG_SDM VCCL_HPS VCCPLLDIG_HPS                        | V <sub>CCRT_GXE</sub> V <sub>CC_HSSI_GXE</sub> (1) V <sub>CCRTPLL_GXE</sub> | VCC_HSSI_GXP VCCRT_GXP VCCFUSE_GXP             | VCC_HSSI_GXF VCCERT_FGT_GXF VCCERT1_FHT_GXF VCCERT2_FHT_GXF          | VCC_HSSI_GXR VCCE_PLL_GXR VCCE_DTS_GXR VCCRT_GXR |  |  |

| Group 2     | VCCPT<br>VCCPLL_SDM<br>VCCADC<br>VCCPLL_HPS                                                               | V <sub>CCH_GXE</sub> (1)<br>V <sub>CCCLK_GXE</sub> (1)                      | V <sub>CCH_GXP</sub><br>V <sub>CCCLK_GXP</sub> | VCCFUSECORE_GXF VCCFUSEWR_GXF VCCCLK_GXF VCCH_FGT_GXF VCCEHT_FHT_GXF | VCCED_GXR VCCCLK_GXR VCCH_FUSE_GXR VCCH_GXR      |  |  |

| Group 3     | VCCA_PLL <sup>(2)</sup> VCCRCORE <sup>(2)</sup> VCCIO_PIO_SDM VCCIO_PIO VCCFUSEWR_SDM VCCIO_SDM VCCIO_HPS | _                                                                           | _                                              | _                                                                    |                                                  |  |  |

All power rails in Group 1 must ramp up (in any order) to a minimum of 90% of their respective nominal voltage before the power rails from Group 2 can start ramping up. The power rails within Group 2 can ramp up in any order after the last power rail in Group 1 ramps to the minimum threshold of 90% of its nominal voltage. All power rails in Group 2 must ramp to a minimum threshold of 90% of their nominal value before the Group 3 power rails can start ramping up. The power rails within Group 3 can ramp up in any order after the last power rail in Group 2 ramps up to a minimum threshold of 90% of their full value. For more information, refer to the *Intel Agilex 7 Device Family Pin Connection Guidelines: F-Series and I-Series*.

For Intel Agilex 7 devices, there is no power-down sequence requirement, except for Intel Agilex 7 devices with E-tile.

<sup>(2)</sup> For Intel Agilex 7 production devices and ES (except 2486A package) devices, VCCA\_PLL and VCCRCORE are part of power Group 3. For Intel Agilex 7 ES (2486A package) devices, VCCA\_PLL and VCCRCORE are part of power Group 2.

<sup>(1)</sup> For Intel Agilex 7 devices with E-tile, these voltage rails must follow the power-down sequence. For more information, refer to the *Power-Down Sequence for the Intel Agilex 7 Devices with E-Tile* figure.

For Intel Agilex 7 devices without E-tile, Intel recommends that you reverse the power-up sequence when you power down your device to ensure lowest current draw on each voltage supply.

Table 4. Voltage Rails Group for the Intel Agilex 7 M-Series Devices

| Group 1                                                                                                 | Group 2                  | Group 3a                                                                                  | Group 3b                                  |

|---------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|

| VCC VCCP VCCL_SDM VCCH_SDM VCCH VCCH VCCPLLDIG_SDM VCCL_HPS VCCPLLDIG_HPS VCCLLNOC VCCPLLDIG_NOC        | F-Tile: • VCCEHT_FHT_GXF | VCCFUSEWR_SDM VCCIO_SDM VCCIO_HPS VCCPT VCCPLL_NOC VCCIO_NOC VCCPLL_SDM VCCADC VCCPLL_HPS | VCCIO_PIO VCCN_PIO_SDM VCCRCORE VCCIO_UIB |

| F-Tile:  VCC_HSSI_GXF  VCCFUSECORE_GXF  VCCERT_FGT_GXF  VCCERT1_FHT_GXF  VCCERT2_FHT_GXF  VCCFUSEWR_GXF |                          | F-Tile: • VCCCLK_GXF • VCCH_FGT_GXF                                                       |                                           |

| R-Tile:  VCC_HSSI_GXR  VCCE_PLL_GXR  VCCE_DTS_GXR  VCCRT_GXR  VCCED_GXR  VCCCLK_GXR  VCCCH_FUSE_GXR     |                          | R-Tile: • VCCH_GXR                                                                        |                                           |

| HBM2E: • VCCM_PUMP_HBM                                                                                  |                          |                                                                                           |                                           |

All power rails in Group 1 must ramp up (in any order) to a minimum of 90% of their respective nominal voltage before the power rails from Group 2 can start ramping up. The power rails within Group 2 can ramp up in any order after the last power rail in Group 1 ramps to the minimum threshold of 90% of its nominal voltage. All power rails in Group 2 must ramp to a minimum threshold of 90% of their nominal value before the Group 3a power rails can start ramping up. All power rails in Group 3a must ramp to a minimum threshold of 90% of their nominal value before the Group 3b power rails can start ramping up. The power rails within Group 3b can ramp up in any order after the last power rail in Group 3a ramps up to a minimum threshold of 90% of their full value. For more information, refer to the *Pin Connection Guidelines*.

All power rails must ramp up and ramp down monotonically. The power-up sequence must meet the POR delay time. For the POR specifications of the Intel Agilex 7 devices, refer to the POR Specifications section in the Intel Agilex 7 FPGAs and SoCs Device Data Sheet: F-Series and I-Series.

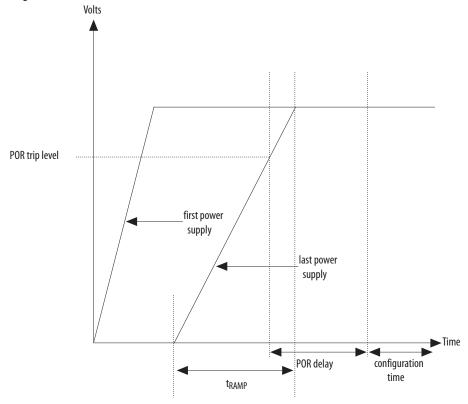

For configuration via protocol (CvP), the total  $t_{RAMP}$  must be less than 10 ms from the first power supply ramp-up to the last power supply ramp-up. For the  $t_{RAMP}$  specifications, refer to the *Recommended Operating Conditions* section in the *Intel Agilex 7 FPGAs and SoCs Device Data Sheet: F-Series and I-Series*.

#### **Related Information**

- Intel Agilex 7 Device Family Pin Connection Guidelines: F-Series and I-Series

Provides more information about the power supply sharing guidelines for F Series and I-Series FPGAs.

- Intel Agilex 7 FPGAs and SoCs Device Data Sheet: F-Series and I-Series

Provides more information about the t<sub>RAMP</sub> and POR specifications for F-Series

and I-Series FPGAs.

- Intel Agilex 7 FPGAs and SoCs Device Data Sheet: M-Series

Provides more information about the t<sub>RAMP</sub> and POR specifications for M-Series FPGAs.

# 3.2.1. Guidelines for I/O Pins in GPIO, HPS, and SDM Banks During Power Sequencing

Intel Agilex 7 devices do not support hot-socketing and require a specific power sequence. Design your power supply solution to properly control the complete power sequence.

Adhere to the following guidelines to prevent unnecessary current draw on the I/O pins located in the GPIO, HPS, and SDM banks. These guidelines are applicable for unpowered, power up to POR, POR delay, POR delay to configuration, configuration, initialization, user mode, and power down device states.

- The I/O pins in these banks can be in one the following states:

- GPIO banks—tri-stated, driven to ground, or driven to the  $V_{CCIO\ PIO}$  level.

- HPS banks—tri-stated, driven to ground, or driven to the V<sub>CCIO HPS</sub> level.

- SDM banks—tri-stated, driven to ground, or driven to the V<sub>CCIO SDM</sub> level.

- While the Intel Agilex 7 device is powering up or down:

- The input signals of an I/O pin at all times must not exceed the I/O buffer power supply rail of the bank where the I/O pin resides.

- If you use a pin in a GPIO bank with 1.5 V  $V_{CCIO\_PIO}$  (for Intel Agilex 7 F-Series and I-Series) or 1.3 V  $V_{CCIO\_PIO}$  (for Intel Agilex 7 M-Series), the pin voltage must not exceed the  $V_{CCIO\_PIO}$  rail or 1.2 V, whichever is lower.

- While the Intel Agilex 7 device is powering up, powering down, or not turned on, the GPIO, SDM, and HPS pins can tolerate a maximum of 10 mA per pin and a total of 100 mA per I/O bank.

- After the Intel Agilex 7 device fully powers up, the voltage levels for the GPIO, SDM, and HPS pins must not exceed the DC input voltage  $(V_{\rm I})$  value.

Table 5. Guideline Examples for the Intel Agilex 7 F-Series and I-Series

| Condition                                                                                          | Guideline                                                                                                           |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| The VCCIO_SDM pin ramps up and at period $X$ , the $V_{\text{CCIO}\_\text{SDM}}$ voltage is 0.9 V. | At period X, keep the signals driven by the device connected to the SDM I/O pin at a voltage of 0.9 V or lower.     |

| The VCCIO_PIO pin ramps up and at period $X$ , the $V_{\text{CCIO}\_PIO}$ voltage is 1.1 V.        | At period $X$ , keep the signals driven by the device connected to the GPIO I/O pin at a voltage of 1.1 V or lower. |

| The 1.5 V VCCIO_PIO pin ramps up and the voltage continues to rise pass the 1.2 V level.           | Keep the GPIO I/O pin voltage at 1.2 V or lower until the Intel Agilex 7 device fully powers up.                    |

**Table 6.** Guideline Examples for the Intel Agilex 7 M-Series

| Condition                                                                                          | Guideline                                                                                                           |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| The VCCIO_SDM pin ramps up and at period $X$ , the $V_{\text{CCIO}\_\text{SDM}}$ voltage is 1.8 V. | At period $X$ , keep the signals driven by the device connected to the SDM I/O pin at a voltage of 1.8 V or lower.  |

| The VCCIO_PIO pin ramps up and at period $X$ , the $V_{\text{CCIO}\_PIO}$ voltage is 1.1 V.        | At period $X$ , keep the signals driven by the device connected to the GPIO I/O pin at a voltage of 1.1 V or lower. |

| The 1.3 V VCCIO_PIO pin ramps up and the voltage continues to rise pass the 1.2 V level.           | Keep the GPIO I/O pin voltage at 1.2 V or lower until the F-Series and I-Series device fully powers up.             |

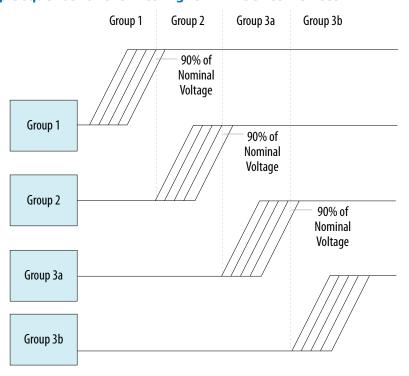

# 3.3. Power-Down Sequence Requirements for Intel Agilex 7 Devices with E-Tile

Intel Agilex 7 devices with E-tile must follow certain requirements during a power-down sequence. The power-down sequence can be a controlled power-down event via an on or off switch or an uncontrolled event such as a power supply collapse. In either situation, you must follow a specific power-down sequence.

Figure 4. Power-Down Sequence for Intel Agilex 7 Devices with E-Tile

- Power down all power rails fully within 100 ms.

- Before Group 1 (VCC\_HSSI\_GXE) supply power down, power down Group 2 (VCCH\_GXE & VCCCLK\_GXE) supplies within 10% of the nominal voltage.

For Intel Agilex 7 devices with E-tile, you can combine and ramp down other voltage rails that share the same voltage level and the same voltage regulator.

## 3.4. Floating Voltage

When you power up the device, you may observe a a floating voltage may be observed on the power rails as listed in the following table.

Table 7. Power Rails Floating Voltage for the Intel Agilex 7 F-Series and I-Series

| Power Rail          | Approximate Floating Voltage Value (V) |

|---------------------|----------------------------------------|

| VCCPT               | 0.366                                  |

| VCCIO_PIO           | 0.340                                  |

| VCCA_PLL            | 0.095                                  |

| VCCRCORE            | 0.500                                  |

| VCCFUSEWR_SDM       | 0.229-1.360                            |

| VCCCLK_GXE[R1]      | 0.460                                  |

| VCCRT_GXP[L1,L3]    | 0.547                                  |

| VCCEHT_FHT_GXF[L,R] | 0.091                                  |

| VCCED_GXR[L,R]      | 0.035                                  |

| VCCL_HPS            | 0.096                                  |

This is an expected behavior and causes neither functional nor reliability issue to the device, provided you follow the power-up or power-down sequence. The observed behavior can be avoided if the power supplies are not left to float before the device ramp up and after the device ramp down.

#### 3.5. Power-On Reset

The power-on reset (POR) circuitry keeps the Intel Agilex 7 device in the reset state until the power supply outputs are within the recommended operating range.

A POR event occurs when you power up the Intel Agilex 7 device until all power supplies monitored by the POR circuitry reach the recommended operating range within the maximum power supply ramp time,  $t_{RAMP}$ . If  $t_{RAMP}$  is not met, the Intel Agilex 7 device I/O pins remain tri-stated, and programming registers remain reset, which may cause device configuration to fail.

#### Figure 5. Relationship Between t<sub>RAMP</sub> and POR Delay

The boot ROM initialization sequence is part of the POR delay. For  $t_{RAMP}$  and POR delay specifications, refer to the Intel Agilex 7 FPGAs and SoCs Device Data Sheet: F-Series and I-Series .

The Intel Agilex 7 POR circuitry uses individual detection circuitry to monitor each of the configuration-related power supplies independently. The POR circuitry is gated by the outputs of all the individual detectors.

POR delay is the time from when the POR trips out to the final reset signal. For POR trip level, you can use the minimum value of the last power supply as a reference.

The Intel Agilex 7 device is held in the POR state until all power supplies have passed their trigger point. After power supplies have passed the trigger point, the Secure Device Manager (SDM) waits for a configurable delay time and then starts device configuration.

#### **Related Information**

- Intel Agilex 7 FPGAs and SoCs Device Data Sheet: F-Series and I-Series

Provides more information about the t<sub>RAMP</sub> and POR specifications for F-Series

and I-Series FPGAs.

- Intel Agilex 7 FPGAs and SoCs Device Data Sheet: M-Series

Provides more information about the t<sub>RAMP</sub> and POR specifications for for M-Series FPGAs.

#### 3.5.1. Power Supplies Monitored by the POR Circuitry

The following power supplies are monitored by the Intel Agilex 7 POR circuitry:

#### 3. Intel Agilex 7 Power and I/O State Sequencing

683373 | 2023.07.17

- V<sub>CCL\_SDM</sub>

- V<sub>CCPT</sub>

- $\bullet$   $V_{CCIO\_SDM}$

- V<sub>CCADC</sub>

- V<sub>CC</sub>

- V<sub>CCH\_SDM</sub>

- V<sub>CCL\_HPS</sub>

- V<sub>CCIO\_PIO\_SDM</sub>

- V<sub>CCRCORE</sub>

The  $V_{CCL\_SDM}$ ,  $V_{CCPT}$ , and  $V_{CCIO\_SDM}$  gate the SDM POR.

# 4. Intel Agilex 7 Sensor Monitoring System

Intel Agilex 7 devices provide you with on-chip voltage and temperature sensors. You can use these sensors to monitor external voltages and on-chip operation conditions such as the internal power rail and on-chip junction temperature.

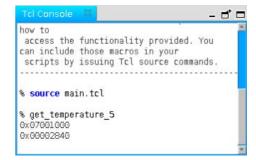

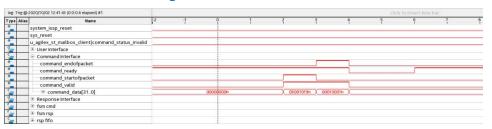

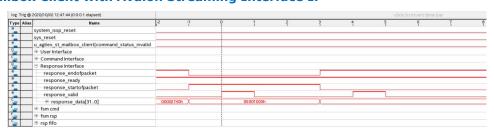

The Intel Agilex 7 sensor monitoring system stores sampled data in the secure device manager (SDM). You can read the voltage and temperature values in the SDM by using the Mailbox Client Intel FPGA IP or the Mailbox Client with Avalon® Streaming Interface Intel FPGA IP.

#### **Related Information**

- Operation Commands, Mailbox Client Intel FPGA IP User Guide

Provides information about the GET\_VOLTAGE and GET\_TEMPERATURE

commands of the Mailbox Client IP.

- Mailbox Client with Avalon Streaming Interface Intel FPGA IP User Guide

Provides information about reading the voltage and temperature values using

the Mailbox Client with Avalon Streaming Interface IP.

### 4.1. Voltage Monitoring System

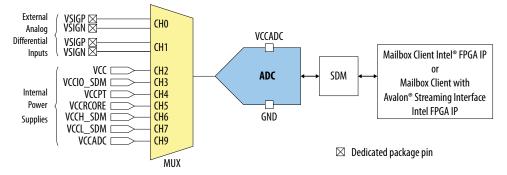

The Intel Agilex 7 voltage monitoring system uses a built-in 7-bit analog to digital converter (ADC). The ADC can sample up to one kilo samples per second (KSPS).

Figure 6. Intel Agilex 7 Voltage Sensor

The voltage sensor has the following capabilities:

- Monitor external voltages up to 1.10 V through two pairs of differential input pins.

- Monitor internal power supplies. For internal high-voltage rails in channels 3, 4, 5, and 9, a voltage divider function divides the input voltage by half and feeds the voltage to the ADC. The SDM then doubles the ADC reading to get the actual voltage.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### 4.1.1. Voltage Sensor Transfer Function

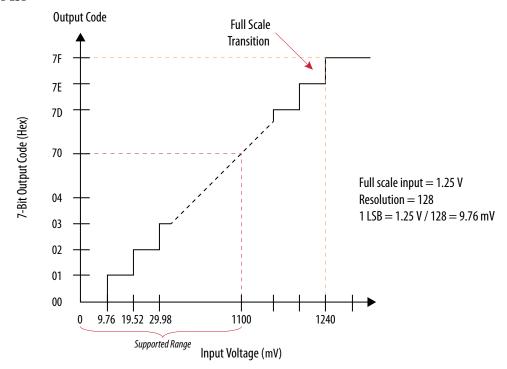

The Intel Agilex 7 voltage sensor supports the ADC's unipolar operation mode.

#### Figure 7. Intel Agilex 7 ADC 7-Bit Unipolar Transfer Function

The analog input scale has full scale code from 00h to 7Fh. The measurement can only display up to full scale – 1 LSB

# 4.2. Temperature Monitoring System

The Intel Agilex 7 temperature monitoring system allows you to measure the on-chip temperature ( $T_{JUNCTION}$ ) using local temperature sensors or remote temperature sensing diodes (TSDs).

**Table 8.** Overview of the Local and Remote Temperature Sensors

| Feature              | Local Temperature Sensor                                                                                     | Remote TSD                                                    |

|----------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Temperature sensing  | Uses the built-in ADC to sample the on-chip temperature.                                                     | Interfaces the TSD with an external temperature sensing chip. |

| Readout access       | From the SDM mailbox through the Mailbox<br>Client or Mailbox Client with Avalon Streaming<br>Interface IPs. | From the external temperature sensing chip.                   |

| Operation capability | While the Intel Agilex 7 devices are in user mode.                                                           | While the Intel Agilex 7 devices are powered on or off.       |

| User calibration     | Not required.                                                                                                | Required. Refer to the related information.                   |

#### **Related Information**

Guidelines: Calibrate Temperature Sensing Chip Interfacing the Intel Agilex 7 Remote TSD on page 29

#### 4.2.1. Local Temperature Sensor

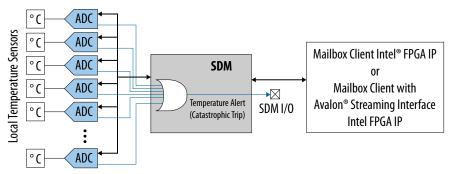

The Intel Agilex 7 local temperature sensors use built-in 11-bit ADCs and provide temperature readouts through the SDM mailbox.

Each temperature sensor location contains up to two local TSDs in the core fabric, or up to six TSDs in transceiver tiles<sup>(3)</sup>.

#### Figure 8. Intel Agilex 7 FPGAs Local Temperature Sensor

This figure is a block diagram of the local temperature sensors. For the physical locations of the sensors, refer to the related information.

Intel Agilex 7 devices provide up to 11 local temperature sensor locations for monitoring on-chip temperature.

- Up to five temperature sensor locations in the core fabric—with a total of up to nine local TSDs among them—allow you to monitor the temperatures around the core fabric.

- Up to six local temperature sensor locations, one in each transceiver tile, allow you to monitor the temperature of the transceiver tiles. The number of transceiver tiles varies among Intel Agilex 7 devices and package options.

- For M-Series FPGAs, up to two temperature sensor locations, one in each HBM2E tile, allow you to monitor the temperature of the HBM2E tiles. The number of HBM2E tiles varies among the M-Series FPGAs.

Refer to the related information for more details about the locations and availability of the temperature sensors in different Intel Agilex 7 series, densities, and packages.

<sup>(3)</sup> The number of local TSDs in each location for R-Tile, F-Tile, and E-Tile transceivers are six, five, and four, respectively. Other types of transceiver tiles have only one local TSD per location. For details about availability of the temperature sensors, refer to the related information.

#### **Catastrophic Trip Signal**

The catastrophic trip signal, nCATTRIP, is an optional signal that you can assign to any unused SDM\_IO pin. If enabled, the nCATTRIP signal asserts and stays high. When the core temperature reaches  $120^{\circ}$  C and higher, the nCATTRIP signal drives low—you must immediately power down the FPGA to avoid permanent damage to the device. The nCATTRIP signal is only valid after the device enters user mode.

Note: The catastrophic signal is not supported for the local TSD in the SDM location.

#### **Related Information**

- Temperature Sensor Locations on page 21

- SDM Pin Mapping, Intel Agilex 7 Configuration User Guide

Provides more details about enabling and assigning the nCATTRIP signal to an SDM IO pin.

#### 4.2.2. Remote Temperature Sensing Diode

The remote TSD interface allows you to monitor the temperature of the core fabric and transceiver tiles using an external temperature sensor.

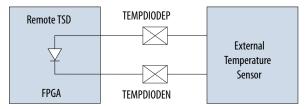

#### Figure 9. External Temperature Sensor Connection to the Remote TSD

The remote TSD requires a two-pins connection.

- In the device pin-out files, the remote TSD pins are marked as TEMPDIODEP and TEMPDIODEN.

- For the remote TSD characteristics, refer to the relevant section in the device datasheet.

#### **Related Information**

Temperature Sensor Locations on page 21

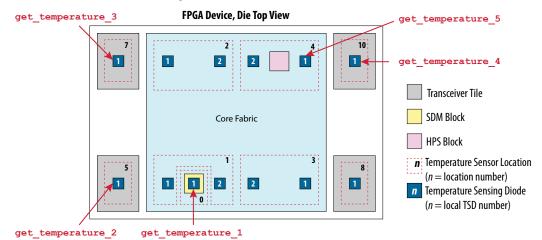

#### 4.2.3. Temperature Sensor Locations

The Intel Agilex 7 local and remote TSDs are located in the core fabric and tiles. There are several local temperature sensor locations within the core fabric and one location in each transceiver or HBM2E tile.

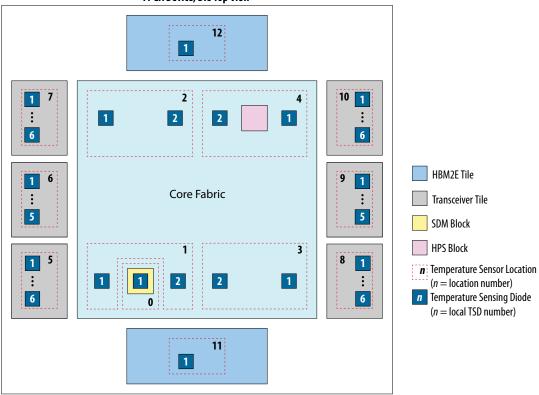

#### Figure 10. Temperature Sensing Diode Locations

This figure shows approximate locations of the temperature sensors and is not to scale. The figure shows the view of the die as shown in the Intel Quartus Prime **Chip Planner**. In the **Pin Planner**, this corresponds to the "Bottom View".

#### **FPGA Device, Die Top View**

Note:

Availability of the transceiver tiles varies among different Intel Agilex 7 series, densities, and packages. The HPS block is only available in Intel Agilex 7 SoC FPGAs. The HBM2E tiles are only available in M-Series FPGAs.

- To monitor the HPS temperature, use TSD 1 in location 4.

- To monitor the SDM temperature, use the TSD in location 0.

#### Table 9. Temperature Sensor Locations Availability—Core Fabric

This table lists the availability of the temperature sensor locations and TSDs in the core fabric for different Intel Agilex 7 device densities. For more information about the device densities, refer to the Intel Agilex 7device overview.

| Location | TSD | F-Se    | eries   | I-Se    | eries   | M-Series  |

|----------|-----|---------|---------|---------|---------|-----------|

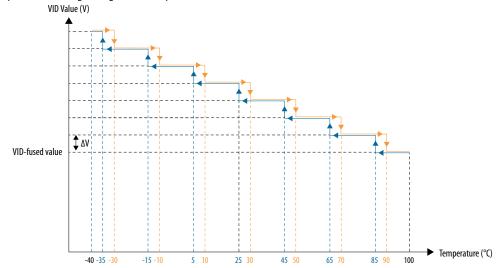

|          |     | AGF 006 | AGF 012 | AGI 019 | AGI 022 | AGM 032   |