# **LDO Thermal Performance**

Kyle Van Renterghem Applications Manager

#### **Topics**

- JEDEC Standard

- Using θja

- Guidelines For Maximum Thermal Relief

#### **JEDEC Thermals**

- Because an IC's thermal dissipation is subject to many variables we use the JEDEC standard (JESD51) for all thermal modeling.

- The JEDEC standard is used so that devices can be easily compared on a similar basis.

- if a competitor is not reporting the JEDEC standard the customer should consider why they don't want to be directly compared to other devices.

- Common thermal metrics:  $\theta_{JA}$ ,  $\theta_{JB}$ ,  $\theta_{JC(top)}$ ,  $\theta_{JC(bot)}$ TI Datasheet

| Competitor | Datasheet |

|------------|-----------|

|------------|-----------|

|                                                                                                   |                                                                                                          | TPS732 <sup>(3)</sup>                                                      |                                                      |                                            |       |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------|-------|

|                                                                                                   | THERMAL METRIC <sup>(1)(2)</sup>                                                                         |                                                                            | DCQ<br>[SOT223]                                      | DBV [SOT23]                                | UNIT  |

|                                                                                                   |                                                                                                          |                                                                            | 6 PINS                                               | 5 PINS                                     |       |

| R <sub>eja</sub>                                                                                  | Junction-to-ambient thermal resistance                                                                   | 58.3                                                                       | 53.1                                                 | 205.9                                      |       |

| R <sub>0JC(top)</sub>                                                                             | Junction-to-case (top) thermal resistance                                                                | 93.8                                                                       | 35.2                                                 | 119                                        |       |

| R <sub>eJB</sub>                                                                                  | Junction-to-board thermal resistance                                                                     | 72.8                                                                       | 7.8                                                  | 35.4                                       | °C/W  |

| Ψյт                                                                                               | Junction-to-top characterization parameter                                                               | 2.7                                                                        | 2.9                                                  | 12.7                                       | C/W   |

| Ψјв                                                                                               | Junction-to-board characterization parameter                                                             | 25                                                                         | 7.7                                                  | 34.5                                       |       |

| R <sub>eJC(bot)</sub>                                                                             | Junction-to-case (bottom) thermal resistance                                                             | 5                                                                          | N/A                                                  | N/A                                        |       |

| ₽ <sub>JT</sub><br>₽ <sub>JB</sub><br>R <sub>6JC(bot)</sub><br>1) Formo<br>2) Forthe<br>3) Therma | Junction-to-top characterization parameter<br>Junction-to-board characterization parameter               | 2.7<br>25<br>5<br>IC Package Therm<br>TI PCB Thermal<br>mal simulations ba | 2.9<br>7.7<br>N/A<br>nal Metrics appl<br>Calculator. | 12.7<br>34.5<br>N/A<br>ication report, SPR | ×A953 |

| (a) i.                                                                                            | DRB: The exposed pad is connected to the PCB groun<br>DCQ: The exposed pad is connected to the PCB groun | d layer through                                                            |                                                      |                                            |       |

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                      | Test Conditions (Typical Value) U |                                                                               |                                     | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------|-------------------------------------|------|

| DPAK 5-PIN PACKAGE                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |                                                                               |                                     |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                     | Min Pad Board (N                  | lote 3)                                                                       | 1" Pad Board (Note 4)               |      |

| Junction-to-Tab (psi-JLx, $\psi_{JLx}$ )                                                                                                                                                                                                                                                                                                                                                                            | 4.2                               |                                                                               | 4.7                                 | C/W  |

| Junction-to-Ambient (R <sub>BJA</sub> , $\theta_{JA}$ )                                                                                                                                                                                                                                                                                                                                                             | 100.9                             |                                                                               | 46.8                                | C/W  |

| D <sup>2</sup> PAK 5-PIN PACKAGE                                                                                                                                                                                                                                                                                                                                                                                    |                                   |                                                                               |                                     |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.4 sq. in. Spreader Bo           | ard (Note 5)                                                                  | 1.2 sq. in. Spreader Board (Note 6) |      |

| Junction-to-Tab (psi-JLx, $\psi_{JLx}$ )                                                                                                                                                                                                                                                                                                                                                                            | 3.8                               |                                                                               | 4.0                                 | C/W  |

| Junction-to-Ambient (R <sub><math>\theta</math>JA</sub> , $\theta$ <sub>JA</sub> )                                                                                                                                                                                                                                                                                                                                  | 74.8                              | 41.6                                                                          |                                     | C/W  |

| <ol> <li>1 oz. copper, 0.26 inch<sup>2</sup> (168 mm<sup>2</sup>) copper area, 0.062" thick FR4.</li> <li>1 oz. copper, 1.14 inch<sup>2</sup> (736 mm<sup>2</sup>) copper area, 0.062" thick FR4.</li> <li>1 oz. copper, 0.373 inch<sup>2</sup> (241 mm<sup>2</sup>) copper area, 0.062" thick FR4.</li> <li>6. 1 oz. copper, 1.222 inch<sup>2</sup> (788 mm<sup>2</sup>) copper area, 0.062" thick FR4.</li> </ol> |                                   | 28mm x 28mm area on the<br>top side dedicated to only<br>thermal dissipation? |                                     |      |

# **θ**<sub>JA</sub>: Understanding Usage and Limitations

- The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is the most commonly used thermal metric.

- $\theta_{JA}$  is a measure of the thermal performance of an IC mounted on a PCB.

- $\theta_{JA}$  is used since the ambient temperature is one of the few temperatures that designers have accurate data on.  $T_J = T_A + (\theta_{JA} * P_D)$

- The board acts as the main heat sink for any IC attached to it

TU

If the actual application board is significantly different from the JEDEC High-K board this can result in an estimate that is unrealistic

|           | Factors Affecting θja              | Strength of Influence<br>(rule of thumb) | Relation to θja                                                                            |  |  |

|-----------|------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

|           | PCB design                         | Very Strong                              | The more metal connected to the IC the lower $\theta$ a due to larger thermal mass         |  |  |

|           | Chip or pad size                   | Strong                                   | The larger the chip and thermal pad the lower $\theta$ a due to heat spreading             |  |  |

|           | Altitude                           | Medum                                    | The lower the altitude the lower $\theta$ ja due to increased cooling efficiency of air    |  |  |

| Exte      | ernal ambient temperature          | Weak                                     | The higher the ambient temp the lower $\theta$ ja due to increased radiative heat transfer |  |  |

|           | Power dissipation                  | Very Weak                                | The higher the junction temp the lower $\theta$ ja due to increased heat transfer          |  |  |

| Informati | Information – Selective Disclosure |                                          |                                                                                            |  |  |

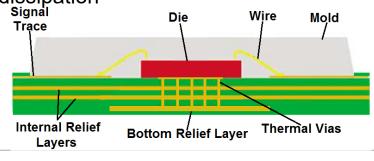

### **JEDEC High-K Board**

- TI LDO thermal metrics are modeled using the JEDEC High-K Board (2s2p)

- The JEDEC High-K board has:

- Two internal planes which have ~5500mm<sup>2</sup> of 1oz copper (1 GND & 1 PWR plane)

- Bottom layer (opposite the IC) thermal relief layer which has ~1100mm<sup>2</sup> of 2oz copper

- One internal GND plane and bottom GND plane are connected to the thermal pad using as many thermal vias as can be fit within the power pad dimensions.

- The top layer only has traces running straight to the pins.

- The JEDEC high-k board is good but not 100% optimized for maximum thermal dissipation

TI Information - Selective Disclosure

| TEST BOARD<br>DESIGN         | JEDEC HIGH-K<br>2s2p   | JEDEC LOW-K<br>1s0p       |  |

|------------------------------|------------------------|---------------------------|--|

| Trace thickness              | 0.0028 in              |                           |  |

| Trace length                 | 0.98 in                |                           |  |

| PCB thickness                | 0.062 in               |                           |  |

| PCB width                    | 4 in                   |                           |  |

| PCB length                   | 4.5 in                 |                           |  |

| Power/ground plane thickness | 0.0014in<br>(2 planes) | No internal copper planes |  |

### **Guidelines For Maximum Thermal Relief**

- ✓ Have as much metal as possible in the areas around the device (on both the same layer and the layers below the IC)

- 2oz copper is better than 1oz copper simply because there is extra metal

- The more thermal vias the better spreading the heat between the different layers

- ✓ An array of thermal vias maximizes the amount of heat which can be transferred from the LDO to the internal and bottom layers.

- With a large enough thermal via array the internal layers can dissipate heat almost as well as the top layer which is often crowded with other components.

- Vias should be as small as possible to decrease the amount of open space in the via hole (this maximizes the amount of metal)

- Ideally these thermal vias are all within the power pad landing pattern, but if the power pad is too small then placing extra vias as close as possible to the power pad is still helpful

- If the board is large, there is a lot of metal, and the thermal vias are maximized then it is possible to reduce the θja by 25%-50%.

TI Information - Selective Disclosure

### **Other Thermal Considerations**

- Nearby heat sources on the PCB can reduce the ability of the LDO to shed heat to the board

- This is because those other heat sources increase the local board temperature decreasing the temperature differential between the board to the LDO in question

- Load pulses can still heat the die significantly if the duty cycle isn't low

- A step increase in power dissipation will cause the die temp to stabilize on the order of hundreds of milliseconds to 1 second

- For ~1 second pulses the LDO should reach a similar internal temp as if the load was on constantly

- Pulses of tens of milliseconds don't heat the die nearly as much

- Forced convection and board level heatsinks can help significantly, though they are rarely a consideration for many applications which have to rely on passive cooling only

- The thermal models in our datasheets assume natural convection (no forced air).

- Some customer applications have a metal enclosure and it is punched so that the metal enclosure makes contact with ICs which are dissipating large amounts of power. This conduction of heat is much more affective than standard natural convection cooling.

TI Information – Selective Disclosure

## **2** methods for testing effective $\theta_{JA}$ of a PCB

- 1. For applications which can force ambient temp >165C

- a. Set a very light load on the output (ideally less 1mA or less)

- b. Increase the ambient temp until the device enters thermal shutdown (~165C). Note this temp as Tsd

- c. Decrease the ambient temperature at least until the devices turns back on (we usually use ~85C but in general lower is better). Note this temp as Ta.

- d. Increase the power dissipation until the LDO turns off. Note this temp as Pd

- e. You can now calculate  $\theta_{JA} = (Tsd-Ta)/Pd$

- 2. For applications with limited ability to change ambient temp

- a. Assume the Tsd is equal to value listed in the EC table of the datasheet.

- a. Sims indicate it can vary +-5C, but we've not seen that much variation with actual units on the bench

- Set the ambient temperature so that the device is on (we usually use ~85C but in general lower is better).

Note this temp as Ta.

- c. Increase the power dissipation until the LDO turns off. Note this temp as Pd

- d. You can now calculate  $\theta_{JA} = (Tsd-Ta)/Pd$