## TPS61042DRB New package qualified

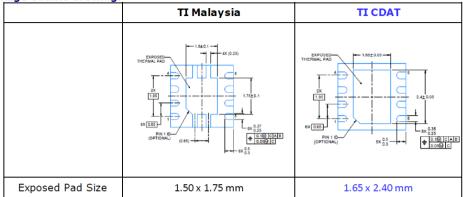

One of my customers knows that a new package made at TI CDAT assembly site were qualified as an additional package of TPS61042DRB via PCN# 20230719001.1

Package outline drawing:

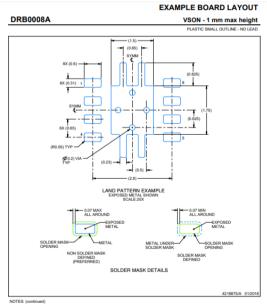

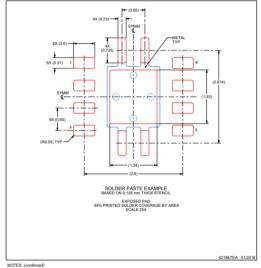

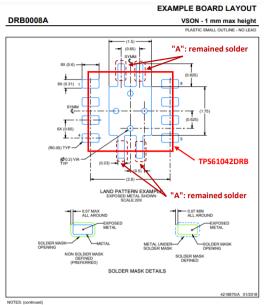

They designed TPS61042DRB foot pattern on their PCB by copying example board layout on page 27 of the device datasheet. Their stencil design is same. It was designed by copying example stencil design on page 28 of the datasheet.

ing on application, refer to device data sheet. If any vias are implended that vias under paste be filed, plugged or tented.

They think that remained solder of pattern "A" would become solder ball when the package made at TI CDAT is soldered without PCB footpattern changing and they worry that this solder ball would cause any trouble.

NO LES (commune)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Yexas Instruments (Berature marcher SLUATY) (www.st.com/ttchusz/Y).

5. Vas are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations show on this view. It is encommended that view under paste be filled, plugged or tented.

## [Question]

What do TI think about this? They want to hear TI thought.