# TPS65910 User Guide For OMAPL-137, OMAPL-138, and TMS320C674x Family of Processors

This user guide can be used as a reference for connectivity between the TPS65910 power-management integrated circuit (PMIC) and TI OMAPL, TMS320C674x processors.

#### Contents

| 1 | Introduction                                                                           | . 1 |

|---|----------------------------------------------------------------------------------------|-----|

| 2 | Platform Connection                                                                    | . 2 |

| 3 | Power-Up Sequencing                                                                    |     |

| 4 | Getting Started With TPS65910 and OMAPL-137, OMAPL-138, and TMS320C6742/6/8 Processors | . 8 |

| 5 | Revision History                                                                       | . 9 |

|   | List of Figures                                                                        |     |

| 1 | OMAPL-137 Power Supply Connections With TPS65910                                       | 2   |

| 2 | OMAPL-138, TMS320C6742/6/8 Power Connections With TPS65910                             | 3   |

| 3 | Power-Up Timing Diagram                                                                | 6   |

|   | List of Tables                                                                         |     |

| 1 | Power Rail Requirements for OMAPL-138, TMS320C6742/6/8                                 | 4   |

| 2 | Power Rail Requirements for OMAPL-137                                                  | 4   |

| 3 | Power-Up Sequence for TPS65910                                                         | 5   |

| 4 | EEPROM Configuration for TPS65910                                                      | 6   |

| 5 | REVISION HISTORY                                                                       | 9   |

#### 1 Introduction

This user guide can be used as a reference for connectivity between the TPS65910 PMIC and TI OMAPL, TMS320C674x processors. This user guide does not provide details about the power resources or the functionality of the device. For such information, refer to the full specification document, *TPS65910 Data Manual*.

Platform Connection www.ti.com

#### 2 Platform Connection

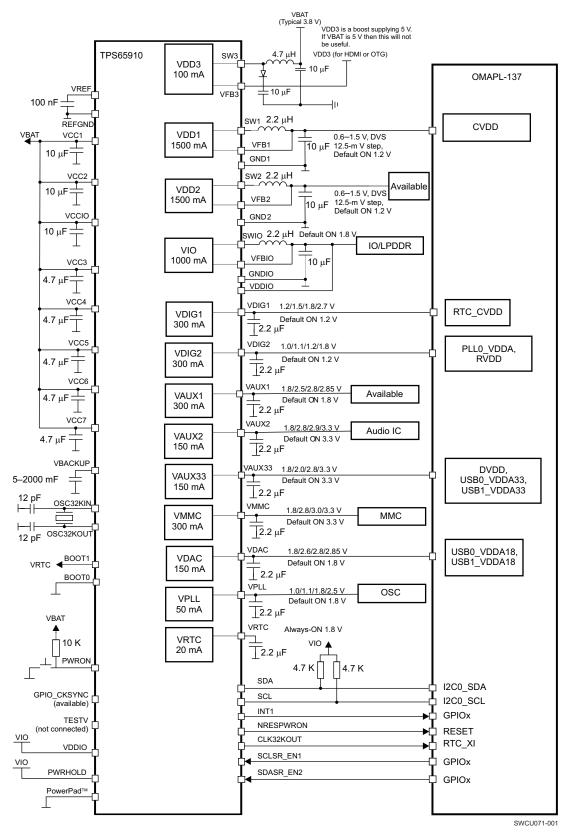

Figure 1. OMAPL-137 Power Supply Connections With TPS65910

www.ti.com Platform Connection

NOTE: If only 1.8 V operation is required, then these domains can be merged with 1.8 V on VIO.

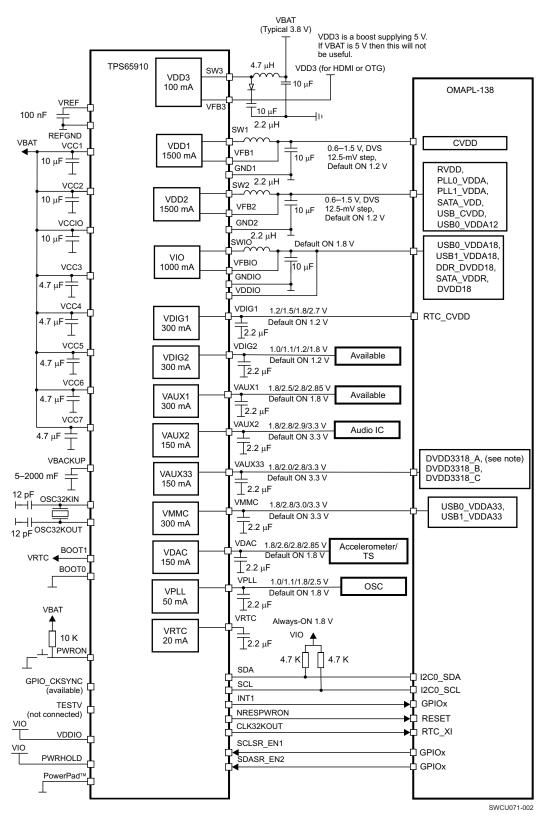

Figure 2. OMAPL-138, TMS320C6742/6/8 Power Connections With TPS65910

At power up, the maximum current capability (default setting) of the DCDC converters is as follows:

3

Power-Up Sequencing www.ti.com

- VIO(max) = 500 mA

- VDD1(max) = 1000 mA

- VDD2(max) = 1000 mA

To have the maximum current capability, the user must program the following register bits:

- VIO\_REG[ILMAX] = b01 for 1 A

- VDD1\_REG[ILMAX] = b1 for 1.5 A

- VDD2\_REG[ILMAX] = b1 for 1.5 A

# 3 Power-Up Sequencing

# 3.1 Power-Up Sequence for OMAPL-138 and TMS320C6742/6/8 Processors

The following sections show the power-up sequence requirement for OMAPL-138 and TMS320C6742/6/8 processors. To power on the system, the user must press and release the PWRON switch (generating a negative pulse). The BOOT pads on the TPS65910 must be connected as follows:

- BOOT0 = 0

- BOOT1 = 1

Table 1 lists the power rail requirements for OMAPL-138, TMS320C6742/6/8.

Table 1. Power Rail Requirements for OMAPL-138, TMS320C6742/6/8

| Power Domain                           | Pin Name                                                        | I <sub>max</sub> (mA) | Voltage (V) | Sequence         |

|----------------------------------------|-----------------------------------------------------------------|-----------------------|-------------|------------------|

| I/O                                    | I/O RTC_CVDD                                                    |                       | 1.2         | 1 <sup>(1)</sup> |

| Core                                   | Core CVDD <sup>(2)</sup>                                        |                       | 1.0/1.1/1.2 | 2                |

| I/O                                    | I/O RVDD, PLL0_VDDA, PLL1_VDDA, SATA_VDD, USB_CVDD, USB0_VDDA12 |                       | 1.2         | 3                |

| I/O                                    | I/O USB0_VDDA18, USB1_VDDA18, DDR_DVDD18, SATA_VDDR, DVDD18     |                       | 1.8         | 4                |

| I/O                                    | USB0_VDDA33, USB1_VDDA33 <sup>(3)(4)</sup>                      | 24                    | 3.3         | 5                |

| I/O DVDD3318_A, DVDD3318_B, DVDD3318_C |                                                                 | 90 <sup>(5)</sup>     | 3.3         | 5                |

<sup>(1)</sup> If RTC is not used/maintained on a separate supply, it can be included in the STATIC12 (fixed 1.2 V) group.

# 3.2 Power-Up Sequence for OMAPL-137 Processor

Table 2 lists the power rail requirements for OMAPL-137.

Table 2. Power Rail Requirements for OMAPL-137

| Power Domain                 | Pin Name                      | I <sub>max</sub> (mA) | Voltage (V) (2) | Sequence |

|------------------------------|-------------------------------|-----------------------|-----------------|----------|

| Core RTC_CVDD <sup>(1)</sup> |                               | 0.1                   | 1.2             | 1        |

|                              | CVDD                          | 600                   | 1.2             | 2        |

|                              | PLL0_VDDA, RVDD               | 60                    | 1.2             | 3        |

| I/O                          | USB0_VDDA18, USB1_VDDA18      | 50                    | 1.8             | 5        |

| I/O                          | DVDD, USB0VDDA33, USB1_VDDA33 | 115                   | 3.3             | 4        |

<sup>(2)</sup> If using CVDD at fixed 1.2 V, all 1.2-V rails may be combined. CVDD can support 1.3 V; in this case SMPS (VDD1) supplying CVDD core can be set to 1.3-V after initial power up.

<sup>(3)</sup> If 1.8-V LVCMOS is used, power rails up with the 1.8-V rails. If 3.3-V LVCMOS is used, power it up with the ANALOG33 rails (VDDA33\_USB0/1).

<sup>(4)</sup> There is no specific required voltage ramp rate for any of the supplies LVCMOS33 (USB0\_VDDA33, USB1\_VDDA33) that never exceeds STATIC18 by more than 2 V.

<sup>(5)</sup> If DVDD3318\_A, B, and C are powered independently, maximum power for each rail will be 1/3 the above maximum power. These rails can be connected independently to 1.8 or 3.3 V.

Power-Up Sequencing www.ti.com

(1) RTC\_CVDD can be combined with PLL and RAM 1.2-V supplies if desired to turn off RTC when device is off. Otherwise, power RTC\_CVDD separately with a dedicated power source.

#### (2) Sequencing 1.2-V supplies:

- (a) RTC (RTC\_CVDD) may be powered from an external device (such as a battery) before all other supplies are applied. If the RTC is not used, RTC\_CVDD must be connected to CVDD.

- Group 2a: CVDD core logic supply. CVDD can support 1.3 V, in this case SMPS (VDD1) supplying CVDD core can be set to 1.3 V after initial power up.

- (c) Group 2b: Other 1.2-V logic supplies (RVDD, PLL0\_VDDA). Groups 2a and 2b may be powered up together or 2a first followed by 2b.

NOTE: To correctly power on the device, the PWRHOLD signal must be high after PWRON is pressed. In this configuration the PWRHOLD signal on TPS65910 is connected to VIO. PWRHOLD transitions to high when VIO powers up.

#### 3.3 Power-Up Sequence for TPS65910

To satisfy the power-up requirements for the OMAPL-138 and TMS320C6742/4/6 processors, the TPS65910 powers up with the default sequence when in the EEPROM boot mode configuration (BOOT0) = 0 and BOOT1 = 1) (see Table 3). The correct power-up sequence is configured in the EEPROM (factory programmable only).

Apart from the main power rails required by the processors, all other rails are also powered up at initial power up to support other system peripherals.

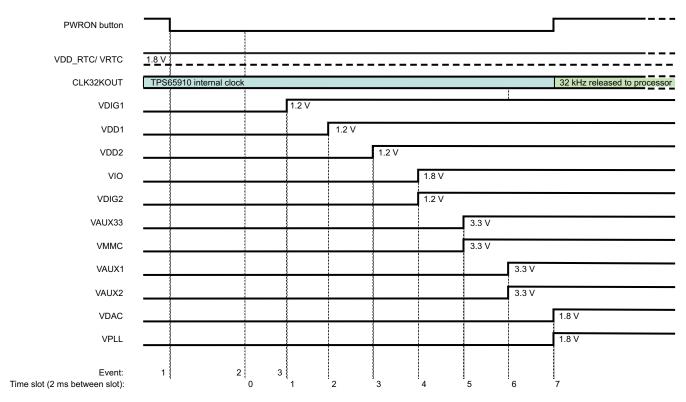

Figure 3 shows a typical power-up timing diagram.

Table 3 shows the power-up sequence.

Table 3. Power-Up Sequence for TPS65910

| TPS65910 Power Rail  | Voltage (V) | Sequence Number | Delay (ms) |

|----------------------|-------------|-----------------|------------|

| PWRON <sup>(1)</sup> | -           | _               |            |

| VDIG1                | 1.2         | 1               | 2          |

| VDD1                 | 1.2         | 2               | 2          |

| VDD2                 | 1.2         | 3               | 2          |

| VIO                  | 1.8         | 4               | 2          |

| VDIG2                | 1.2         | 4               | 0          |

| VAUX33               | 3.3         | 5               | 2          |

| VMMC                 | 3.3         | 5               | 0          |

| VAUX1                | 1.8         | 6               | 2          |

| VAUX2                | 3.3         | 6               | 0          |

| VDAC                 | 1.8         | 7               | 2          |

| VPLL                 | 1.8         | 7               | 0          |

The PWRON signal is the start-on event. All timings listed are with respect to the previous event.

Power-Up Sequencing www.ti.com

Event description: 1 PWRON button press falling edge

2 Valid press after debounce

3 First step of power-up sequence available for DCDC, LDO activation. Time slot 0 is for internal use.

Note: PWRON press must be maintained until PWRHOLD acknowledge, or, for shorter PWRON press,

PWRHOLD must go high within 984 ms of valid PWRON press (event 2). To ensure this, PWRHOLD is tied to VIO.

SWCU071-003

Figure 3. Power-Up Timing Diagram

**Table 4. EEPROM Configuration for TPS65910**

| Register                     | Bit        | Description                           | Option Selected |

|------------------------------|------------|---------------------------------------|-----------------|

| VDD1_OP_REG                  | SEL        | VDD1 voltage level selection for boot | 1.2 V           |

| VDD1_REG                     | VGAIN_SEL  | VDD1 gain selection, x1 or x2         | x1              |

| EEPROM                       |            | VDD1 time slot selection              | 2               |

| DCDCCTRL_REG                 | VDD1_PSKIP | VDD1 pulse skip mode enable           | Skip enabled    |

| VDD2_OP_REG /<br>VDD2_SR_REG | SEL        | VDD2 voltage level selection for boot | 1.2 V           |

| VDD2_REG                     | VGAIN_SEL  | VDD2 gain selection, x1 or x3         | x1              |

| EEPROM                       |            | VDD2 time slot selection              | 3               |

| DCDCCTRL_REG                 | VDD2_PSKIP | VDD2 pulse skip mode enable           | Skip enabled    |

| VIO_REG                      | SEL        | VIO voltage selection                 | 1.8 V           |

| EEPROM                       |            | VIO time slot selection               | 4               |

| DCDCCTRL_REG                 | VIO_PSKIP  | VIO pulse skip mode enable            | Skip enabled    |

| EEPROM                       |            | VDD3 time slot                        | OFF             |

| VDIG1_REG                    | SEL        | LDO voltage selection                 | 1.2             |

| EEPROM                       |            | LDO time slot                         | 1               |

| VDIG2_REG                    | SEL        | LDO voltage selection                 | 1.2 V           |

| EEPROM                       |            | LDO time slot                         | 4               |

| VDAC_REG                     | SEL        | LDO voltage selection                 | 1.8 V           |

| EEPROM                       |            | LDO time slot                         | 7               |

www.ti.com Power-Up Sequencing

# Table 4. EEPROM Configuration for TPS65910 (continued)

| Register      | Bit            | Description                                                                                                                             | Option Selected                               |

|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| VPLL_REG      | SEL            | LDO voltage selection                                                                                                                   | 1.8 V                                         |

| EEPROM        |                | LDO time slot                                                                                                                           | 7                                             |

| VAUX1_REG     | SEL            | LDO voltage selection                                                                                                                   | 1.8 V                                         |

| EEPROM        |                | LDO time slot                                                                                                                           | 6                                             |

| VMMC_REG      | SEL            | LDO voltage selection                                                                                                                   | 3.3 V                                         |

| EEPROM        |                | LDO time slot                                                                                                                           | 5                                             |

| VAUX33_REG    | SEL            | LDO voltage selection                                                                                                                   | 3.3 V                                         |

| EEPROM        |                | LDO time slot                                                                                                                           | 5                                             |

| VAUX2_REG     | SEL            | LDO voltage selection                                                                                                                   | 3.3 V                                         |

| EEPROM        |                | LDO time slot                                                                                                                           | 6                                             |

| CLK32KOUT pin |                | CLK32KOUT time slot                                                                                                                     | 7                                             |

| NRESPWRON pin |                | NRESPWRON time slot                                                                                                                     | 7 + 1                                         |

| VRTC_REG      | VRTC_OFFMASK   | 0 = VRTC LDO will be in low-power mode during OFF state. 1 = VRC LDO will be in full-power mode during OFF state.                       | Low-power mode                                |

| DEVCTRL_REG   | RTC_PWDN       | 0 = RTC in normal power mode<br>1 = Clock gating of RTC register and logic,<br>low-power mode                                           | 1                                             |

| DEVCTRL_REG   | CK32K_CTRL     | 0 = Clock source is crystal/external clock.<br>1 = Clock source is internal RC oscillator.                                              | Crystal                                       |

| DEVCTRL2_REG  | TSLOT_LENGTH   | Boot sequence time slot duration:<br>0 = 0.5 ms<br>1 = 2 ms                                                                             | 2 ms                                          |

| DEVCTRL2_REG  | IT_POL         | 0 = INT1 signal will be active low.<br>1 = INT1 signal will be active high.                                                             | Active low                                    |

| INT_MSK_REG   | VMBHI_IT_MSK   | 0 = Device automatically switches on at NO SUPPLY-to-OFF or BACKUP-to-OFF transition. 1 = Start-up reason is required before switch-on. | 0 = Automatic switch on from supply insertion |

| VMBCH_REG     | VMBCH_SEL[1:0] | Select threshold for main battery comparator threshold VMBCH.                                                                           | 3 V                                           |

# 4 Getting Started With TPS65910 and OMAPL-137, OMAPL-138, and TMS320C6742/6/8 Processors

#### 4.1 First Initialization

#### 4.1.1 I/O Polarity/Muxing Configuration

Program DEVCTRL2\_REG.SLEEPSIG\_POL according to the GPIO from the processor. This can be set to active low or active high for SLEEP transition. Software configuration allows specific power resources to enter low consumption state.

Set DEVCTRL\_REG.DEV\_SLP = 1 to allow SLEEP transition when requested.

Update the GPIO0 configuration (GPIO0\_REG) based on your needs.

#### 4.1.2 Define Wake-Up/Interrupt Event (SLEEP or OFF)

Select the appropriate bits in the INT\_MSK\_REG and INT\_MSK2\_REG registers to activate an interrupt to the processor on the INT1 line.

#### 4.1.3 Backup Battery Configuration

If the system has a backup battery, set the BBCHEN bit to 1 in the BBCH\_REG register, to enable backup battery charging. The maximum voltage to which the backup battery is charged is set by the BBSEL bits.

# 4.1.4 DCDC and Voltage Scaling Resource Configuration

Set DEVCTRL\_REG[SR\_CTL\_I2C\_REG] = 1 to control register using the control I<sup>2</sup>C interface. Using the SCLSR\_EN1 and SDASR\_EN2 signals, the user can control the power resources. For OMAPL series, the following example is provided:

- SMPS control:

- Configure two operating voltages for DCDC1 and DCDC2:

- VDDx\_OP\_REG.SEL= Roof voltage (ENx ball high)

- VDDx\_SR\_REG.SEL = Floor voltage (ENx ball low)

- Assign control for VDD1 to SCLSR\_EN1:

- Set EN1 SMPS ASS REG.VDD1 EN1 = 1

- Set SLEEP\_KEEP\_RES\_ON\_REG.VDD1\_KEEPON = 1 (allow low-power mode)

- LDO control:

- Assign control for VMMC regulator (for example, can be used for any other set of registers).

- Set EN2\_LDO\_ASS\_REG.VMMC\_EN2 = 1

- When SDASR\_EN2 control signal is high then the regulator output depends on SLEEP\_KEEP\_LDO\_ON setting.

- SDASR EN2 = 1, VMMC status is active.

- SDASR EN2 = 0 then:

- SLEEP\_KEEP\_LDO\_ON[VMMC\_KEEPON] = 0, VMMC output is off.

- SLEEP KEEP LDO ON[VMMC KEEPON] = 1, VMMC output is on in LOW-POWER state.

#### 4.1.5 Sleep Platform Configuration

Configure the state of the LDOs when the SLEEP signal is used (by default all resources go into SLEEP state; in SLEEP state the LDO voltage is maintained but transient and load capability are reduced).

Resources that must provide full load capability must be set in the SLEEP\_KEEP\_LDO\_ON\_REG register.

Resources that can be set off in SLEEP state to optimize power consumption must be set in the SLEEP\_SET\_LDO\_OFF\_REG register.

www.ti.com Revision History

# 4.2 Event Management Through Interrupts

# 4.2.1 INT\_STS\_REG.VMBHI\_IT

INT\_STS\_REG.VMBHI\_IT indicates that the supply (VBAT) is connected (leaving the BACKUP or NO SUPPLY state), the system must be initialized. (See Section 4.1, First Initialization.)

#### 4.2.2 INT STS REG.PWRON IT

INT\_STS\_REG.PWRON\_IT is triggered when the PWRON button is pressed. If device is in OFF or SLEEP state, then this acts as a wake-up event and resources are reinitialized.

# 4.2.3 INT\_STS\_REG.PWRON\_LP\_IT

INT\_STS\_REG.PWRON\_LP\_IT is the PWRON long-press interrupt. This interrupt is generated when the PWRON button is pressed for 6 seconds. The application processor can make a decision to acknowledge the interrupt. If this interrupt is not acknowledged in the next 2 seconds then the device interprets this as a power-down event.

#### 4.2.4 INT STS REG.HOTDIE IT

INT\_STS\_REG.HOTDIE\_IT indicates that the temperature of die is reaching the limit. Software must take action to decrease the power consumption before automatic shutdown.

#### 4.2.5 INT\_STS\_REG.VMBDCH\_IT

INT\_STS\_REG.VMBDCH\_IT idicates that the input supply is low and the processor must prepare a shutdown to prevent losing data. This interrupt is linked to VBAT but does not apply to a system where PMIC is connect to 5-V rails and not directly to VBAT.

#### 4.2.6 INT STS2 REG.GPIO R/F IT

INT\_STS2\_REG.GPIO\_R/F\_IT is the GPIO interrupt event and can be used to wake up the device from SLEEP state. This can be an interrupt coming from any peripheral device or alike.

NOTE: This wake-up event is not valid for a transition from OFF state.

#### 4.2.7 INT STS REG. RTC ALARM IT

INT\_STS\_REG. RTC\_ALARM\_IT is triggered when the RTC alarm set time is reached.

#### 5 Revision History

#### **Table 5. REVISION HISTORY**

| Version Literature Number |   | Date     | Notes         |          |

|---------------------------|---|----------|---------------|----------|

|                           | * | SWCU071  | December 2010 | See (1). |

|                           | Α | SWCS071A | July 2011     | See (2). |

<sup>(1)</sup> TPS65910 User Guide For OMAPL-137, OMAPL-138, and TMS320C674x, SWCU071 - Initial release.

<sup>&</sup>lt;sup>2)</sup> TPS65910 User Guide For OMAPL-137, OMAPL-138, and TMS320C674x, SWCU071A:

Update Table 3: Change VAUX1 from 3.3 V to 1.8 V.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                  |                                   |

|-----------------------------|------------------------|-------------------------------|-----------------------------------|

| Audio                       | www.ti.com/audio       | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers                  | amplifier.ti.com       | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters             | dataconverter.ti.com   | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products               | www.dlp.com            | Energy and Lighting           | www.ti.com/energy                 |

| DSP                         | dsp.ti.com             | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers           | www.ti.com/clocks      | Medical                       | www.ti.com/medical                |

| Interface                   | interface.ti.com       | Security                      | www.ti.com/security               |

| Logic                       | logic.ti.com           | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt                  | power.ti.com           | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers            | microcontroller.ti.com | Video and Imaging             | www.ti.com/video                  |

| RFID                        | www.ti-rfid.com        | Wireless                      | www.ti.com/wireless-apps          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |                               |                                   |

**TI E2E Community Home Page**

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated

e2e.ti.com