### UCC21225A SCH Review and PCB Recommendations

#### Disclaimer

The information provided on this page represents TI's knowledge and belief as of the date that it is provided. No guarantees as to device or system performance are implied.

| Rev | Date released | Changes         | Author        |

|-----|---------------|-----------------|---------------|

| 1.0 | -             | Initial release | (Author name) |

#### **Table of Contents**

- Glossary

- Typical Device Schematic

- Primary-side Checklist

- Secondary-side Checklist

- UCC21225 Unused pins

- UCC21225 Layout Recommendations

#### **TI Comments**

(TI summary of findings in the review)

### Glossary

#### For each component:

- A component labeled REQUIRED denotes it is necessary for normal operation of the driver and may have significant consequences if omitted.

- A component labeled RECOMMENDED denotes that TI thinks its usage provides system benefit and recommends its usage to achieve best device performance.

- A component labeled OPTIONAL denotes that its usage depends on a specific configuration and may provide benefits in a limited scope.

#### When TI checks the schematic:

- An evaluation of Good means that TI thinks the components/circuit connected to a pin and usage of the pin are acceptable and will allow normal system function

- An evaluation of NEEDS REVIEW means that TI sees an issue with the components/circuit connected to a pin or usage of the pin. Schematic review checklist table below is expected to be followed.

- An evaluation of NOT APPLICABLE means that the design doesn't use configure or enable a specific features.

TI Confidential – NDA Restrictions Page 1 of 9

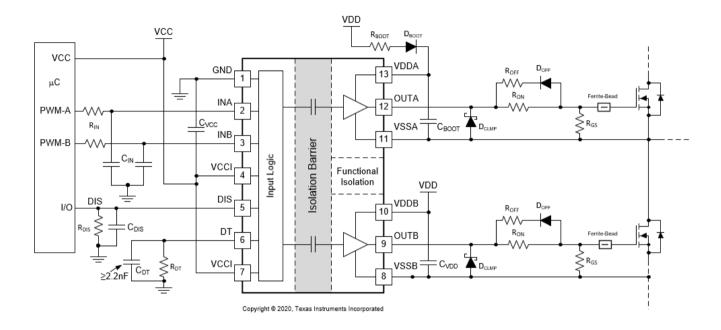

## **Typical Device Schematic**

TI Confidential – NDA Restrictions

# **Primary-side Checklist**

| System                   | Pin # | PIN<br>Name | Component<br>Name | Usage is? | Component<br>Function     | Typ. Value                                                                                  | Component<br>Details                                                                                                                      | Layout<br>Suggestions                                                                                                 | Evaluation   | Comments |

|--------------------------|-------|-------------|-------------------|-----------|---------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|----------|

| Bypass Caps              | 4,7   | vccı        | C <sub>VCCI</sub> | REQUIRED  | Big Decoupling Cap        | >1uF                                                                                        | Tantalum or<br>Electrolytic parallel<br>to small capacitor<br>when when bias<br>supply is a at a<br>relatively long<br>distance from VCCI | Place on same side<br>5mm away from the pin.  Prioritize the placement<br>of the smaller cap<br>closer to the driver. | GOOD         |          |

|                          |       |             |                   | REQUIRED  | Small Decoupling<br>Cap   | >100nF                                                                                      | 25V , MLCC, X7R recommended                                                                                                               |                                                                                                                       |              |          |

| Input Signal             | 2,3   | INA         | R <sub>IN</sub>   | REQUIRED  | Input RC Filter           | 0 - 100<br>10pF - 100pF                                                                     | Helps to filter out<br>ringing induced by<br>non-ideal layout or<br>long PCB traces                                                       | Place on same side<br>5mm away from the pin.                                                                          | NEEDS REVIEW |          |

| Programable<br>Dead Time | 6     | DT          | R <sub>DT</sub>   | REQUIRED  | User Defined Dead<br>Time | Based on DT equation RDT in k $500 - 500 \text{k}$ $t_{DT}(ns) = 10 \times R_{DT}(k\Omega)$ | For larger values of DT, it is recommended placing a ceramic capacitor for higher noise immunity                                          | Place on same side<br>5mm away from the pin.                                                                          | NEEDS REVIEW |          |

|                          |       |             | C <sub>DT</sub>   | REQUIRED  | Helps Noise<br>Immunity   | >2.2nF                                                                                      |                                                                                                                                           |                                                                                                                       |              |          |

| Disable                  | 5     | DIS         | R <sub>DIS</sub>  | REQUIRED  | Pull Down Resistor        | 10k                                                                                         | Recommended to use a capacitor of                                                                                                         | Place on same side 5mm away from the pin.                                                                             | GOOD         |          |

|                          |       |             | C <sub>DIS</sub>  | REQUIRED  | Helps Noise<br>Immunity   | 1nF                                                                                         | low ESR/ESL close<br>to DIS pin when<br>connecting to a<br>microcontroller with<br>distance                                               |                                                                                                                       |              |          |

TI Confidential – NDA Restrictions

Page 3 of 9

# **Secondary-side Checklist**

| System     | Pin<br>#      | PIN<br>Name  | Component<br>Name | Usage is? | Component<br>Function         | Typ. Value                                                                                                                                                             | Component<br>Details                                                                                                                                               | Layout<br>Suggestions                                                                                                       | Evaluation   | Comments |

|------------|---------------|--------------|-------------------|-----------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------|----------|

| Gate Drive | 11,12<br>8,9  | OUTX<br>VSSX | R <sub>ON</sub>   | REQUIRED  | External Turn ON<br>Resistor  | Design based on specifications $I_{OA+} = MIN(4A, \frac{v_{DD}-v_{BDF}}{R_{NMOS}  R_{OH}+R_{ON}+R_{GFET-Int}})$                                                        | It is recommended<br>to have<br>placeholders to<br>allow for different<br>gate drive strength<br>when turning ON<br>/OFF the power<br>switches.                    | Place capacitor on<br>the same side 5mm<br>away from the pin.                                                               | NEEDS REVIEW |          |

|            |               |              | R <sub>OFF</sub>  | OPTIONAL  | External Turn<br>OFF Resistor | Design based on specifications $I_{OA+} = MIN(6A, \frac{v_{DD}-v_{BDF}-v_{GDF}}{R_{OL}+R_{OFF}  R_{ON}+R_{GFET-Int} })$                                                |                                                                                                                                                                    | High priority layout.  Place gate resistors as close to the gate as possible.                                               |              |          |

|            |               |              | D <sub>OFF</sub>  | OPTIONAL  | Anti-parallel Diode           |                                                                                                                                                                        |                                                                                                                                                                    |                                                                                                                             |              |          |

|            |               |              | R <sub>GS</sub>   | OPTIONAL  | Pull Down<br>Resistor         | 5.1k - 20k                                                                                                                                                             | Mitigates risk of dv<br>/dt induced turn-on<br>due to miller<br>current                                                                                            | Place as close to the gate as possible.                                                                                     | NEEDS REVIEW |          |

|            |               |              | Ferrite-Bead      | OPTIONAL  | Reducing Gate<br>Ringing      | Low resistance value during normal operation                                                                                                                           | Example Part<br>number:<br>MPZ1608S101A<br>It's recommended<br>to have<br>placeholders for<br>this component in<br>a high power, fast<br>switching<br>application. |                                                                                                                             |              |          |

|            |               |              | D <sub>CLMP</sub> | OPTIONAL  | Driver Output<br>Clamp        | Schottky                                                                                                                                                               | It's recommended<br>to have<br>placeholders for<br>this component in<br>a high power, fast<br>switching<br>application                                             | Clamp diode should<br>be place close to<br>the driver pin.                                                                  | NEEDS REVIEW |          |

| Bootstrap  | otstrap 11,13 | VDDA<br>VSSA | C <sub>BOOT</sub> | REQUIRED  | Bootstrap<br>Capacitor        | Based on design specifications $C_{BOOT} = rac{\mathcal{Q}_{TOTAL}}{\triangle V_{VDDA}}$                                                                              | Use the calculator for the design of the Bootstrap                                                                                                                 | Bootstrap capacitor<br>and bypass<br>capacitor should be<br>place as close as<br>possible to the gate<br>driver supply pins | NEEDS REVIEW |          |

|            |               |              | R <sub>BOOT</sub> | REQUIRED  | Bootstrap<br>Resistor         | 1 - 20 $I_{DBoot(pk)} = \frac{V_{DD} - V_{BDF}}{R_{Boot}}$                                                                                                             |                                                                                                                                                                    | current path that<br>includes CBOOT,<br>DBOOT, and<br>RBOOT. This will<br>minimize parasitic                                |              |          |

|            |               |              | D <sub>BOOT</sub> | REQUIRED  | Bootstrap Diode               | High Voltage(Voltage rating should be higher than the DC link), fast recovery diode or SiC Schottky diode with a low forward drop voltage and low junction capacitance |                                                                                                                                                                    |                                                                                                                             |              |          |

TI Confidential – NDA Restrictions

Page 4 of 9

| VDDB<br>Capacitor | 8,10 | VDDB | C <sub>VDD</sub> | REQUIRED | 10uF parallel with | 50V , MLCC, X7R recommended | Place as close as possible to the gate | NEEDS REVIEW |

|-------------------|------|------|------------------|----------|--------------------|-----------------------------|----------------------------------------|--------------|

|                   |      | VSSB |                  |          | 220nF              |                             | driver supply pins.                    |              |

|                   |      |      |                  |          | 10uF               | Tantalum or<br>Electrolytic |                                        |              |

TI Confidential – NDA Restrictions

Page 5 of 9

# UCC21225 Unused pins

| Side    | Pin Name   | Pin #s | What to do if Unused                                                                                                              | Urgency  |

|---------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|----------|

| Primary | INA or INB | 2 or 3 | Tie to ground for better noise immunity                                                                                           | REQUIRED |

|         | DIS        | 5      | Tie to ground for better noise immunity                                                                                           | REQUIRED |

|         | DT         | 6      | If Dead Time is no required and overlapping the outputs is allowed, DT pin can be connected to VCCI to disable Dead Time feature. | REQUIRED |

|         |            |        | It is not recommended to leave DT floating since external noise can couple into the pin affecting the outputs behavior.           |          |

TI Confidential – NDA Restrictions

Page 6 of 9

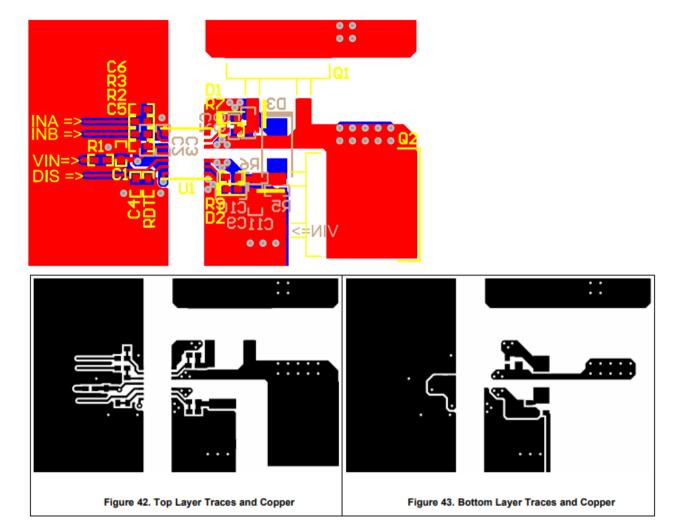

## **UCC21225 Layout Recommendations**

Recommendations Urgency Comments

TI Confidential – NDA Restrictions

Page 7 of 9

| Component<br>Placement         | <ul> <li>Decoupling capacitors should be placed as close as possible to the device pins</li> <li>Minimize parasitic inductance between HS source transistor and LS source transistor to avoid large negative transient currents</li> </ul>                                                                                                                                                                                                                                                                                            | REQUIRED |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| Grounding<br>Considerations    | <ul> <li>Driver should be place as close as possible to the transistors. Minimize loop inductance and noise in gate terminals by confining the high peak currents that charge and discharged transistor gates</li> <li>Minimize loop design for the bootstrap circuit.</li> </ul>                                                                                                                                                                                                                                                     | REQUIRED |  |

| High Voltage<br>Considerations | <ul> <li>To ensure isolation performance between primary and secondary side, avoid placing any PCB traces or copper below the driver device. PCB cutout is recommended to increase the creepage</li> <li>For half-bridge or high-side/low-side configurations, maximize the clearance distance of the PCB layout between the high and low-side PCB traces.</li> </ul>                                                                                                                                                                 | REQUIRED |  |

| Thermal<br>Considerations      | <ul> <li>If there are multiple layers in the system, it is also recommended to connect the VDDA, VDDB, VSSA and VSSB pins to internal ground or power planes through multiple vias of adequate size. Ensure that no traces or copper from different high-voltage planes overlap.</li> <li>Increasing the PCB copper connecting to VDDA, VDDB, VSSA and VSSB pins is recommended, with priority on maximizing the connection to VSSA and VSSB. However, high voltage PCB considerations mentioned above must be maintained.</li> </ul> | REQUIRED |  |

TI Confidential – NDA Restrictions

Page 8 of 9

TI Confidential – NDA Restrictions