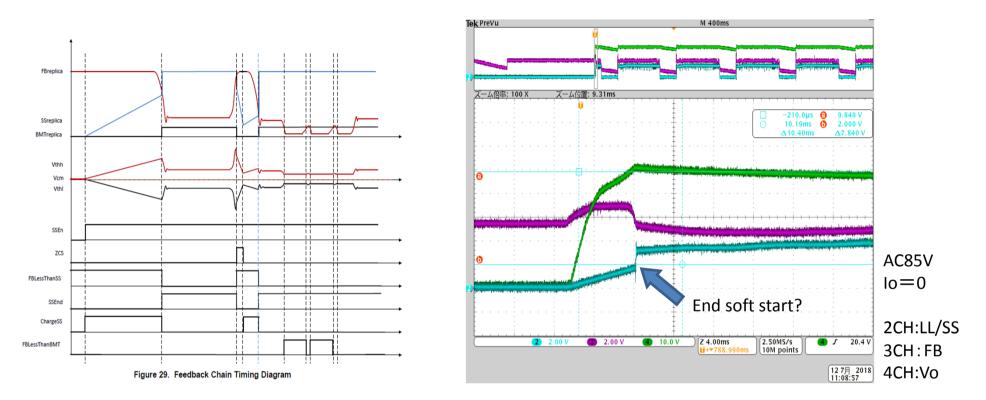

## ① About soft start

Looking at the above timing of the data sheet, SSEnd goes High when Ssreplica becomes higher than FBReplica. Soft start has ended at this time. 1 Ssreplica = LL/SS Voltage Fbreplica = FB Voltage Is this correct?

2 The upper waveform (under evaluation) is FB> LL / SS. It seems that soft-start has ended.

Is the behavior of this waveform correct?

(I think it is different from the operation described in the data sheet.)

3 In addition, the sending start is over in the above part. Is this correct in your understanding?

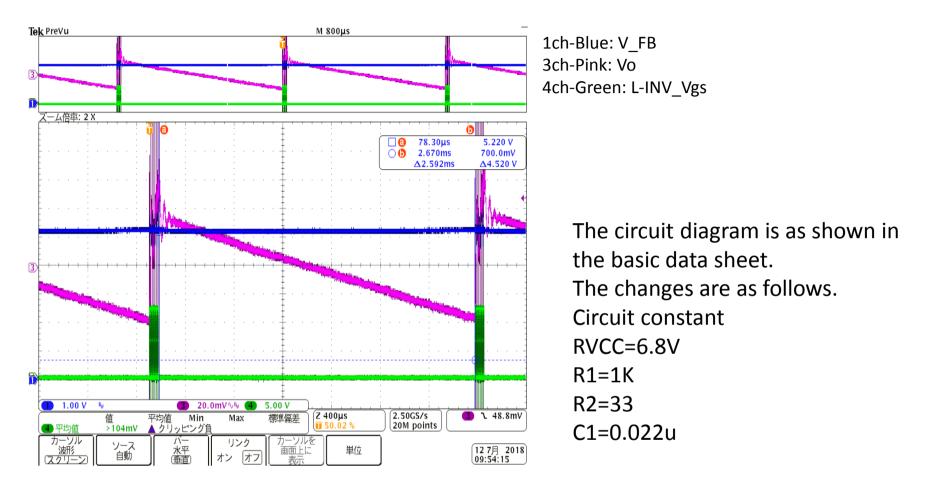

## 2 About burst mode threshold

The waveform is performing burst operation at no load.

RLLupper (Terminal Upper Resistance)=open.

VLL(Burst threshold voltage)=0.7V(min)

When the FB voltage falls below VLL, the burst operation starts.

State of FB voltage> 0.7 V. However, I think that the burst operation state.

why?

What is the reason for this?

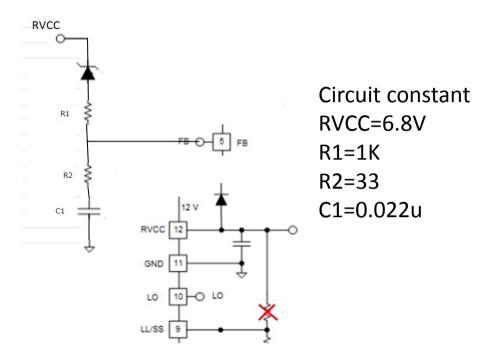

Circuit