2018.11.08

- As you guessed, it seems that the input gradual raise starts and enters the burst mode when boosting the PFC output. The reason for this is that VCC of UCC 28056 declines and enters UVLO protection and operation stops, so it was not in the original burst mode operation.

- In this operation, the PFC could not be started until the Vcc voltage recovered, it turned into a hunting rise and the stair-like PFC output increased.

- •This operation involves hunting activation of LLC output, there is a problem.

- As a countermeasure, it is necessary to increase the capacity of the RVCC line as suggested, and in order to avoid a decrease to the UVLO value of PFC\_IC it is necessary to have a capacitor capacity of 470  $\mu$ F, which is a severe situation in reality such as securing space.

- Also, since the power thermistor was short-circuited on the application on the PFC\_EVM board, we also checked the difference in the problem phenomenon due to the presence or absence of this line insertion, but there was no big difference and trouble occurred even in the line insertion state .

Below is a comparison defect waveform.

< Observation result of UCC 28056 \_ gradual increase start waveform >

- Gradually raised Start condition is measured by setting COMP terminal as remote control signal and PFC start as AC 80V.

- 1. Presence or absence of Vcc voltage drop and burst malfunction with varying VCC capacity of PFC

Test conditions : (Below both are LLC\_EVM (transformer modified), output setting: 5 V 0.3 A 12 V 0 A)

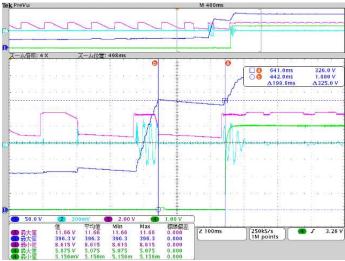

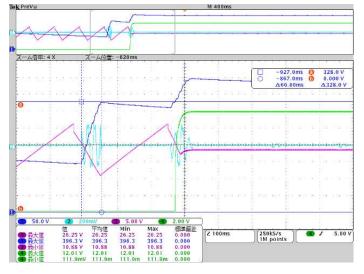

1-1. PFC\_C13 = 10  $\mu$  F (Default state) Although the level is low, there is hunting occurrence at 5 V output. Vcc is in a normal state.

- ① Blue : PFC\_Out [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(RVcc) [2V/div]

- ④ Green :5V\_out [1V/div] H:[100mS(400mS)/div]

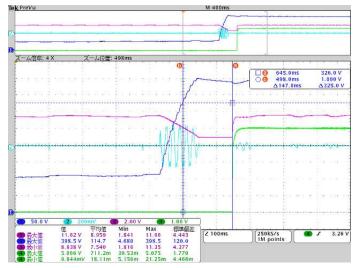

1-2.  $C_{13}=10+220=230 \,\mu$  F

- ① Blue : PFC\_Out [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(RVcc) [2V/div]

- ④ Green :5V\_out [1V/div] H:[100mS(400mS)/div]

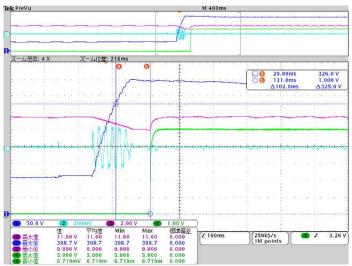

## 1-3. $C_{13}=10+470=480 \,\mu$ F Vcc Drop=9.9Vmin

- (1) Blue :  $PFC_Out$  [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(RVcc) [2V/div]

- ④ Green :5V\_out [1V/div] H:[100mS(400mS)/div]

- Evaluate the difference in PFC output rising waveform due to difference in activation timing of PFC Test conditions : (PFC : C13 capacity : Default state), (LLC\_EVM : Default item used)

Output setting : 12V 0.13A) At light load equivalent to the preceding paragraph. From the difference in PFC activation timing with the charge / discharge waveform of LLC - Vcc, a rising peak change of the starting initial voltage is observed.

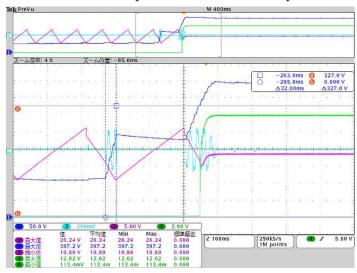

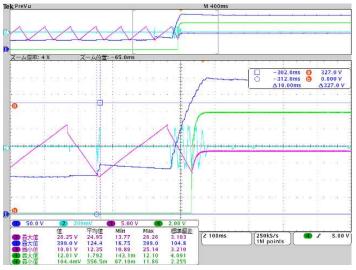

2-1. Vcc Immediately after the discharge starts up (12V output is hunting.)

- ① Blue : PFC\_Out [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(RVcc) [5V/div]

- ④ Green :12V\_out [2V/div] H:[100mS(400mS)/div]

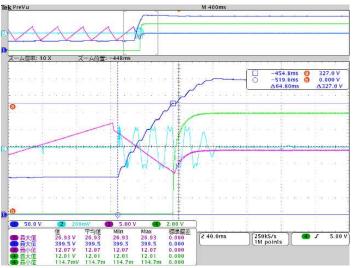

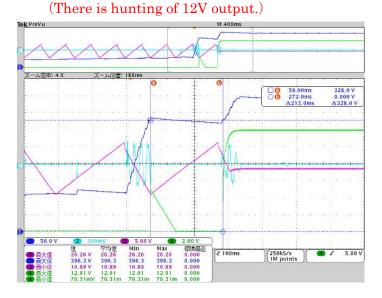

2-2. At the time of startup after a lapse of a little after the start of Vcc discharge (No output hunting)Although the PFC output rises in a stepwise manner, LLC does not reach the start detection value (about 328 V) at the first time.

- ① Blue: PFC\_Out [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(RVcc) [5V/div]

- ④ Green :12V\_out [2V/div] H:[100mS(400mS)/div]

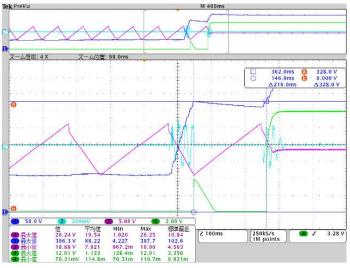

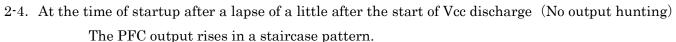

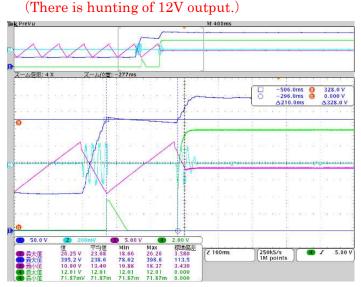

## 2-3. Vcc At the time of startup after a lapse of discharge (without output hunting.)

PFC output rises linearly

- ① Blue: PFC\_Out [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink : Vcc(RVcc) [5V/div]

- ④ Green :12V\_out [2V/div] H:[40mS(100mS)/div]

(1) Blue :  $PFC_Out$  [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(RVcc) [5V/div]

- ④ Green :12V\_out [2V/div] H:[100mS(400mS)/div]

- 2-5. At the time of activation just before switching to charging after Vcc discharge starts (No output hunting) The PFC output rises in a staircase pattern.

- ① Blue: PFC\_Out [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(RVcc) [5V/div]

- ④ Green :12V\_out [2V/div] H:[100mS(400mS)/div]

Comparison result with remodeled product : Even if LLC\_EVM in the default state is used, 12 V output hunting occurs depending on the PFC startup timing, which is not a problem caused by remodeling the evaluation  $board_{\circ}$

3. Comparison of startup characteristics depending on whether or not the power thermistor is mounted on the PFC output section

Other test conditions: same as above 2

3-1. power thermistor shorted

- 1 Blue: PFC\_Out [50V/div]

- ② Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(LLC) [5V/div]

- ④ Green: 12V\_out [2V/div] H:[100mS(400mS)/div]

## 3-2. Power Thermistor inserted

- ① Blue: PFC\_Out [50V/div]

- 2 Light blue: PFC\_Iin [2A/div]

- ③ Pink: Vcc(LLC) [5V/div]

- ④ Green: 12V\_out [2V/div] H:[100mS(400mS)/div]

Comparison result : It was not a malfunction due to the presence or absence of a power thermistor.