## 1 Introduction

The UCD92xx family of digital power controller supports a wide range of commands that allow an external host to configure, control, and monitor the controller. Communication between an UCD92xx controller and the host is via an I2C electrical interface using the PMBus command protocol.

The PMBus specification describes the command protocol in general terms. This document describes implementation details that are specific to the UCD92xx Digital Power Controllers.

## **Table of Contents:**

| 1   |              | duction                                    |           |

|-----|--------------|--------------------------------------------|-----------|

| 2   |              | Bus Specification                          |           |

| 3   | Data         | Formats                                    |           |

|     | 3.1          | Data Format for Output Voltage Parameters  |           |

|     | 3.2          | Data Format for Other Parameters           |           |

|     | 3.3          | Distinguishing Between Linear Data Formats |           |

|     | 3.4          | Translation, Quantization, and Truncation  |           |

| 4   |              | nory Model                                 |           |

| 5   |              | ring a Shutdown due to a Fault             |           |

| 6   |              | perature Warning and Fault Monitoring      |           |

| 7   |              | Iware Over-Current Fault Response          |           |

| 8   |              | t Response Address Support                 |           |

| 9   |              | ported PMBus Commands                      |           |

| 10  |              | ementation Details for PMBus Core Commands |           |

|     |              | (00h) PAGE                                 |           |

|     |              | (01h) OPERATION                            |           |

|     |              | (04h) PHASE                                |           |

|     | 10.4         | (11h) STORE_DEFAULT_ALL                    | 11        |

|     |              | (12h) RESTORE_DEFAULT_ALL                  |           |

|     | 10.6         | (20h) VOUT_MODE                            | 11        |

|     |              | (33h) FREQUENCY_SWITCH                     |           |

|     |              | (38h) IOUT_CAL_GAIN                        |           |

|     |              | (3Ah) FAN_CONFIG_1_2                       |           |

|     | 10.1         |                                            | 11<br>44  |

|     | 10.1         | \                                          |           |

|     | 10.1         |                                            |           |

|     | 10.1         |                                            |           |

|     | 10.1<br>10.1 | \                                          |           |

|     | 10.1         |                                            |           |

|     | 10.1         |                                            |           |

|     | 10.1         | • • • • • • • • • • • • • • • • • • • •    |           |

|     | 10.1         | ·                                          |           |

|     | 10.1         |                                            |           |

| 11  |              | ementation Details for User Data Commands  | ' '<br>11 |

| • • |              | (B0h) USER DATA 00                         |           |

|     |              | (B9h) SYNC CONFIG (USER DATA 09)           |           |

|     |              | (BAh) READ_AUX_ADCS (USER_DATA_10)         |           |

|     |              | (BBh) VID_CONFIG (USER_DATA_11)            |           |

|     |              | (BCh) VID_CODE_RAIL1 (USER_DATA_12)        |           |

|     |              | \\\\\\\\\\\                                | ٠.        |

|    | 11 C (DDb) VID     | CODE RAIL2 (USER DATA 13)                                                                | 4 4        |

|----|--------------------|------------------------------------------------------------------------------------------|------------|

|    |                    |                                                                                          |            |

|    |                    | CODE_RAIL3 (USER_DATA_14)                                                                |            |

|    |                    | _CODE_RAIL4 (USER_DATA_15)                                                               |            |

| 12 |                    | Details for Manufacturer-Specific Commands                                               |            |

|    |                    | Q_TIMEOUT (MFR_SPECIFIC_00)                                                              |            |

|    |                    | JT_CAL_MONITOR (MFR_SPECIFIC_01)                                                         |            |

|    |                    | SE_INFO (MFR_SPECIFIC_02)                                                                |            |

|    |                    | _SCALE_MONITOR (MFR_SPECIFIC_03)                                                         |            |

|    |                    | _BANK (MFR_SPECIFIC_04)                                                                  |            |

|    | 12.6 (D5h) CLA     | _GAINS (MFR_SPECIFIC_05)                                                                 | 11         |

|    |                    | E_ISOLATED (MFR_SPECIFÍC_06) (UCD9220, '9240, '9211, '9212)                              |            |

|    |                    | VER_CONFIG (MFR_SPECIFIC_06) (UCD9224, '9246, '9248, '9244)                              |            |

|    | 12.9 (D7h) EAD     | C_SAMPLE_TRIGGER (MFR_SPECIFIC_07)                                                       |            |

|    | 12.10              | (D8h) ACTIVATE_CLA_BANK (MFR_SPECIFIC_08)                                                | 11         |

|    | 12.11              | (D9h) ROM MODE (MFR SPECIFIC 09)                                                         | 11         |

|    | 12.12              | (DAh) USER_RAM_00 (MFR_SPECIFIC_10)                                                      | 11         |

|    | 12.13              | (DBh) SOFT_RESET (MFR_SPECIFIC_11)                                                       | 11         |

|    | 12.14              | (DCh) IIN_SCALE_MONITOR (MFR_SPECIFIC_12)                                                | 11         |

|    | 12.15              | (DDh) THERMAL_COEFF (MFR_SPECIFIC_13)                                                    |            |

|    | 12.16              | (DEh) PHASE_ENABLE (MFR_SPECIFIC_14)                                                     |            |

|    | 12.17              | (DFh) DRIVER_MIN_PULSE (MFR_SPECIFIC_15)                                                 | 11         |

|    | 12.18              | (E0h) MIN DUTY (MFR SPECIFIC 16)                                                         |            |

|    | 12.19              | (E1h) SYNC_IN_OUT (MFR_SPECIFIC_17)                                                      | 11         |

|    | 12.20              | (E2h) PARM_INFO (MFR_SPECIFIC_18)                                                        |            |

|    | 12.21              | (E3h) PARM VALUE (MFR SPECIFIC 19)                                                       |            |

|    | 12.22              | (E4h) TEMPERATURE CAL GAIN (MFR SPECIFIC 20)                                             |            |

|    | 12.23              | (E5h) TEMPERATURE CAL OFFSET (MFR SPECIFIC 21)                                           |            |

|    | 12.24              | (E6h) TRACKING SOURCE (MFR SPECIFIC 22)                                                  |            |

|    | 12.25              | (E7h) TRACKING_SCALE_MONITOR (MFR_SPECIFIC_23)                                           | 11         |

|    | 12.26              | (E8h) FAN SPEED FAULT LIMIT (MFR SPECIFIC 24)                                            |            |

|    | 12.27              | (E9h) LOGGED PEAKS (MFR SPECIFIC 25)                                                     |            |

|    | 12.28              | (EAh) LOGGED FAULTS (MFR SPECIFIC 26)                                                    |            |

|    | 12.29              | (EBh) LIGHT LOAD LIMIT HIGH (MFR SPECIFIC 27)                                            |            |

|    | 12.30              | (ECh) DEVICE_ID / ROM_VER (MFR_SPECIFIC_28)                                              |            |

|    |                    |                                                                                          |            |

|    | 12.31              | (EDh) LIGHT_LOAD_CONFIG (MFR_SPECIFIC_29)                                                |            |

|    | 12.32              | (EEh) PREBIAS_OFFSET (MFR_SPECIFIC_30)                                                   |            |

|    | 12.33              | (EFh) PREBIAS_GAIN (MFR_SPECIFIC_31)                                                     |            |

|    | 12.34              | (F0h) EXECUTE_FLASH (MFR_SPECIFIC_32)                                                    |            |

|    | 12.35              | (F1h) MFR_SETUP_PASSWORD (MFR_SPECIFIC_33)                                               |            |

|    | 12.36              | (F2h) DISABLE_SECURITY (MFR_SPECIFIC_34)                                                 |            |

|    | 12.37              | (F4h) MFR_SECURITY_BIT_MASK (MFR_SPECIFIC_36)                                            |            |

|    | 12.38              | (F3h) GPIO_SEQ_CONFIG (MFR_SPECIFIC_35)                                                  |            |

|    | 12.38.1<br>12.38.2 | First-Generation GPIO_SEQ_CONFIG (UCD9220 and '9240)                                     |            |

|    | 12.36.2            | (F5h) TEMP_BALANCE_IMIN (MFR_SPECIFIC_37)                                                |            |

|    | 12.40              | (F6h) LIGHT_LOAD_LIMIT_LOW (MFR_SPECIFIC_37)(F6h) LIGHT_LOAD_LIMIT_LOW (MFR_SPECIFIC_38) | 1 1<br>4 4 |

|    |                    |                                                                                          |            |

|    | 12.41              | (F7h) FAST_OC_FAULT_LIMIT (MFR_SPECIFIC_39)                                              | 1 1        |

|    | 12.42              | (F8h) POWER_GOOD_CONFIG (MFR_SPECIFIC_40) (UCD9222A, '9244A,                             |            |

|    | '9244N)            | 11 (FOb) Undefined (MED, CDECIFIC, 41)                                                   | 4 -        |

|    | 12.43              | (F9h) Undefined (MFR_SPECIFIC_41)                                                        |            |

|    | 12.44              | (FAh) PHASE_DROP_CAL (MFR_SPECIFIC_42)                                                   |            |

|    | 12.45              | (FBh) SYNC_OFFSET (MFR_SPECIFIC_43)                                                      |            |

|    | 12.46              | (FCh) EADC_TRIM (MFR_SPECIFIC_44)                                                        |            |

|    | 12.47              | (FCh) VID RESTART (MFR SPECIFIC 44) (UCD9222A, '9244A, '9244N)                           | 11         |

# Τi

|    | 12.48         | (FDh) DEVICE_ID (MFR_SPECIFIC_45)                                                       | . 11 |

|----|---------------|-----------------------------------------------------------------------------------------|------|

| 13 | Range Check   | ring and Limits                                                                         | . 11 |

| 14 | Usage: Assig  | ning DPWM Outputs to Phases and Pages                                                   | . 11 |

|    | 14.1 (D2h) Pi | HASE_INFO (MFR_SPECIFIC_02)                                                             | . 11 |

|    |               | Validity Checking:                                                                      |      |

|    | 14.1.2        |                                                                                         | 11   |

|    | 14.1.3        | Examples of Invalid Configurations                                                      | 11   |

| 15 | Usage: Settir | ng Control Law Accelerator Gains                                                        | . 11 |

|    | 15.1 (D4h) CI | _A_BANK (MFR_SPECIFIC_04)                                                               | . 11 |

|    | 15.2 (D5h) CI | _A_GAINS`(MFR_SPECIFIC_05)                                                              | . 11 |

|    |               | CTIVATE CLA BANK (MFR SPECIFIC 08)                                                      |      |

|    |               | age Examples                                                                            |      |

|    | 15.4.1        | Example 1: Writing and then Selecting the Run Mode CLA gains for Page 0                 |      |

|    | 15.4.2        | Example 2: Writing and then Selecting the Ramp Mode CLA gains for Page 2                |      |

|    | 15.4.3        | Example 3: Setting the CLA gains for Page 3 Directly to Hardware without Storing in RAM | .11  |

|    | 15.4.4        | Example 4: Swapping Between Active and Inactive Banks of Page 2 without Loading New     | ,    |

|    |               | Gains                                                                                   | 11   |

|    | 15.5 AFE Ga   | n 11                                                                                    |      |

|    | 15.6 Non-Line | ear EADC Gains                                                                          | . 11 |

| 16 | Glossary      |                                                                                         | . 11 |

| 17 | Document Re   | evision History                                                                         | . 11 |

## 2 PMBus Specification

This document makes frequent mention of the PMBus specification. Specifically, this document is "PMBus Power System Management Protocol Specification Part II – Command Language", Revision 1.1, dated 5 February 2007. The specification is published by the Power Management Bus Implementers Forum and is available from <a href="http://pmbus.org">http://pmbus.org</a>.

#### 3 Data Formats

Sections 7 and 8 of the PMBus standard provides for a number of different data formats: three for parameters related to output voltage and two for all other commands. Each PMBus device is expected to support only one of these formats.

#### 3.1 Data Format for Output Voltage Parameters

For parameters related to output voltage, the UCD92xx supports the Linear format defined in Section 8.3.1 of the PMBus specification. The linear format uses a 16-bit unsigned mantissa for each parameter, along with an exponent that is shared by all the voltage-related parameters. The exponent is reported in the bottom 5 bits of the VOUT\_MODE parameter. In the UCD92xx, this exponent is a read-only parameter whose value is fixed at -12. This allows setting voltage-related variables over a range from 0 to 15.9997V, with a resolution of 0.244mV.

The voltage value is calculated using the equation

Voltage =  $V * 2^X$ ,

where

Voltage is the parameter of interest, in volts,

V is a 16-bit unsigned binary integer mantissa, and

X is the signed 5-bit twos-complement binary integer exponent from VOUT MODE.

Exception: The PMBus standard assumes that all output voltages are expressed as positive numbers, so all parameters related to output voltage are unsigned integers, with a few notable exceptions. The VOUT\_CAL\_OFFSET and VOUT\_CAL\_MONITOR values are intended for making fine adjustments to the output voltage, and may take on small negative values. As such, these parameters are treated as signed twos-complement binary integers.

#### 3.2 Data Format for Other Parameters

For parameters not directly related to output voltage, the UCD92xx supports the Linear Data Format described in section 7.1 of the PMBus specification. This linear format is a two-byte value that contains an 11-bit, twos-complement mantissa and a 5-bit, twos-complement exponent.

The relationship between the PMBus parameter and the "real world" value is given by the formula:

$R = Y * 2^X$ .

Where

R is the "real world" value,

Y is an 11-bit, signed twos-complement binary integer mantissa, and

X is the signed 5-bit twos-complement binary integer exponent.

This pseudo floating point notation allows values as large as ~33E6 down to ~15E-6 to be sent over the PMBus. The internal variables used by the UCD92xx firmware are mostly 16 bits wide and do not support such a wide range of values. The resolution of a PMBus setting depends strongly on both the exponent of the PMBus value (larger values have coarser resolution) and the scaling of the internal variables.

## 3.3 Distinguishing Between Linear Data Formats

The PMBus specification uses the same term, "Linear", to describe both the 16-bit+exponent format used for the voltage-related parameters as well as the 11-bit+exponent format used for other parameters. In cases where it is necessary to distinguish between these two data formats, this document will use the term LINEAR16 or LINEAR11.

#### 3.4 Translation, Quantization, and Truncation

The internal variables used by the UCD92xx are often scaled to take optimal advantage of the hardware's native units such as ADC or DAC counts rather than volts or amperes. As a result, values that are written and read via PMBus must undergo mathematical translations. These translations, with their inherent quantization, may result in very slight differences between the setting that was written to the UCD92xx and the value that was later read back from it. This is normal and compliant, described in section 7.4 of the PMBus specification.

In some cases, a value written to the device may cause it to exceed the range of its internal variable. In some cases the device will report this as an error; in other cases it will saturate the variable at a safe value. In all cases, the value read back via the PMBus will reflect as accurately as possible the internal variable actually being used by the UCD92xx.

## 4 Memory Model

Section 6 of the PMBus specification describes the memory model for PMBus devices. Values used by the PMBus device are loaded into volatile Operating Memory from one of more of the following places.

Values hard coded into an IC design (if any),

Values programmed from hardware pins (if any),

A non-volatile memory called the Default Store (if supported in the device),

A non-volatile memory called the User Store (if supported in the device), or

Communications from the PMBus.

The UCD92xx contains RAM that is used as Operating Memory. On-board Data Flash memory is used to implement the hard-coded values and the Default Store values. Hard-coded values require a new firmware revision. Values in the Default Store may be changed using the STORE\_DEFAULT\_ALL command described in section 10.4. The User Store is not supported.

Section 6.1 of the PMBus specification describes the ordering of memory loading and precedence. In general, the hard-coded parameters are loaded into Operating Memory first. Second, any pin-programmable settings take effect. Third, values from the Default Store are loaded. Later, commands issued from the PMBus take effect. In all cases, an operation on a parameter will overwrite any prior value that was already in the Operating Memory.

# 5 Clearing a Shutdown due to a Fault

Section 10.7 of the PMBus specification describes the conditions required to resume power conversion for a device or rail that has been shutdown due to a fault. One of these conditions is that a rail must be commanded to turn OFF and then ON before power conversion can resume. Rails that are configured to be "Always On" via the ON\_OFF\_CONFIG PMBus command will remain latched off. Toggling the CONTROL PIN or OPERATION command will not clear the latched state. These rails can only be enabled by device reset or by changing the ON\_OFF\_CONFIG command to allow the CONTROL PIN or OPERATION command to clear the latched state. The UCD9224, UCD9246 and UCD9248 devices also allow toggling a TURN\_ON dependent input for the rail to clear the latched state. However, toggling a STAY\_ON dependent input for the rail will not clear the latched state.

# 6 Temperature Warning and Fault Monitoring

The external temperature sensors are used for temperature warning and fault detection using the PMBus commands OT\_WARN\_LIMIT and OT\_FAULT\_LIMIT for all UCD92xx devices. The UCD9211 and UCD9212 devices will report an over-temperature warning if the internal temperature exceeds 85C.

# 7 Hardware Over-Current Fault Response

The UCD92xx device family has two forms of hardware assistance for over-current faults. The first is an external driver fault input pin and the second is a set of analog comparators that monitor the CS-1A, CS-2A, CS-3A and CS-4A input pins. The analog comparator threshold can be configured using the FAST\_OC\_FAULT\_LIMIT command described in this document.

Both types of hardware over-current detection use the IOUT\_OC\_FAULT\_RESPONSE\_CODE to configure how the UCD92xx device reacts when a hardware over-current fault event occurs with the exception that only the RETRY\_SETTING and DELAY\_TIME bits are valid. The RESPONSE bits are ignored because the UCD92xx device will always shut down the output Rail in response to a hardware over-current event.

# 8 Alert Response Address Support

The UCD92xx supports using the PMBALERT# line to notify the host of warning or fault conditions and also supports the Alert Response Address protocol with the following exception. The UCD92xx will not respond to its address on the PMBus or another Alert Response Address event when it loses arbitration during an Alert Response Address event. Any PMBus command will clear this state, even commands addressed to other devices. Subsequent commands and Alert Response Address events will be responded to normally.

# 9 Supported PMBus Commands

Table 1 lists the PMBus commands. Commands 00h through CFh are defined in the PMBus specification and are considered to be "core" commands that are standardized for all manufacturers and products. Commands D0h through FEh are manufacturer-specific and may be unique for each manufacturer and product.

Commands that are not supported by the UCD92xx are indicated in the Comments column.

Most commands support writing and reading. Exceptions are indicated in the Comments column.

The Data Format column indicates the format of the data:

| Byte              | 8-bit binary value. Refer to the PMBus specification for details for each command. |

|-------------------|------------------------------------------------------------------------------------|

| LINEAR16          | 16-bit Linear format used for output voltage parameters. Described in 3.1 above.   |

| LINEAR11          | 11-bit Linear format used parameters other than output voltage. Described in       |

| section 3.2 above |                                                                                    |

| n/a               | Command does not have a data field.                                                |

| String            | ASCII string. Described in section 22.2 of the PMBus specification.                |

| Byte Array        | A block of data in binary format.                                                  |

The Scope column indicates how each command is affected by the PAGE and PHASE settings.

| Common | This command does not depend on the PAGE or PHASE setting. | It is a common |

|--------|------------------------------------------------------------|----------------|

|        | variable used by all pages and phases.                                       |

|--------|------------------------------------------------------------------------------|

| PAGE   | This command applies to the page(s) set by the most recent PAGE command. See |

|        | section 10.1 below for details.                                              |

| PAGE & | This command applies to the phase(s) set by the most recent PHASE command.   |

| PHASE  | See section 10.3 below for details.                                          |

|        | All commands that depend on PHASE also depend on PAGE.                       |

**Table 1: PMBus Commands**

| Code        | Command Name         | Transaction Type                            | Data Format<br>[Units] | Scope  | Supported Models (Comments) |

|-------------|----------------------|---------------------------------------------|------------------------|--------|-----------------------------|

| 00h         | PAGE                 | R/W Byte                                    | Byte                   | Common | All                         |

| 01h         | OPERATION            | R/W Byte                                    | Byte                   | PAGE   | All                         |

| 02h         | ON_OFF_CONFIG        | R/W Byte                                    | Byte                   | PAGE   | All                         |

| 03h         | CLEAR_FAULTS         | Send byte                                   | n/a                    | Common | All (Write Only)            |

| 04h         | PHASE                | R/W Byte                                    | Byte                   | PAGE   | All                         |

| 05h         | PAGE_PLUS_WRITE      | Write Block                                 | n/a                    | Common | PMBus 1.2 (*1)              |

| 06h         | PAGE_PLUS_READ       | Block Write –<br>Block Read<br>Process Call | n/a                    | Common | 'PMBus 1.2 (*1)             |

| 07h-<br>0Fh | Reserved             |                                             |                        |        | NOT SUPPORTED               |

| 10h         | WRITE_PROTECT        | R/W Byte                                    | Byte                   |        | NOT SUPPORTED               |

| 11h         | STORE_DEFAULT_ALL    | Send byte                                   | n/a                    | Common | All                         |

| 12h         | RESTORE_DEFAULT_ALL  | Send byte                                   | n/a                    | Common | All                         |

| 13h         | STORE_DEFAULT_CODE   | Write Byte                                  | Byte                   |        | NOT SUPPORTED               |

| 14h         | RESTORE DEFAULT CODE | Write Byte                                  | Byte                   |        | NOT SUPPORTED               |

| 15h         | STORE USER ALL       | Send byte                                   | n/a                    | Common | NOT SUPPORTED               |

| 16h         | RESTORE_USER_ALL     | Send byte                                   | n/a                    | Common | NOT SUPPORTED               |

| 17h         | STORE USER CODE      | Write Byte                                  | Byte                   |        | NOT SUPPORTED               |

| 18h         | RESTORE USER CODE    | Write Byte                                  | Byte                   |        | NOT SUPPORTED               |

| 19h         | CAPABILITY           | R/W Byte                                    | Byte                   | Common | All (Read Only)             |

| 1Ah         | QUERY                | Block Write –<br>Block Read<br>Process Call | Byte                   | Common | NOT SUPPORTED               |

| 1Bh         | SMBALERT_MASK        | R/W Word                                    | Word                   | PAGE   | PMBus 1.2 (*1)              |

| 1Ch-<br>1Fh | Reserved             |                                             |                        |        | NOT SUPPORTED               |

| 20h         | VOUT_MODE            | R/W Byte                                    | LINEAR16 [V]           | PAGE   | All (Read Only)             |

| 21h         | VOUT COMMAND         | R/W Word                                    | LINEAR16 [V]           | PAGE   | All                         |

| 22h         | VOUT TRIM            | R/W Word                                    | LINEAR16 [V]           | PAGE   | '9211, '9212                |

| 23h         | VOUT CAL OFFSET      | R/W Word                                    | LINEAR16 [V]           | PAGE   | All                         |

| 24h         | VOUT MAX             | R/W Word                                    | LINEAR16 [V]           | PAGE   | All                         |

| 25h         | VOUT_MARGIN_HIGH     | R/W Word                                    | LINEAR16 [V]           | PAGE   | All                         |

| 26h         | VOUT_MARGIN_LOW      | R/W Word                                    | LINEAR16 [V]           | PAGE   | All                         |

| 27h         | VOUT_TRANSITION_RATE | R/W Word                                    | LINEAR11<br>[V/ms]     | PAGE   | All                         |

| 28h         | VOUT DROOP           | R/W Word                                    | LINEAR16 [V]           | PAGE   | NOT SUPPORTED               |

| 29h         | VOUT_SCALE_LOOP      | R/W Word                                    | LINEAR11<br>[V/V]      | PAGE   | All                         |

| 2Ah         | VOUT_SCALE_MONITOR   | R/W Word                                    | LINEAR11<br>[V/V]      | PAGE   | All                         |

| 2Bh-<br>2Fh | Reserved             |                                             |                        |        | NOT SUPPORTED               |

| 30h         | COEFFICIENTS         | Block Write –<br>Block Read<br>Process Call | Byte Array             | PAGE   | NOT SUPPORTED               |

| 31h         | POUT MAX             | R/W Word                                    | LINEAR11 [W]           | PAGE   | NOT SUPPORTED               |

| Code       | Command Name                               | Transaction Type     | Data Format<br>[Units]         | Scope           | Supported Models (Comments)    |

|------------|--------------------------------------------|----------------------|--------------------------------|-----------------|--------------------------------|

| 32h        | MAX_DUTY                                   | R/W Word             | LINEAR11<br>[0-100%]           | PAGE            | All except '9224, '9246, '9248 |

| 33h        | FREQUENCY_SWITCH                           | R/W Word             | LINEAR11<br>[kHz]              | PAGE            | All                            |

| 34h        | Reserved                                   |                      |                                |                 | NOT SUPPORTED                  |

| 35h        | VIN_ON                                     | R/W Word             | LINEAR11 [V]                   | Common          | All                            |

| 36h        | VIN_OFF                                    | R/W Word             | LINEAR11 [V]                   | Common          | All                            |

| 37h        | INTERLEAVE                                 | R/W Word             | Word                           | Common          | NOT SUPPORTED                  |

| 38h        | IOUT_CAL_GAIN                              | R/W Word             | LINEAR11 $[mV/A = m\Omega]$    | PAGE &<br>PHASE | All                            |

| 39h        | IOUT_CAL_OFFSET                            | R/W Word             | LINEAR11 [A]                   | PAGE &<br>PHASE | All                            |

| 3Ah        | FAN_CONFIG_1_2                             | R/W Byte             | Byte                           | Common          | '9220, 9240, '9246F            |

| 3Bh        | FAN_COMMAND_1                              | R/W Word             | LINEAR11 [%]                   | Common          | '9220, 9240, '9246F            |

| 3Ch        | FAN_COMMAND_2                              | R/W Word             | LINEAR11 [%]                   | Common          | NOT SUPPORTED                  |

| 3Dh        | FAN_CONFIG_3_4                             | R/W Byte             | Byte                           | Common          | NOT SUPPORTED                  |

| 3Eh        | FAN_COMMAND_3                              | R/W Word             | LINEAR11 [%]                   | Common          | NOT SUPPORTED                  |

| 3Fh        | FAN_COMMAND_4                              | R/W Word             | LINEAR11 [%]                   | Common          | NOT SUPPORTED                  |

| 40h        | VOUT_OV_FAULT_LIMIT                        | R/W Word             | LINEAR16 [V]                   | PAGE            | All                            |

| 41h        | VOUT_OV_FAULT_RESPONSE                     | R/W Byte             | Byte                           | PAGE            | All                            |

| 42h        | VOUT_OV_WARN_LIMIT                         | R/W Word             | LINEAR16 [V]                   | PAGE            | All                            |

| 43h        | VOUT_UV_WARN_LIMIT                         | R/W Word             | LINEAR16 [V]                   | PAGE            | All                            |

| 44h        | VOUT_UV_FAULT_LIMIT                        | R/W Word             | LINEAR16 [V]                   | PAGE            | All                            |

| 45h        | VOUT_UV_FAULT_RESPONSE                     | R/W Byte             | Byte                           | PAGE            | All                            |

| 46h        | IOUT_OC_FAULT_LIMIT                        | R/W Word             | LINEAR11 [A]                   | PAGE            | All                            |

| 47h        | IOUT_OC_FAULT_RESPONSE                     | R/W Byte             | Byte                           | PAGE            | All                            |

| 48h        | IOUT_OC_LV_FAULT_LIMIT                     | R/W Word             | LÍNEAR16 [V]                   | PAGE            | All                            |

| 49h        | IOUT_OC_LV_FAULT_RESPONSE                  | R/W Byte             | Byte                           | PAGE            | All                            |

| 4Ah        | IOUT_OC_WARN_LIMIT                         | R/W Word             | LINEAR11 [A]                   | PAGE            | All                            |

| 4Bh        | IOUT_UC_FAULT_LIMIT                        | R/W Word             | LINEAR11 [A]                   | PAGE            | All                            |

| 4Ch        | IOUT_UC_FAULT_RESPONSE                     | R/W Byte             | Byte                           | PAGE            | All                            |

| 4Dh        | Reserved                                   |                      |                                |                 | NOT SUPPORTED                  |

| 4Eh        | Reserved                                   |                      |                                |                 | NOT SUPPORTED                  |

| 4Fh        | OT_FAULT_LIMIT                             | R/W Word             | LINEAR11 [℃]                   | PAGE            | All                            |

| 50h        | OT_FAULT_RESPONSE                          | R/W Byte             | Byte                           | PAGE            | All                            |

| 51h<br>52h | OT_WARN_LIMIT UT_WARN_LIMIT                | R/W Word             | LINEAR11 [°C]<br>LINEAR11 [°C] | PAGE<br>PAGE    | All                            |

|            |                                            |                      |                                |                 | NOT SUPPORTED                  |

| 53h        | UT_FAULT_LIMIT                             | R/W Word             | LINEAR11 [℃]                   | PAGE            | NOT SUPPORTED                  |

| 54h        | UT_FAULT_RESPONSE                          | R/W Byte             | Byte                           | PAGE            | NOT SUPPORTED                  |

| 55h        | VIN_OV_FAULT_LIMIT                         | R/W Word             | LINEAR11 [V]                   | Common          | All                            |

| 56h        | VIN_OV_FAULT_RESPONSE                      | R/W Byte             | Byte                           | Common          | All                            |

| 57h        | VIN_OV_WARN_LIMIT                          | R/W Word             | LINEAR11 [V]                   | Common          | All                            |

| 58h        | VIN_UV_WARN_LIMIT                          | R/W Word             | LINEAR11 [V]                   | Common          | All                            |

| 59h        | VIN_UV_FAULT_LIMIT                         | R/W Word             | LINEAR11 [V]                   | Common          | All                            |

| 5Ah        | VIN_UV_FAULT_RESPONSE                      | R/W Byte             | Byte                           | Common          | All                            |

| 5Bh        | IIN_OC_FAULT_LIMIT                         | R/W Word             | LINEAR11 [A]                   | PAGE            | NOT SUPPORTED                  |

| 5Ch        | IIN_OC_FAULT_RESPONSE                      | R/W Byte             | Byte                           | PAGE            | NOT SUPPORTED                  |

| 5Dh        | IIN_OC_WARN_LIMIT                          | R/W Word             | LINEAR11 [A]                   | PAGE            | NOT SUPPORTED                  |

| 5Eh        | POWER_GOOD_ON                              | R/W Word             | LINEAR16 [V]                   | PAGE            | All                            |

| 5Fh        | POWER_GOOD_OFF                             | R/W Word             | LINEAR16 [V]                   | PAGE            | All                            |

| 60h        | TON_DELAY                                  | R/W Word             | LINEAR11 [ms]                  | PAGE            | All                            |

| 61h        | TON_RISE TON MAX FAULT LIMIT               | R/W Word<br>R/W Word | LINEAR11 [ms]                  | PAGE<br>PAGE    | All                            |

| 62h        | TON_MAX_FAULT_LIMIT TON_MAX_FAULT_RESPONSE | R/W Word             |                                | PAGE            | All                            |

| 63h        |                                            |                      | Byte                           |                 |                                |

| 64h        | TOFF_DELAY                                 | R/W Word             | LINEAR11 [ms]                  | PAGE            | All                            |

| 65h        | TOFF_FALL                                  | R/W Word<br>R/W Word | LINEAR11 [ms]                  | PAGE            | All                            |

| 66h        | TOFF_MAX_WARN_LIMIT                        | n/vv vvora           | LINEAR11 [ms]                  | PAGE            |                                |

| 67h        | Reserved POUT OP FAULT LIMIT               | D/M//M/~J            | LINEAD14 DAG                   | DACE            | NOT SUPPORTED                  |

|            | I FOUL OF FAULT LIMIT                      | R/W Word             | LINEAR11 [W]                   | PAGE            | NOT SUPPORTED                  |

| 68h<br>69h | POUT OP FAULT RESPONSE                     | R/W Byte             | Byte                           | PAGE            | NOT SUPPORTED                  |

| Code         | Command Name                        | Transaction Type      | Data Format [Units]   | Scope           | Supported Models (Comments)                                |

|--------------|-------------------------------------|-----------------------|-----------------------|-----------------|------------------------------------------------------------|

| 6Bh          | PIN_OP_WARN_LIMIT                   | R/W Word              | LINEAR11 [W]          | Common          | NOT SUPPORTED                                              |

| 6Ch-<br>77h  | Reserved                            |                       |                       |                 | NOT SUPPORTED                                              |

| 78h          | STATUS_BYTE                         | R/W Byte              | Byte                  | Common          | All (Read Only, *2)                                        |

| 79h          | STATUS_WORD                         | R/W Word              | Word                  | Common          | All (Read Only, *2)                                        |

| 7 <b>A</b> h | STATUS_VOUT                         | R/W Byte              | Bye                   | PAGE            | All (Read Only, *2)                                        |

| 7Bh          | STATUS_IOUT                         | R/W Byte              | Byte                  | PAGE            | All (Read Only, *2)                                        |

| 7Ch          | STATUS_INPUT                        | R/W Byte              | Byte                  | PAGE            | All (Read Only, *2)                                        |

| 7Dh          | STATUS_TEMPERATURE                  | R/W Byte              | Byte                  | PAGE            | All (Read Only, *2)                                        |

| 7Eh          | STATUS_CML                          | R/W Byte              | Byte                  | Common          | All (Read Only, *2)                                        |

| 7Fh          | STATUS_OTHER                        | R/W Byte              | Byte                  | Common          | All (Read Only, *2)                                        |

| 80h<br>81h   | STATUS_MFR_SPECIFIC STATUS_FANS_1_2 | R/W Byte              | Byte<br>Byte          | PAGE<br>Common  | All (Read Only, *2)<br>'9220, '9240, '9246F                |

| 82h          | STATUS_FANS_3_4                     | R/W Byte              | Byte                  | Common          | (Read Only, *2)<br>'9220, '9240, '9246F<br>(Read Only, *2) |

| 83h-         |                                     |                       | 2,10                  |                 | Always returns 0x00 NOT SUPPORTED                          |

| 87h          | Reserved                            |                       |                       |                 |                                                            |

| 88h          | READ_VIN                            | R/W Word              | LINEAR11 [V]          | Common          | All (Read Only)                                            |

| 89h          | READ_IIN                            | R/W Word              | LINEAR11 [A]          | Common          | All except '9244<br>variants (Read Only)                   |

| 8Ah          | READ_VCAP                           | R/W Word              | LINEAR16 [V]          | PAGE            | NOT SUPPORTED                                              |

| 8Bh          | READ_VOUT                           | R/W Word              | LINEAR16 [V]          | PAGE            | All (Read Only)                                            |

| 8Ch          | READ_IOUT                           | R/W Word              | LINEAR11 [A]          | PAGE &<br>PHASE | All (Read Only)                                            |

| 8Dh          | READ_TEMPERATURE_1                  | R/W Word              | LINEAR11 [℃]          | Common          | All (Read Only)                                            |

| 8Eh          | READ_TEMPERATURE_2                  | R/W Word              | LINEAR11 [℃]          | PAGE &<br>PHASE | All (Read Only)                                            |

| 8Fh          | READ_TEMPERATURE_3                  | R/W Word              | LINEAR11 [℃]          | Common          | NOT SUPPORTED                                              |

| 90h          | READ_FAN_SPEED_1                    | R/W Word              | LINEAR11<br>[RPM]     | Common          | '9220, '9240, '9246F<br>(Read Only)                        |

| 91h          | READ_FAN_SPEED_2                    | R/W Word              | LINEAR11<br>[RPM]     | Common          | NOT SUPPORTED                                              |

| 92h          | READ_FAN_SPEED_3                    | R/W Word              | LINEAR11<br>[RPM]     | Common          | NOT SUPPORTED                                              |

| 93h          | READ_FAN_SPEED_4                    | R/W Word              | LINEAR11<br>[RPM]     | Common          | NOT SUPPORTED                                              |

| 94h          | READ_DUTY_CYCLE                     | R/W Word              | LINEAR11 [0-<br>100%] | PAGE            | All (Read Only)                                            |

| 95h          | READ_FREQUENCY                      | R/W Word              | LINEAR11<br>[kHz]     | PAGE            | NOT SUPPORTED                                              |

| 96h          | READ_POUT                           | R/W Word              | LINEAR11 [W]          | PAGE            | All (Read Only)                                            |

| 97h          | READ_PIN                            | R/W Word              | LINEAR11 [W]          | Common          | All except '9244<br>variants (Read Only)                   |

| 98h          | PMBUS_REVISION                      | R/W Byte              | Byte                  | Common          | All (Read Only)                                            |

| 99h          | MFR_ID                              | R/W block<br>18 bytes | String                | Common          | All                                                        |

| 9Ah          | MFR_MODEL                           | R/W block<br>12 bytes | String                | Common          | All                                                        |

| 9Bh          | MFR_REVISION                        | R/W block<br>12 bytes | String                | Common          | All                                                        |

| 9Ch          | MFR_LOCATION                        | R/W block<br>12 bytes | String                | Common          | All                                                        |

| 9Dh          | MFR_DATE                            | R/W block<br>6 bytes  | String                | Common          | All                                                        |

| 9Eh          | MFR_SERIAL                          | R/W block<br>12 bytes | String                | Common          | All                                                        |

| 9Fh          | Reserved                            | ·                     |                       |                 |                                                            |

| A0h          | MFR_VIN_MIN                         | R/W Word              | LINEAR11 [V]          | Common          | NOT SUPPORTED                                              |

| A1h          | MFR_VIN_MAX                         | R/W Word              | LINEAR11 [V]          | Common          | NOT SUPPORTED                                              |

| A2h          | MFR_IIN_MAX                         | R/W Word              | LINEAR11 [A]          | Common          | NOT SUPPORTED                                              |

| Code        | Command Name                           | Transaction<br>Type       | Data Format<br>[Units] | Scope          | Supported Models (Comments)                                               |

|-------------|----------------------------------------|---------------------------|------------------------|----------------|---------------------------------------------------------------------------|

| A3h         | MFR PIN MAX                            | R/W Word                  | LINEAR11 [W]           | Common         | NOT SUPPORTED                                                             |

| A4h         | MFR VOUT MIN                           | R/W Word                  | LINEAR11 [V]           | Common         | NOT SUPPORTED                                                             |

| A5h         | MFR VOUT MAX                           | R/W Word                  | LINEAR11 [V]           | Common         | NOT SUPPORTED                                                             |

| A6h         | MFR_IOUT_MAX                           | R/W Word                  | LINEAR11 [A]           | PAGE           | NOT SUPPORTED                                                             |

| A7h         | MFR POUT MAX                           | R/W Word                  | LINEAR11 [W]           | Common         | NOT SUPPORTED                                                             |

| A8h         | MFR_TAMBIENT_MAX                       | R/W Word                  | LINEAR11 [°C]          | Common         | NOT SUPPORTED                                                             |

| A9h         | MFR_TAMBIENT_MIN                       | R/W Word                  | LINEAR11 [°C]          | Common         | NOT SUPPORTED                                                             |

|             |                                        |                           |                        |                |                                                                           |

| AAh         | MFR_EFFICIENCY_LL                      | R/W Word                  | LINEAR11 [%]           | Common         | NOT SUPPORTED                                                             |

| ABh         | MFR_EFFICIENCY_LL                      | R/W Word                  | LINEAR11 [%]           | Common         | NOT SUPPORTED                                                             |

| ACh         | MFR_EFFICIENCY_PIN                     | R/W Word                  | LINEAR11 [%]           | Common         | NOT SUPPORTED                                                             |

| ADh         | IC_DEVICE_ID                           | Read Block<br>10-11 bytes | String                 | Common         | PMBus 1.2 (*1),<br>Read Only                                              |

| AEh         | IC_DEVICE_REV                          | Read Block<br>16-20 bytes | String                 | Common         | PMBus 1.2 (*1),<br>Read Only                                              |

| AFh         | Reserved                               | -                         |                        |                | NOT SUPPORTED                                                             |

| B0h         | USER_DATA_00                           | R/W Block                 | String                 | Common         | All except '9220,                                                         |

| DUII        | USER_DATA_00                           | 32 bytes                  | String                 | Common         | <sup>'</sup> 9240,                                                        |

| B1h         | STATISTICS_VALUES (USER_DATA_01)       | R/W Block<br>16 bytes     | Byte Array             | Common         | '9211, '9212                                                              |

| B2h         | STATISTICS_MAXMIN (USER_DATA_02)       | R/W Block<br>32 bytes     | Byte Array             | Common         | '9211, '9212                                                              |

| B3h         | BLACKBOX_VALUES (USER_DATA_03)         | R/W Block<br>20 bytes     | Byte Array             | Common         | '9211, '9212                                                              |

| B4h         | BLACKBOX_MAXMIN (USER_DATA_04)         | R/W Block<br>32 bytes     | Byte Array             | Common         | '9211, '9212                                                              |

| B5h         | FAULT_EVENT_CONTROL<br>(USER_DATA_05)  | R/W Word                  | Word                   | Common         | '9211, '9212                                                              |

| B6h-<br>B8h |                                        |                           |                        |                |                                                                           |

| B9h         | SYNC_CONFIG (USER_DATA_09)             | R/W Block<br>9 bytes      | Byte Array             | Common         | '9222, '9244                                                              |

| BAh         | READ_AUX_ADCS (USER_DATA_10)           | Read Block<br>9 bytes?    | Byte Array             | Common         | '9222, '9244                                                              |

| BBh         | VID_CONFIG (USER_DATA_11)              | R/W Block<br>8 bytes?     | Byte Array             | PAGE           | '9222, '9244                                                              |

| BCh         | VID_CODE_RAIL1 (USER_DATA_12)          | R/W Byte                  | Byte                   | Common         | '9222, '9244                                                              |

| BDh         | VID_CODE_RAIL2 (USER_DATA_13)          | R/W Byte                  | Byte                   | Common         | '9222, '9244                                                              |

| BEh         | VID_CODE_RAIL3 (USER_DATA_14)          | R/W Byte                  | Byte                   | Common         | <sup>'</sup> 9244                                                         |

| BFh         | VID CODE RAIL4 (USER DATA 15)          | R/W Byte                  | Byte                   | Common         | <sup>'</sup> 9244                                                         |

| C0h-<br>CFh | Reserved                               |                           |                        |                | NOT SUPPORTED                                                             |

| D0h         | SEQ_TIMEOUT (MFR_SPECIFIC_00)          | R/W Word                  | LINEAR11 [ms]          | PAGE           | '9220, '9240,<br>'9224, '9246, '9248<br>'9246F, '9224E,<br>'9246E, '9248E |

| D1h         | VOUT_CAL_MONITOR<br>(MFR_SPECIFIC_01)  | R/W Word                  | LINEAR16 [V]           | PAGE           | All                                                                       |

| D2h         | PHASE_INFO (MFR_SPECIFIC_02)           | R/W block<br>4 bytes      | Byte Array             | Common         | All                                                                       |

| D3h         | VIN_SCALE_MONITOR<br>(MFR_SPECIFIC_03) | R/W Word                  | LINEAR11<br>[V/V]      | Common         | All                                                                       |

| D4h         | CLA_BANK (MFR_SPECIFIC_04)             | R/W Byte                  | Byte                   |                | All                                                                       |

| D5h         | CLA_GAINS (MFR_ SPECIFIC_05)           | R/W Block<br>16 bytes     | Byte Array             | PAGE &<br>BANK | All                                                                       |

| D6h         | PAGE_ISOLATED (MFR_SPECIFIC_06)        | R/W Byte                  | Byte                   | PAGE           | '9220, '9240<br>'9211, '9212                                              |

|             | DRIVER_CONFIG (MFR_SPECIFIC_06)        | R/W Byte                  | Byte                   | PAGE           | All others                                                                |

| D7h         | EADC_SAMPLE_TRIGGER (MFR_SPECIFIC_07)  | R/W Word                  | LÍNEAR11<br>[ns]       | PAGE           | All                                                                       |

| D8h         | ACTIVATE_CLA_BANK<br>(MFR_SPECIFIC_08) | R/W Byte                  | Byte                   | PAGE           | All                                                                       |

| D9h         | ROM_MODE (MFR_SPECIFIC_09)             | Send Byte                 | n/a                    | Common         | All                                                                       |

| DAh         | USER_RAM_00 (MFR_SPECIFIC_10)          | R/W Byte                  | Byte                   | Common         | All                                                                       |

| Code | Command Name                                | Transaction Type                           | Data Format [Units]                         | Scope           | Supported Models (Comments)                              |

|------|---------------------------------------------|--------------------------------------------|---------------------------------------------|-----------------|----------------------------------------------------------|

| DBh  | SOFT_RESET (MFR_SPECIFIC_11)                | Send Byte                                  | n/a                                         | Common          | All                                                      |

| DCh  | IIN_SCALE_MONITOR (MFR_SPECIFIC_12)         | R/W Word                                   | LINEAR11<br>[V/A]                           | Common          | All except '9244 variants                                |

| DDh  | THERMAL_COEF (MFR_SPECIFIC_13)              | R/W Word                                   | LINEAR11<br>[%/℃]                           | PAGE            | All                                                      |

| DEh  | PHASE_ENABLE (MFR_SPECIFIC_14)              | R/W Byte                                   | Byte                                        | PAGE            | All                                                      |

| DFh  | DRIVER_MIN_PULSE (MFR_SPECIFIC_15)          | R/W Word                                   | LINEAR11 [ns]                               | PAGE            | All                                                      |

| E0h  | MIN_DUTY (MFR_SPECIFIC_16)                  | R/W Word                                   | LINEAR11 [0-<br>100%]                       | PAGE            | '9220, '9240<br>'9211, '9212                             |

| E1h  | SYNC_IN_OUT (MFR_SPECIFIC_17)               | R/W Word                                   | 2 Bytes                                     | Common          | All except '9222,<br>'9244                               |

| E2h  | PARM_INFO (MFR_SPECIFIC_18)                 | R/W block<br>5 bytes                       | Byte Array                                  | Common          | All                                                      |

| E3h  | PARM_VALUE (MFR_SPECIFIC_19)                | R/W block                                  | Byte Array                                  | Common          | All                                                      |

| E4h  | TEMPERATURE_CAL_GAIN<br>(MFR_SPECIFIC_20)   | R/W Word                                   | LINEAR11<br>[°C/V]                          | PAGE &<br>PHASE | All                                                      |

| E5h  | TEMPERATURE_CAL_OFFSET (MFR_SPECIFIC_21)    | R/W Word                                   | LINEAR11 [℃]                                | PAGE &<br>PHASE | All                                                      |

| E6h  | TRACKING_SOURCE<br>(MFR_SPECIFIC_22)        | R/W Byte                                   | Byte                                        | PAGE            | All ('9244 variants support only internal tracking)      |

| E7h  | TRACKING_SCALE_MONITOR<br>(MFR_SPECIFIC_23) | R/W Word                                   | LINEAR11<br>[V/V]                           | PAGE            | All                                                      |

| E8h  | FAN_SPEED_FAULT_LIMIT<br>(MFR_SPECIFIC_24)  | R/W Word                                   | LINEAR11<br>[RPM]                           | Common          | '9220, '9240, '9246F                                     |

| E9h  | LOGGED_PEAKS (MFR_SPECIFIC_25)              | R/W Block<br>17 bytes                      | Byte Array<br>Byte [°C] and<br>LINEAR11 [A] | Common          | All                                                      |

| EAh  | LOGGED_FAULTS (MFR_SPECIFIC_2               | R/W Block<br>9 bytes                       | Byte Array                                  | Common          | All                                                      |

| EBh  | LIGHT_LOAD_LIMIT_HIGH<br>(MFR_SPECIFIC_27)  | R/W Word                                   | LINEAR11 [A]                                | PAGE            | All                                                      |

| ECh  | DEVICE_ID / ROM_VER<br>(MFR_SPECIFIC_28)    | Read block<br>4 bytes or up<br>to 32 bytes | Byte Array or<br>String                     | Common          | All (Read Only)                                          |

| EDh  | LIGHT_LOAD_CONFIG<br>(MFR_SPECIFIC_29)      | R/W Byte                                   | Byte                                        | PAGE            | All                                                      |

| EEh  | PREBIAS_OFFSET                              | R/W Word                                   | LINEAR11 [%]                                | PAGE            | '9220, '9240                                             |

| EFh  | PREBIAS_GAIN                                | R/W Word                                   | LINEAR11<br>[%/%]                           | PAGE            | '9220, '9240                                             |

| F0h  | EXECUTE_FLASH (MFR_SPECIFIC_32)             | Send Byte                                  | n/a                                         | Common          | All (Write Only)                                         |

| F1h  | MFR_SETUP_PASSWORD<br>(MFR_SPECIFIC_33)     | R/W Block<br>6 bytes                       | Binary Array                                | Common          | All                                                      |

| F2h  | DISABLE_SECURITY (MFR_SPECIFIC_34)          | R/W Block<br>6 bytes                       | Binary Array                                | Common          | All                                                      |

| F3h  | GPIO_SEQ_CONFIG (MFR_SPECIFIC_35)           | R/W Block<br>29 bytes                      | Binary Array                                | Common          | '9220, '9240                                             |

|      | GPIO_SEQ_CONFIG (MFR_SPECIFIC_35)           | R/W Block<br>32 bytes                      | Binary Array                                | Common          | '9224, '9246, '9248<br>'9246F, '9224E,<br>'9246E, '9248E |

| F4h  | MFR_SECURITY_BIT_MASK (MFR_SPECIFIC_36)     | R/W Block<br>32 bytes                      | Binary Array                                | Common          | All                                                      |

| F5h  | TEMP_BALANCE_IMIN<br>(MFR_SPECIFIC_37)      | R/W Word                                   | LINEAR11 [A]                                | PAGE            | All except '9211, '9222, '9244                           |

| F6h  | LIGHT_LOAD_LIMIT_LOW<br>(MFR_SPECIFIC_38)   | R/W Word                                   | LINEAR11 [A]                                | PAGE            | All                                                      |

| F7h  | FAST_OC_FAULT_LIMIT<br>(MFR_SPECIFIC_39)    | R/W Word                                   | LINEAR11 [A]                                | PAGE            | All                                                      |

| F8h  | POWER_GOOD_CONFIG<br>(MFR_SPECIFIC_40)      | R/W Byte                                   | Byte                                        | Common          | '9222A, '9244A,<br>'9244N                                |

| F9h  | (MFR_SPECIFIC_41)                           |                                            |                                             |                 | NOT SUPPORTED                                            |

| Code | Command Name                     | Transaction Type             | Data Format [Units]                     | Scope  | Supported Models (Comments)                              |

|------|----------------------------------|------------------------------|-----------------------------------------|--------|----------------------------------------------------------|

| FAh  | PHASE_DROP_CAL (MFR_SPECIFIC_42) | R/W Word                     | LINEAR11<br>[Switching<br>cycles / Amp] | PAGE   | 'All except '9220,<br>'9240                              |

| FBh  | SYNC_OFFSET (MFR_SPECIFIC_43)    | R/W Word                     | LINEAR11 [ns]                           | PAGE   | '9224, '9246, '9248<br>'9246F, '9224E,<br>'9246E, '9248E |

|      | EADC_TRIM (MFR_SPECIFIC_44)      | R/W Byte                     | Byte                                    | PAGE   | '9220, '9240,                                            |

| FCh  | VID_RESTART (MFR_SPECIFIC_44)    | Send Byte                    | n/a                                     | PAGE   | '9222A,<br>'9244A, '9244N                                |

| FDh  | DEVICE_ID (MFR_SPECIFIC_45)      | Read Block<br>up to 32 bytes | String                                  | Common | All (Read Only)                                          |

| FEh  | Mfr_Specific_Extended_Command    |                              |                                         |        | NOT SUPPORTED                                            |

| FFh  | PMBUS_Extended_Command           |                              |                                         |        | NOT SUPPORTED                                            |

<sup>&</sup>lt;sup>1</sup> PMBus Revision 1.1 is supported by UD9220, '9240, '9211, '9212, '9224, '9246, '9248, and '9246F. PMBus Revision 1.2 is supported by 9224E, '9246E, '9248E, and all variants of '9222 and '9244.

<sup>&</sup>lt;sup>2</sup> STATUS\_xxx commands are read-only in PMBus revision 1.1 and are R/W in PMBus revision 1.2.

# 10 Implementation Details for PMBus Core Commands

These PMBus core commands are defined in the PMBus specification. This section describes details that are unique to the UCD92xx implementation.

#### 10.1 (00h) PAGE

The PAGE command provides the ability to configure, control, and monitor multiple outputs on one unit using a single PMBus physical address. All subsequent commands that depend on page will be applied to the rail selected by the PAGE command.

The Fusion Digital Power Designer software uses the term "Rail" to refer to a voltage output. Rails are numbered starting with one, while pages are numbered starting at zero. The relationship between the PMBus PAGE value and the Rail number is shown in Table 2.

Setting PAGE = 0xFF means that the following write command are to be applied to all outputs. A page setting of 0xFF is invalid for all read commands with scope of PAGE or PAGE & PHASE.

Table 2: Relationship between PAGE and Rail

| Page     | Output Rail |

|----------|-------------|

| 0        | 1           |

| 1*       | 2           |

| 2*       | 3           |

| 3*       | 4           |

| 4 – 0xFE | Invalid     |

| 0xFF     | All         |

(\*) The maximum number of rails on the UCD9240 is four. In some power supply configurations, multiple phases may be bridged together to increase the current capability. This may result in fewer than four independent rails. (Note that the UCD9220 only supports two rails and the UCD921x only supports one). The number of rails is configured using the PHASE\_INFO command, described in section 13 below.

Section 11.10 of the PMBus specification describes the PAGE command in more detail.

## 10.2 (01h) OPERATION

This command is used to turn outputs on and off in conjunction with input from the CONTROL pin. Section 12.1 of the PMBus specification describes this command in more detail.

The UCD92xx supports the following modes for the Operation command:

Immediate Off (No Sequencing)

Soft Off (With Sequencing)

On Nominal (No Margining)

On Margin High (Ignore Faults)

On Margin High (Act on Fault)

On Margin Low (Ignore Faults)

On Margin Low (Act on Fault)

The parameter is not stored in the Default Store in Data Flash.

## 10.3 (04h) PHASE

This command selects a specific phase on a multi-phase output rail. All subsequent commands that depend on phase will be applied to the phase(s) selected by the PHASE command.

The number of phases for each page may be determined from the PHASE\_INFO command (D2h) (see section 13 below). The phase numbering for each page starts at zero and goes up to one less than the number of phases on the selected page.

Setting PHASE = FF will cause subsequent write commands to be applied to all the phases on the selected page. Issuing a read command while PHASE = 0xFF has results that depend on the command.

| Command                | Response when PHASE = 0xFF for Read Commands                 |

|------------------------|--------------------------------------------------------------|

| READ_IOUT              | Returns total current for all phases on selected page.       |

| IOUT_CAL_GAIN          | Invalid Data                                                 |

| IOUT_CAL_OFFSET        | Invalid Data                                                 |

| READ_TEMPERATURE_2     | Returns highest temperature for all phases on selected page. |

| TEMPERATURE_CAL_GAIN   | Invalid Data                                                 |

| (MFR_SPECIFIC_20)      |                                                              |

| TEMPERATURE_CAL_OFFSET | Invalid Data                                                 |

| (MFR_SPECIFIC_21)      |                                                              |

## 10.4 (11h) STORE DEFAULT ALL

The STORE\_DEFAULT\_ALL command will save the PMBus parameters from Operating Memory into the Default Store in Data Flash. The UCD92xx will use the most recently written set of Default Store values at startup or after a RESTORE\_DEFAULT\_ALL command. If the Default Store has never been written, values from the hard-coded memory will be used. NOTE: The OPERATION and PHASE\_ENABLE parameters are not stored in the Default Store in Data Flash.

#### 10.5 (12h) RESTORE DEFAULT ALL

The RESTORE\_DEFAULT\_ALL command will restore the PMBus parameters from the Default Store into Operating Memory. If the Default Store has never been written, values from the hard-coded memory will be used.

**CAUTION**: If the RESTORE\_DEFAULT\_ALL command is issued while one or more voltage outputs are enabled, the output could behave erratically, with possibly catastrophic consequences.

#### 10.6 (20h) VOUT MODE

This command, described in sections 8.1 and 8.2 of the PMBus specification, indicates the data format used for all commands related to output voltage. In the UCD92xx, VOUT\_MODE is a read-only parameter that is fixed to use Linear data format (described in section 3.1 above), with a fixed scaling exponent of -12.

#### 10.7 (33h) FREQUENCY SWITCH

This command, described in sections 14.4 of the PMBus specification. All outputs must be OFF before this parameter can be written to the device. If any outputs are enabled the device will NACK writes to the FREQUENCY\_SWITCH command.

#### 10.8 (38h) IOUT CAL GAIN

This command, described in section 14.8 of the PMBus specification, is used to configure the gain of the current sense circuit. The units for this command are milliohms (mV/A).

Note that there is some ambiguity in Rev 1.1 of the PMBus specification. One sentence says that the command uses the *conductance* of the sense resistor, but a later sentence says that the resistance should be used. In one place the units are listed as ohms, but the default value is declared as 0 milliohms.

Rev 1.0 of the PMBus specification used resistance (not conductance) and milliohms. It is expected that Rev 1.2 will clear up this ambiguity and revert to the Rev 1.0 wording. In the UCD92xx firmware, the ambiguous language in Rev 1.1 is interpreted to have the same meaning as Rev 1.0 (i.e. milliohms).

#### 10.9 (3Ah) FAN CONFIG 1 2

This command, described in section 14.10 of the PMBus specification, is used to configure the fan controlled by the UCD9240. Note that UCD9220 and UCD921x do not have I/O pins to support a fan so this command is meaningless for those models.

The UCD9240 does not support all possible settings of FAN\_CONFIG\_1\_2. Notably, only Fan 1 is supported, not Fan 2. Writing any non-zero value to the Fan 2 controls (bits 3:0), will return a NACK due to Invalid Data.

In addition, Fan1 may only be commanded in Duty Cycle mode, not in RPM. Attempting to write a non-zero value to bit 6 will return a NACK due to Invalid Data.

| Bit(s) | Value | Meaning                                    |

|--------|-------|--------------------------------------------|

| 7      | 1     | A fan is installed in Position 1           |

|        | 0     | No fan is installed in Position 1          |

| 6      | 1     | Fan 1 is commanded in RPM. – NOT SUPPORTED |

|        | 0     | Fan 1 is commanded in Duty Cycle           |

| 5:4    | 0:3   | Fan 1 Tachometer Pulses Per Revolution     |

|        |       | 0= 1 pulse per revolution                  |

|        |       | 1= 2 pulses per revolution                 |

|        |       | 2= 3 pulses per revolution                 |

|        |       | 3= 4 pulses per revolution                 |

| 3:0    |       | Fan 2 commands – NOT SUPPORTED             |

## 10.10 (3Bh) FAN\_COMMAND\_1

This command, described in section 14.12 of the PMBus specification, is used to adjust the operation of Fan 1 controlled by the UCD9240. . Note that UCD9220 and UCD921x do not have I/O pins to support a fan so this command is meaningless for those models. The PMBus specification describes two ways of setting the fan command (RPM or Duty Cycle), but the UCD9240 only supports the Duty Cycle mode.

The command has two data bytes formatted in the Linear11 data format. The units are percent duty cycle, from 0 to 100%.

#### 10.11 (41h - 69h) xxx FAULT RESPONSE

The data bytes of the \_FAULT\_RESPONSE commands are described in sections 10.5.1 and 10.5.2 of the PMBus specification. In each case, bits 2:0 identify the number of delay time. The delay time is used for either the amount of time a unit is to continue operating after a fault is detected, or for the amount of time between attempts to restart. The units of the time delay, which vary depending on the type of fault, are shown in the table below.

| Code | Command                | Shutdown Delay Units | Retry Delay Units | Comment |

|------|------------------------|----------------------|-------------------|---------|

| 41h  | VOUT_OV_FAULT_RESPONSE | 5 ms                 | 5 ms              | Note 1  |

| 45h  | VOUT_UV_FAULT_RESPONSE | 5 ms                 | 5 ms              | Note 1  |

| 47h  | IOUT_OC_FAULT_RESPONSE | 5 ms                 | 5 ms              |         |

| 49h | IOUT_OC_LV_FAULT_RESPONSE | 5 ms    | 5 ms    | Note 1        |

|-----|---------------------------|---------|---------|---------------|

| 4Ch | IOUT_UC_FAULT_RESPONSE    | 5 ms    | 5 ms    |               |

| 50h | OT_FAULT_RESPONSE         | 1.0 sec | 1.0 sec | Note 1        |

| 54h | UT_FAULT_RESPONSE         | 1.0 sec | 1.0 sec | NOT SUPPORTED |

| 56h | VIN_OV_FAULT_RESPONSE     | 10 ms   | 5 ms    | Note 1        |

| 5Ah | VIN_UV_FAULT_RESPONSE     | 10 ms   | 5 ms    | Note 1        |

| 5Ch | IIN_OC_FAULT_RESPONSE     | 10 ms   | 5 ms    | NOT SUPPORTED |

| 63h | TON_MAX_FAULT_RESPONSE    | 5 ms    | 5 ms    | Note 1        |

| 69h | POUT_OP_FAULT_RESPONSE    | 5 ms    | 5 ms    | NOT SUPPORTED |

NOTE 1: Section 10.5.1 of the PMBus specification describes the response to voltage, temperature and TON\_MAX faults. For the UCD92xx, the Response setting (bits [7:6]) of 11b "The device's output is disabled while the fault is present. Operation resumes and the output is enabled when the fault condition no longer exists" is not supported.

## 10.12(61h) TON\_RISE

This command, described in section 16.2 of the PMBus specification, sets the time, in ms, from when the output starts to rise until the voltage has entered the regulation band. The UCD92xx implementation deviates slightly from the PMBus standard. According to the PMBus standard, setting this parameter to a value of 0 will instruct the unit to bring its output voltage to the programmed regulation value as quickly as possible. The UCD92xx will bring its output voltage to the programmed regulation value as quickly as possible any time that TON\_RISE is set to a value faster than it can achieve.

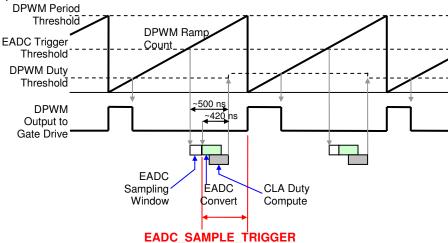

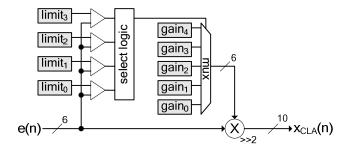

#### 10.13 (62h) TON MAX FAULT LIMIT