# **One Cell Lithium-ion/Polymer Battery Protection IC**

### **GENERAL DESCRIPTION**

The XBL6021-SM Series product is a hi gh integration solution for lithium-ion/polym er battery protection. XBL6021-SM Series contains advanced power MOSFET, highaccuracy voltage detection circuits and del ay circuits. XBL6021-SM Series is put into an DFN1X1x0.37-4 package and external MCU, GPIO signal to high level to enable the chip to enter shipping mode makes it an ideal solution in limited space of battery pack.

XBL6021-SM Series has all the protectio n functions required in the battery applicati on including overcharging, over dischargin g, overcurrent and load short circuiting prot ection etc. The accurate overcharging dete ction voltage ensures safe and full utilizatio n charging. The low standby current drains little current from the cell while in storage.

The device is not only targeted for digital cellular phones, but also for any other Li-lo -n and Li-Poly battery-powered information appliances requiring long-term battery life.

### FEATURES

• Protection of Battery Cell Reverse Connection with external load

- Control MOS of integrated shipping mode

- Support all pin rosin joint

- Integrate Advanced Power MOSFET with Equivalent of 55mΩ Rss(ON)

- DFN 1x1x0.37-4Package

- Reverse connection of charger is supported

- Overdischarge Current 1 Protection

- Charger Detection Function

- OV Battery Charging Function

- Delay Times are generated inside

- High-accuracy Voltage Detection

- Over-Discharge Self-locking

- Low Current Čonsumption -Operation Mode:0.5µA typ.

-Power-down Mode: 10nA max.

- RoHS Compliant and Lead (Pb) Free

- Be suitable for 100% shipping mode

### **APPLICATIONS**

One-Cell Lithium-ion Battery Pack Lithium-Polymer Battery Pack Wearable Device Bluetooth Earphone

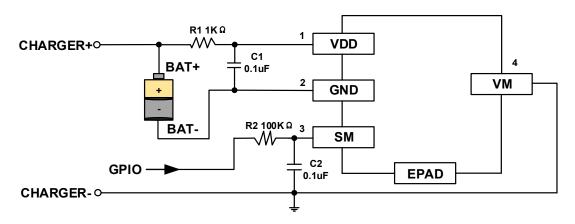

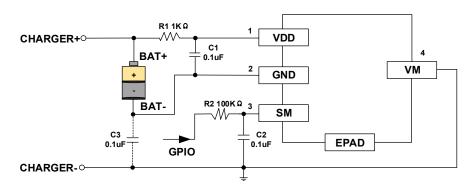

Figure 1. Typical Application Circuit

#### (Suggestion: Connect EPAD pin with GND)

### ORDERING INFORMATION

#### Conventional basic voltage temperature parameters: Ta=25°C

| PART<br>NUMBER    | OCV<br>[VCU] (V)<br>(Ta=25°C) | OCV*<br>[VCU] (V)<br>(Ta=-5℃<br>~55℃) | OCRV<br>[VCL] (V) | ODV<br>[VDL] (V) | ODRV<br>[VDR] (V) | TOP MARK   |

|-------------------|-------------------------------|---------------------------------------|-------------------|------------------|-------------------|------------|

| XBL6021Q2S-<br>SM | 4.275±25mV                    | 4.275±30mV                            | 4.075±50mV        | 2.8±50mV         | 3.0±80mV          |            |

| XBL6021J2S-<br>SM | 4.425±25mV                    | 4.425±30mV                            | 4.25±50mV         | 2.8±50mV         | 3.0±80mV          | YWxx(note) |

| XBL6021M2S-<br>SM | 4.475±25mV                    | 4.475±30mV                            | 4.30±50mV         | 2.8±50mV         | 3.0±80mV          |            |

#### Conventional basic voltage temperature parameters: Ta=-40 ℃~85 ℃\*

| PART        | OCV         | OCRV        | ODV         | ODRV         | TOP MARK   |

|-------------|-------------|-------------|-------------|--------------|------------|

| NUMBER      | [VCU] (V)   | [VCL] (V)   | [VDL] (V)   | [VDR] (V)    |            |

| XBL6021Q2S- | 4.275-50mV  | 4.075-75mV  | 2.800-80mV  | 3.000-100mV  |            |

| SM          | ∼4.275+35mV | ∼4.075+60mV | ~2.800+80mV | ~3.000+100mV |            |

| XBL6021J2S- | 4.425-50mV  | 4.250-75mV  | 2.800-80mV  | 3.000-100mV  | YWxx(note) |

| SM          | ∼4.425+35mV | ∼4.250+60mV | ~2.800+80mV | ~3.000+100mV |            |

| XBL6021M2S- | 4.475-50mV  | 4.300-75mV  | 2.800-80mV  | 3.000-100mV  |            |

| SM          | ∼4.475+35mV | ∼4.300+60mV | ~2.800+80mV | ∼3.000+100mV |            |

Note:1)."YW" is manufacture date code, "Y" means the year, "W" means the week.

2)."xx" is internal product code of XySemi.

\*: Since products are not screened at high and low temperatures, the specification for this temperature range is guaranteed by design, not tested in production.

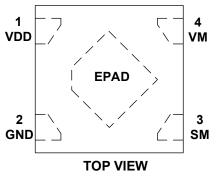

### **PIN CONFIGURATION**

Figure 2. PIN Configuration

#### **PIN DESCRIPTION**

| XBL6021-SM SE-<br>RIES<br>PIN NUMBER | PIN NAME | PIN DESCRIPTION                                                                                   |

|--------------------------------------|----------|---------------------------------------------------------------------------------------------------|

| 1                                    | VDD      | Power Supply.                                                                                     |

| 2                                    | GND      | Ground, connect the negative terminal of the battery to these pins.                               |

| 3                                    | SM       | This Pin relative to VM is connected to high pulse signal, so that the chip en-<br>ters SM mode.  |

| 4                                    | VM       | The negative terminal of the battery pack. The internal FET switch connects this terminal to GND. |

| EPAD                                 | NC       | Not Use. Suggest to connect with GND.                                                             |

#### **ABSOLUTE MAXIMUM RATINGS**

(NOTE: DO NOT EXCEED THESE LIMITS TO PREVENT DAMAGE TO THE DEVICE. EXPOSURE TO ABSOLUTE MAXIMUM RATING CONDITIONS FOR LONG PERIODS MAY AFFECT DEVICE RELIABIL-ITY.)

| PARAMETER                                            | VALUE      | UNIT |

|------------------------------------------------------|------------|------|

| VDD input pin voltage                                | -0.3 to 9  | V    |

| VM input pin voltage                                 | -8 to 10   | V    |

| SM input pin voltage                                 | -0.3 to 9  | V    |

| Operating Ambient Temperature                        | -40 to 85  | °C   |

| Maximum Junction Temperature                         | 150        | °C   |

| Storage Temperature                                  | -55 to 150 | °C   |

| Lead Temperature ( Soldering, 10 sec)                | 300        | °C   |

| Power Dissipation at T=25°C                          | 0.3        | W    |

| Package Thermal Resistance (Junction to Ambient) 0JA | 250        | °C/W |

| Package Thermal Resistance (Junction to Case) θJC    | 130        | °C/W |

| ESD HBM                                              | 8000       | V    |

### **ELECTRICAL CHARACTERISTICS**

Typical and limits appearing in normal type apply for TA = 25°C, unless otherwise specified.

| PARAMETER                                      | SYMBOL         | TEST CONDITIONS              | MIN     | ТҮР     | MAX     | UNIT |

|------------------------------------------------|----------------|------------------------------|---------|---------|---------|------|

| Detection voltage                              |                |                              |         |         |         |      |

| Discharge over-current release<br>Voltage      | <b>V</b> RIOV1 |                              | VDD-1.0 | VDD-0.7 | VDD-0.4 | V    |

| Detection Current                              |                |                              |         |         |         |      |

| Overdischarge Current Detection                | liov1          | VDD=3.6V                     | 0.10    | 0.15    | 0.20    | А    |

| Overcharge Current Detection                   | Існос          | VDD=3.6V                     | 0.20    | 0.30    | 0.40    | А    |

| Load Short-Circuiting Detection                | *ISHORT        | VDD=3.6V                     | 0.30    | 0.45    | 0.60    | А    |

| Current Consumption                            |                |                              |         |         |         |      |

| Current Consumption in Normal<br>Operation     | IOPE           | VDD=3.6V<br>VM =0V           |         | 0.5     | 0.8     | μA   |

| Current Consumption in Power<br>Down           | IPD            | VDD=2.0V<br>VM pin floating  |         |         | 10      | nA   |

| VM Internal Resistance                         |                |                              |         |         |         |      |

| Internal Resistance between VM and VDD         | *R∨mD          | VDD =2.0V<br>VM pin floating | 100     | 150     | 200     | kΩ   |

| Internal Resistance between VM and GND         | *R∨ms          | VDD=3.6V<br>VM=3.6V          | 15      | 25      | 35      | kΩ   |

| Logic Levels on SM                             |                |                              |         | •       |         |      |

| Logic Low input voltage to VM                  | VSML           |                              |         |         | 0.5     | V    |

| Logic High input voltage to VM                 | Vsмн           |                              | 1.3     |         |         | V    |

| FET on Resistance                              |                |                              |         | •       |         |      |

| Equivalent FET on Resistance                   | *Rss(on)       | VDD=3.6V IVM<br>=0.1A        |         | 55      |         | mΩ   |

| Detection Delay Time                           |                |                              |         |         |         |      |

| Overcharge Voltage Detection De-<br>layTime    | tcu            |                              | 58      | 185     | 255     | mS   |

| Overdischarge Voltage Detection<br>Delay Time  | tDL            |                              | 16      | 40      | 48      | mS   |

| Overdischarge Current1 Detection<br>Delay Time | tiov1          | VDD=3.6V                     | 4       | 10      | 15      | mS   |

| Overcharge Current Detection<br>Delay Time     | tснос          | Vdd=3.6V                     | 4       | 10      | 15      | mS   |

| Load Short-Circuiting Detection<br>Delay Time  | *tshort        | Vdd=3.6V                     | 144     | 350     | 500     | μS   |

| SM Detection Delay Time                        | tsм            |                              | 16      | 40      | 56      | mS   |

Note1:

\*: Since products are not screened at high and low temperatures, the specification for this temperature range is guaranteed by design, not tested in production.

### **ELECTRICAL CHARACTERISTICS**

Typical and limits appearing in normal type apply for TA = -40°C~85°C, unless otherwise specified.\*

| PARAMETER                                      | SYMBOL            | TEST CONDITIONS              | MIN     | ТҮР     | MAX     | UNIT |  |  |

|------------------------------------------------|-------------------|------------------------------|---------|---------|---------|------|--|--|

| Detection voltage                              |                   |                              |         |         |         |      |  |  |

| Discharge over-current release<br>Voltage      | VRIOV1            |                              | VDD-1.1 | VDD-0.7 | VDD-0.3 | V    |  |  |

| Detection Current                              | Detection Current |                              |         |         |         |      |  |  |

| Overdischarge Current Detection                | liov1             | VDD=3.6V                     | 0.07    | 0.15    | 0.26    | Α    |  |  |

| Overcharge Current Detection                   | Існос             | VDD=3.6V                     | 0.14    | 0.30    | 0.52    | А    |  |  |

| Load Short-Circuiting Detection                | *ISHORT           | VDD=3.6V                     | 0.21    | 0.45    | 0.78    | А    |  |  |

| Current Consumption                            |                   |                              |         |         |         |      |  |  |

| Current Consumption in Normal<br>Operation     | IOPE              | VDD=3.6V<br>VM =0V           |         | 0.5     | 1.0     | μA   |  |  |

| Current Consumption in Power<br>Down           | IPD               | VDD=2.0V<br>VM pin floating  |         |         | 0.2     | μA   |  |  |

| VM Internal Resistance                         |                   |                              |         |         |         |      |  |  |

| Internal Resistance between VM and VDD         | *R∨мD             | VDD =2.0V<br>VM pin floating | 80      | 150     | 240     | kΩ   |  |  |

| Internal Resistance between VM and GND         | *R∨ms             | VDD=3.6V<br>VM=3.6V          | 12      | 25      | 42      | kΩ   |  |  |

| Logic Levels on SM                             |                   |                              |         |         |         |      |  |  |

| Logic Low input voltage to VM                  | VSML              |                              |         |         | 0.4     | V    |  |  |

| Logic High input voltage to VM                 | Vsмн              |                              | 1.6     |         |         | V    |  |  |

| FET on Resistance                              |                   |                              |         |         |         |      |  |  |

| Equivalent FET on Resistance                   | *Rss(on)          | VDD=3.6V IVM=0.1A            |         | 55      |         | mΩ   |  |  |

| Detection Delay Time                           |                   |                              |         |         |         |      |  |  |

| Overcharge Voltage Detection De-<br>layTime    | tcu               |                              | 46.5    | 185.0   | 357.0   | mS   |  |  |

| Overdischarge Voltage Detection<br>Delay Time  | tDL               |                              | 12.8    | 40.0    | 67.2    | mS   |  |  |

| Overdischarge Current1 Detection<br>Delay Time | tiov1             | Vdd=3.6V                     | 3.2     | 10.0    | 21.0    | mS   |  |  |

| Overcharge Current Detection<br>Delay Time     | tснос             | VDD=3.6V                     | 3.2     | 10.0    | 21.0    | mS   |  |  |

| Load Short-Circuiting Detection<br>Delay Time  | *tshort           | VDD=3.6V                     | 115.0   | 350.0   | 700.0   | μS   |  |  |

| SM Detection Delay Time                        | tsм               |                              | 12.8    | 40.0    | 78.5    | mS   |  |  |

Note1:

\*: Since products are not screened at high and low temperatures, the specification for this temperature range is guaranteed by design, not tested in production.

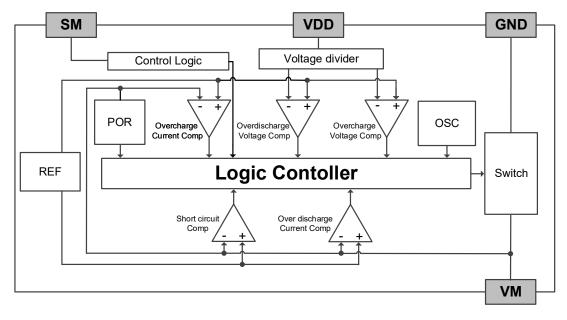

#### FUNCTIONAL BLOCK DIAGRAM

Figure 3. Functional Block Diagram

#### FUNCTIONAL DESCRIPTION

The XBL6021-SM Series monitors the voltage and current of a battery and protec ts it from being damaged due to overcha rge voltage, overdischarge voltage, overdischarge current, and short circuit conditions by disconnecting the battery from the load or charger. These functions are required in order to operate the battery cell within sp ecified limits.

The device has built in R1 and C1 circuit ry to ensure the proper operation of the chi p,and built-in R2 and C2 to enhance the an ti-interference circuitry. The MOSFET is int egrated and its  $R_{SS(ON)}$  is as low as 55m $\Omega$  ty pical.

#### Normal operating mode

If no exception condition is detected, ch arging and discharging can be carried out freely. This condition is called the normal operating mode.

#### **Overcharge Condition**

When the battery voltage becomes highe r than the overcharge detection voltage (V

cu) during charging under normal condition and the state continues for the overcharge detection delay time ( $t_{cu}$ ) or longer, the XB L6021-SM Series turns the charging con trol FET off to stop charging. This condition is called the overcharge condition. The o vercharge condition is released in the follo wing two cases:

1. When the connected charger battery voltage drops below the overcharge releas e voltage ( $V_{cL}$ ), the XBL6021-SM Series tu rns the charging control FET on and return s to the normal condition.

When a load is connected and dischar ging starts, the XBL6021-SM Series turns t he charging control FET on and returns to t he normal condition. The release mechanis m is as follows: the discharging current fl ows through an internal parasitic diode of t he charging FET immediately after a load i s connected and discharging starts, and t he VM pin voltage increases about 0.7V orward voltage of the diode) from the ND pin voltage momentarily. The XBL6021 -SM Series detects this voltage and releas es the overcharge condition. Consequentl y, in the case that the battery voltage is

qual to or lower than the overcharge detect ion voltage (V<sub>cu</sub>), the XBL6021-SM Series r eturns to the normal condition immediately, but in the case the battery voltage is high er than the overcharge detection voltage (V cu),the chip does not return to the normal c ondition until the battery voltage drops belo w the overcharge detection voltage (V<sub>cu</sub>) ev en if the load is connected. In addition, if th e VM pin voltage is equal to or lower than t he overcurrent detection voltage when a lo ad is connected and discharging starts, the chip does not return to the normal condition n.

#### Remark :

If the battery is charged to a voltage higher than the overcharge detection voltage (V<sub>cu</sub>) and the battery voltage does not drops below the over charge detection voltage (V<sub>cu</sub>) even when a heav y load, which causes an overcurrent, is connecte d, the overcurrent do not work until the battery v oltage drops below the overcharge detection v oltage (V<sub>cu</sub>). Since an actual battery has, howeve r, an internal impedance of several dozens of m  $\Omega$ , and the battery voltage drops immediately af ter a heavy load which causes an overcurrent is connected, the overcurrent work. Detection of lo ad short-circuiting works regardless of the b attery voltage.

#### **Overdischarge Condition**

When the battery voltage drops below the overdischarge detection voltage  $(V_{DL})$ during discharging under normal condition and it continues for the overdischarge dete ction delay time ( $t_{DL}$ ) or longer, the XBL602 1-SM Series turns the discharging control FET off and stops discharging. This conditi on is called overdischarge condition. After t he discharging control FET is turned off, th e VM pin is pulled up by the R<sub>VMD</sub> resistor b etween VM and VDD in XBL6021-SM Seri es. The current of the chip is reduced to t he power-down current (IPDN). This conditio n is called power-down condition. The VM and VDD pins are shorted by the RVMD resis tor in the IC under the overdischarge and p ower-down conditions.

The power-down condition is released when a charger is connected and the poten

# XBL6021-SM Series

tial difference between VM and VDD beco mes 2.0V (typ.) or higher (0V charger volta ge when charging). At this time, the FET i s still off. When the battery voltage become s 1.6V or higher (see note), the XBL6021-SM S eries turns the FET on and changes to the normal condition from the overdischarge co ndition.

#### Remark:

If the VM pin voltage is no less than the GND voltage ,when the battery under overdischa rge condition is connected to a charger, the over discharge condition is released (the discharging control FET is turned on) as usu-al, provided that the battery voltage reaches the overdischarge vol tage (VDL) or higher.

#### **Overcurrent Condition**

When the discharging current becomes equal to or higher than a specified value (the VM pin voltage is equal to or higher than the overcurrent detection voltage) duri ng discharging under normal condition a nd the state continues for the overcurrent d etection delay time or longer, the XBL6021 -SM Series turns off the discharging control FET to stop discharging. This condition is called overcurrent condition. (The overcurr ent includes overcurrent, or load short-circ uiting.)

The VM and GND pins are shorted intern ally by the R<sub>VMS</sub> resistor under the overcurre nt condition. When a load is connected, t he VM pin voltage equals the VDD voltage due to the load.

The overcurrent condition returns to the normal condition when the load is released and the impedance between the B+ and B-pins becomes higher than the automatic recoverable impedance. When the load is removed, the VM pin goes back to the GND potential since the VM pin is shorted the GND pin with the Rvms resistor. Detectin g that the VM pin potential is lower than the overcurrent detection voltage ,the IC return s to the normal condition.

#### **Abnormal Charge Current Detection**

If the VM pin voltage drops below the charger detection voltage during charging under the normal condition and it continues for the overcharge detection delay time (t<sub>choc</sub>) or longer, the XBL6021-SM Series tur ns the charging control FET off and stops charging. This action is called abnormal ch arge current detection.

Abnormal charge current detection work s when the charging control FET is on and the VM pin voltage drops below the charge r detection voltage .When an abnormal cha rge current flows into a battery in the overc harge condition, the XBL6021-SM Series c onsequently turns the charging control FET off and stops charging after the battery vol tage becomes the overcharge detection vol tage and the overcharge detection delay ti me ( $t_{choc}$ ) elapses.

Abnormal charge current detection is released when the voltage difference betw een VM pin and GND pin becomes lower than the charger detection voltage by sepa rating the charger. Since the 0 V battery c harging function has higher priority than th e abnormal charge current detection functi on, abnormal charge current may not be de tected by the product with the 0 V battery c harging function while the battery voltage i s low.

#### Load Short-circuiting condition

If voltage of VM pin is equal or above short circuiting protection voltage, the XBL 6021-SM Series will stop discharging and battery is disconnected from load. The max imum delay time to switch current off is t SHORT. This status is released when voltage o f VM pin is lower than short protection volt age, such as when disconnecting the loa d.

#### **Delay Circuits**

The detection delay time for load short-cir cuiting starts when overdischarge current 1 is detected. As soon as load short-circuitin g is detected over detection delay time for load short- circuiting, the XBL6021-SM Se ries stops discharging. When battery voltag e falls below overdischarge detection volta ge due to overdischarge current, the XBL6 021-SM Series stop discharging by overdis charge current detection. In this case the re covery of battery voltage is so slow that if b attery voltage after overdischarge voltage detection delay time is still lower than over discharge detection voltage, the XBL6021-SM Series shifts to power-down.

#### 0V Battery Charging Function (1) (2) (3)

This function enables the charging of a connected battery whose voltage is 0 V by self-discharge.

#### Note:

(1) Some battery providers do not recommend charging of completely discharged batteries. Please refer to battery providers before the selection of 0 V battery charging function.

(2) The 0V battery charging function has higher priority than the abnormal charge current detection function. Consequently, a product with the 0 V battery charging function charges a battery and abnormal charge current cannot be detected during the battery voltage is low (at most 1.8 V or lower).

(3) When a battery is connected to the IC for the first time, the IC may not enter the normal condition in which discharging is possible. In this case, set the VM pin voltage equal to the GND voltage (short the VM and GND pins or connect a charger) to enter the normal condition.

#### Discharge Over-current /Short Selfrecovery

The recovery condition of short circuit/ discharge overcurrent is that the VM voltag e is less than  $V_{\text{RIOV1.}}$

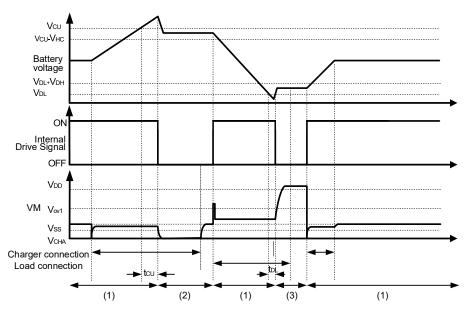

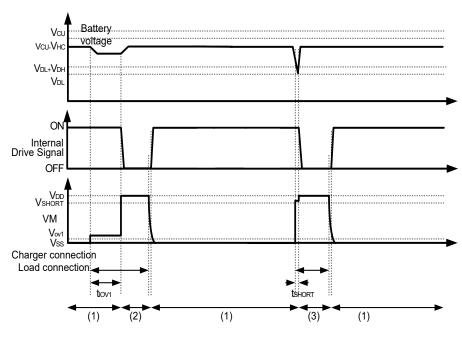

### **TIMING CHART**

#### 1. Overcharge and Overdischarge voltage detection

Figure 4-1 Overcharge and Overdischarge Voltage Detection

Remark: (1) Normal condition (2) Overcharge voltage condition (3) Overdischarge voltage condition

#### 2. Overdischarge Current and Load Short detection

#### Figure4-2 Overdischarge Current and Short Detection

Remark: (1) Normal condition (2) Overcharge voltage condition (3) Overdischarge voltage condition

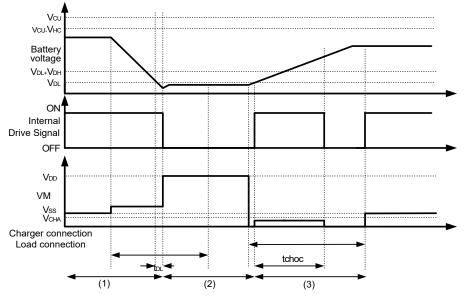

#### 3. Abnormal Charger Detection

Figure 4-3 Abnormal Charger Detection

Remark: (1) Normal condition (2) Overdischarge voltage condition (3) Overcharge voltage condition

## TYPICAL APPLICATION

As shown in Figure 5, the current path which must be kept as short as possible. For thermal management, ensure that these trace widths are adequate. C is a decoupling ca pacitor which should be placed as close as possible to XBL6021-SM SERIES. If add one 0.1uF capacitor between VM pin and GND pin closely, the system ESD

level and anti-interference capability of circuit will improve greatly.

(Suggestion: Connect EPAD pin with GND)

Figure 5 XBL6021-SM SERIES in a Typical Battery Protection Circuit

| Symbol | Тур | Value range | Unit |

|--------|-----|-------------|------|

| R1     | 1   | 0.47~2      | ΚΩ   |

| R2     | 100 | 50~150      | ΚΩ   |

| C1     | 0.1 | 0.1~1       | μF   |

| C2     | 0.1 | 0.047~0.1   | μF   |

| C3     | 0.1 | -           | μF   |

Remark:

1. The above parameters may be changed without notice;

2. The schematic diagram and parameters of the IC are not used as the basis to ensure the operation of the circuit. Please conduct full measurement on the actual application circuit before setting the parameters. 3.R2 and C2 affect the time to enter SM mode.

#### Precautions

• Pay attention to the operating conditions for input/output voltage and load current so that the power loss in XBL6021-SM SERIES does not exceed the power dissipation of the package.

• Do not apply an electrostatic discharge to this XBL6021-SM SERIES that exceeds the performance ratings of the built-in electrostatic protection circuit.

#### Description of shipping patterns

Entering shipping mode:

1.If VSM is greater than VSmH, and Tsm is guaranteed to be the maximum time;

2.After the main switch is disconnected, the VM voltage is increased for 3 seconds and the voltage continues to be greater than 2V;

There are two ways to exit SM mode:

1. Short circuit the two pins of VM and GND;

2. Plug in the charger again.

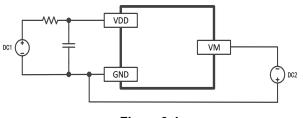

### **APPLIED MEASUREMENT METHOD**

#### (1).Overcharge characteristic test method:

a. According to the figure6-1, connect the power supply DC1 to the B + and GND pins of the system board and set the voltage to about 3.6V. Connect the power supply from GND to VM to DC2 power supply and set 100mV current limiting 10mA. Observe the waveform.

b. Adjust the power supply voltage V1 and increase it by 0.001V until the output level of VM pin c hanges from 0 to negative (-100mV). Record the overcharge protection voltage and measure the pr otection delay.

c. Adjust the power supply voltage V1 to decrease by 0.001V until the output voltage of VM pin is recovered from negative (-100mV) to 0 level, and record the overcharge recovery voltage.

#### (2).Over discharge characteristic test method:

a. According to the figure6-2, connect the power supply DC1 to the B + and GND pins of the system b oard and set the voltage to about 3.6V. Connect the DC2 power supply from VM to GND, set the 100mV c urrent limiting 10mA, and observe the waveform.

b. Adjust the power supply voltage V1 and decrease it by 0.001V until the output level of VM pin chan ges from 0 to positive (100mV). Record the overdischarge protection voltage and measure the protection d elay.

c. Adjust the power supply voltage V1 to increase by 0.001 V until the output voltage of VM pin is resto red from positive (100 mV) to 0 level, and record the overdischarge recovery voltage.

#### (3).Discharge over current test method:

a. According to the figure6-3, connect the DC1 power supply to the B + and GND pins of the system board and set the voltage to about 3.0V/3.6V/4.2V. Connect the electronic load from B + to VM and observe the waveform.

b. Adjust the electronic load increase it by 1mA step, detect that the current from B + to VM is turned off and meet the delay standard (about 10ms), and record the discharge delay time.

#### (4).Charging over current test method:

a. According to the figure6-4, connect the DC1 power supply to the B + and GND pins of the system board and set the voltage to about 3.0V/3.6V/4.2V, and load DC2 power supply from GND to VM.

b. Adjust the current limiting value of DC2 power supply to increase by 1mA step, detect that the current from GND to VM is turned off and meet the delay standard(about 10ms), and record the charging over-current delay time.

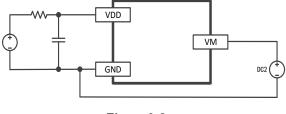

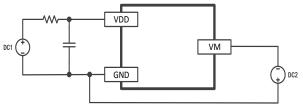

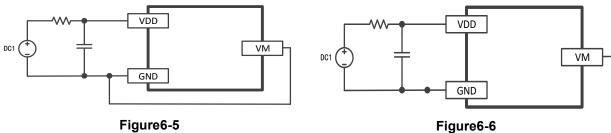

#### (5).lq test method:

a. As shown in the figure6-5, connect the positive pole of DC1 to B +, and the negative pole to GND, and set the voltage to 3.6V;

b. VM grounding, record the current passing through DC1 (Iq).

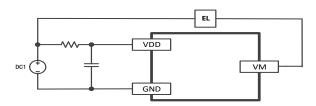

#### (6).Isd test method:

a. As shown in the figure 6-6, connect the positive pole of DC1 to B + and the negative pole to GND, and set the voltage to 2V;

b. VM is suspended and the current passing through DC1 is recorded as Isd.

# SCHEMATIC DIAGRAM OF TEST METHOD

Figure6-1

Figure6-2

Figure6-3

Figure6-4

DC1

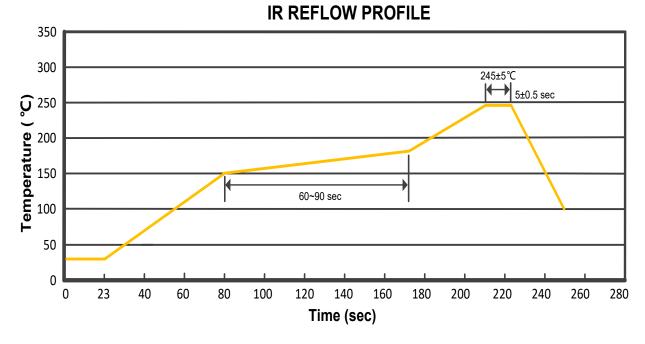

# Solderability Curve of Lead-Free Reflow Soldering (applicable to SMT tube)

Explain:

1.Preheating temperature  $25 \sim 150 \,^{\circ}$ C, duration  $60 \sim 90$ sec; 2.Peak temperature  $245 \pm 5 \,^{\circ}$ C, duration  $5 \pm 0.5$ sec; 3.Cooling rate of welding process is  $2 \sim 10 \,^{\circ}$ C/sec.

### Resistance to welding heat conditions

Temperature: 270±5°C; Time:10±1sec

Suzhou XySemi Electronic Technology Co., Limited.

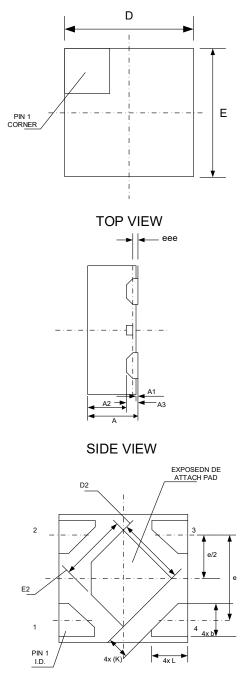

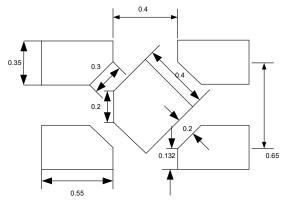

# PACKAGE OUTLINE(DFN1x1-4)

BOTTOM VIEW

**RECOMMENDED LAND PATTERN uint (mm)**

| SYMBOL | NOM                                                           |

|--------|---------------------------------------------------------------|

| A      | 0.37                                                          |

| A1     | 0.02                                                          |

| A2     | 0.27                                                          |

| A3     | 0.102REF                                                      |

| b      | 0.23                                                          |

| D      | 1BSC                                                          |

| E      | 1BSC                                                          |

| e      | 0.65BSC                                                       |

| D2     | 0.48                                                          |

| E2     | 0.48                                                          |

| L      | 0.25                                                          |

| к      | 0.21REF                                                       |

| eee    | 0.05                                                          |

|        | A<br>A1<br>A2<br>A3<br>b<br>D<br>E<br>E<br>D2<br>E2<br>L<br>K |

### DISCLAIMER

The information described herein is subject to change without notice.

Suzhou XySemi Electronic Technology Co., Limited is not responsible for any problems caused by circuits or diagrams described herein whose related industrial properties, patents, or other rights belong to third parties. The application circuit examples explain typical applications of the products, and do not guarantee the success of any specific mass-production design.

When the products described herein are regulated products subject to the Wassenaar Arrangement or other arrangements, they may not be exported without authorization from the appropriate governmental authority.

Use of the information described herein for other purposes and/or reproduction or copying without express permission of Suzhou XySemi Electronic Technology Co., Limited is strictly prohibited.

The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment ,medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of Suzhou XySemi Electronic Technology Co., Limited.

Although Suzhou XySemi Electronic Technology Co., Limited. exerts the greatest possible effort to ensure high quality and reliability, the failure or malfunction of semiconductor may occur. The use of these products should therefore give thorough

consideration to safety design, including redundancy, fire-prevention measure and malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.