# bq77915 Cell Balancing

8/16/2018 Willy Massoth

TI Information - Selective Disclosure

#### **bq77915 cell balancing information**

- See the data sheet <a href="http://www.ti.com/lit/gpn/bq77915">www.ti.com/lit/gpn/bq77915</a> section 9.3.4

- This references various sections and diagrams

- Look for a future cell balance apnote

TI Information – Selective Disclosure

### **Cell balance control pin**

• Cell balance is controlled by the CBI pin.

CBI low threshold

Vсві

- CBI has an internal pull up

- It is current limited

- If controlled it should be pulled low with an open drain/open collector output

- It should not be driven high, this can force current into the part and voltage on the AVDD pin which powers the circuit

- If always enabled CBI may be tied to VSS

- If stacked, CBI should have a resistor

Figure 29. The bq77915 Device with Five Cells

PACK

TI Information – Selective Disclosure

3

0.5

# **Cell balancing general**

- Cell balancing requires charge current, voltage qualification, and absence of certain faults

- Current must be above the state comparator threshold

- ~ 1.875 mV to ~ 0.625 mV

- Voltage expected to rise during charge

- A cell voltage must be above the start threshold

- Cell voltage must be sufficiently separated during charge

- A VFC target defined from OV changes balance behavior

| าต  | CURRENT STATE COMPARATOR |                                                  |                     |        |    |  |  |  |  |

|-----|--------------------------|--------------------------------------------------|---------------------|--------|----|--|--|--|--|

|     | V <sub>STATE_D</sub>     | Discharge qualification threshold1               | Measured at SRP-SRN | -1.875 | m∨ |  |  |  |  |

| e ( | V <sub>STATE_D_HYS</sub> | Discharge qualification threshold1<br>hysteresis | Measured at SRP-SRN | -1.25  | m∨ |  |  |  |  |

|     | V <sub>STATE_C</sub>     | Charge qualification threshold1                  | Measured at SRP-SRN | 1.875  | m∨ |  |  |  |  |

|     | VSTATE_C_HYS             | Charge qualification threshold1<br>hysteresis    | Measured at SRP-SRN | 1.25   | m∨ |  |  |  |  |

|     | t <sub>STATE</sub>       | State detection qualification time               |                     | 1.2    | ms |  |  |  |  |

NAME

Description

Options

V<sub>START</sub>

Start Threshold for Cell Balancing

3.5 V, 3.8 V

V<sub>HYST</sub>

Hysteresis between overvoltage and full charge voltage range (VOV – VFC)

50 mV, 100 mV, 150 mV, 200 mV

Difference between the cell balancing threshold voltages (VCBTH –

VCBTL)

VSTEP

Table 2. Cell Balancing Threshold Summary

50 mV, 100 mV, 150 mV, 200

m٧

### **Cell balance mechanism**

- As other BMS devices, pins pull together

- Current through input filter resistors bypasses the cell and power is dissipated

- Internal resistance is small

- Bypassed current is small during high current charge, becomes more significant portion as charge current tapers

- Duty cycle is fixed by device timing

| R <sub>BAL</sub> | Cell balancing internal FET<br>resistance | Cell1 through Cell5 = 4 V, VDD = 20 V | 8 | 12   | 20 | Ω |

|------------------|-------------------------------------------|---------------------------------------|---|------|----|---|

| DBAL             | Cell balancing duty cycle                 | Only one cell balanced in the stack   |   | 90 % |    |   |

|                  |                                           | 1                                     |   |      |    |   |

TI Information – Selective Disclosure

5

Texas Instruments

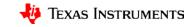

## **External balancing**

- Internal balance current is high, but limited, reduces input filter resistance

- External balancing allows higher current or more filter, can be done similar to other BMS ICs

- N or P channel

- N-channel shown in data sheet

Cell Balancing current (VC5, VC4, VC3, VC2, VC1, VC0)

6

TI Information - Selective Disclosure

Output current

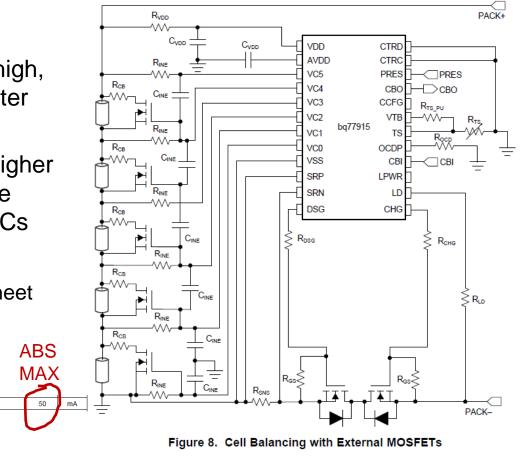

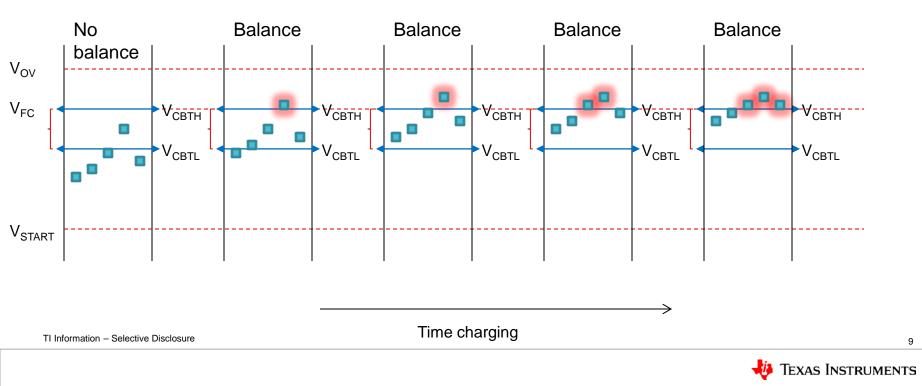

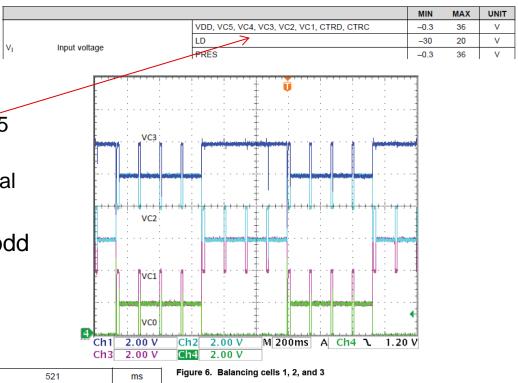

#### **Cell balance start with voltage**

• At lower voltages, cells must be separated by the threshold or greater

Tek PreVu

4

Ch1 2.00 V

Ch3 2.00 V

VC3

VC2

VC1

VC0

Ch2 2.00 V

Ch4 2.00 V

M 200ms

60.00 %

Pattern

-----

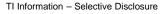

#### Thresholds will advance as cell voltages rise

• Balance may start and stop during charge

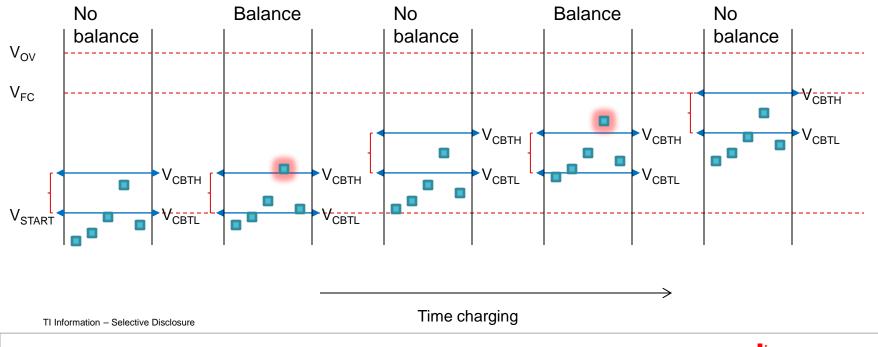

#### Cells above $V_{FC}$ balance

Balance continues with charge current

#### Well matched cells don't balance

- Cells above V<sub>FC</sub> will balance

- Balance stops when current drops sufficiently

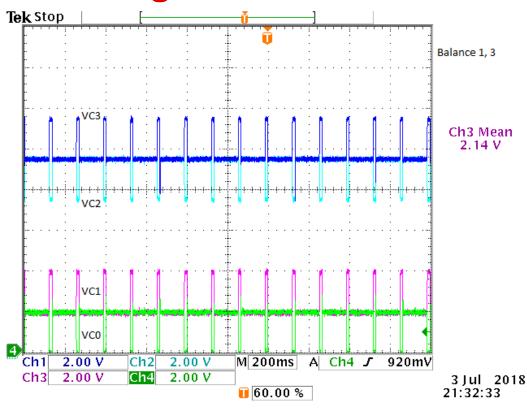

# Non-adjacent cell balancing

- Cells will balance simultaneously when not adjacent

- Any 1, 3, 5

- 2 and 4

# **Adjacent cells balancing**

- Adjacent cells won't balance simultaneously

- Typically important for differential voltage limit on inputs, but bq77915 does not have such limit

- Important to allow signal for external balancing

- The part will duty cycle between odd and even cells when balancing adjacent cells is required

TI Information – Selective Disclosure

t<sub>BAL</sub>

Odd and even cell group

balancing duration

#### **Balance stop**

- Balance will start with current and sufficient voltage difference

- Stops when current drops below state comparator level

- With sufficient voltage difference

- Balance starts with current application

- Stops with certain faults, here simulated OCC

- Does not resume on current drop, fault must be recovered

TI Information – Selective Disclosure

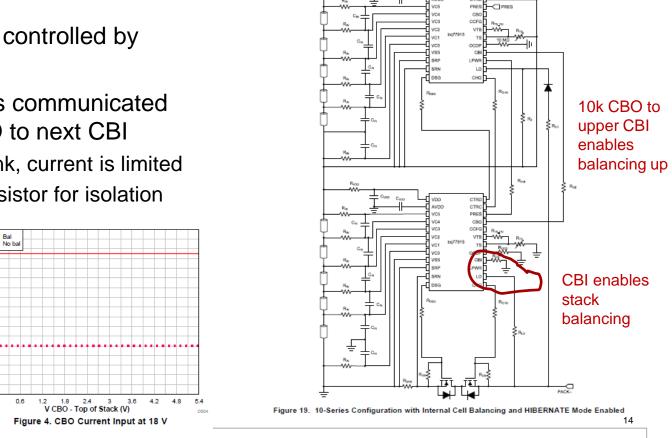

### **Balance control when stacking**

- Balance is manually controlled by bottom part CBI

- Balance command is communicated up the stack by CBO to next CBI

- CBO is a current sink, current is limited

- Use 10k nominal resistor for isolation

0.8

0.7 0.6

0.2 0.1 -0.1 -0.2 -0.3 -0.4

-0.5

TI Information – Selective Disclosure

0.5 0.4 0.3 0.2

PACK+

## **CBO output control for upper part**

- When no faults

- CBI signals CBO with charge current

Charge current flow signals CBO with CBI low

15

Texas Instruments

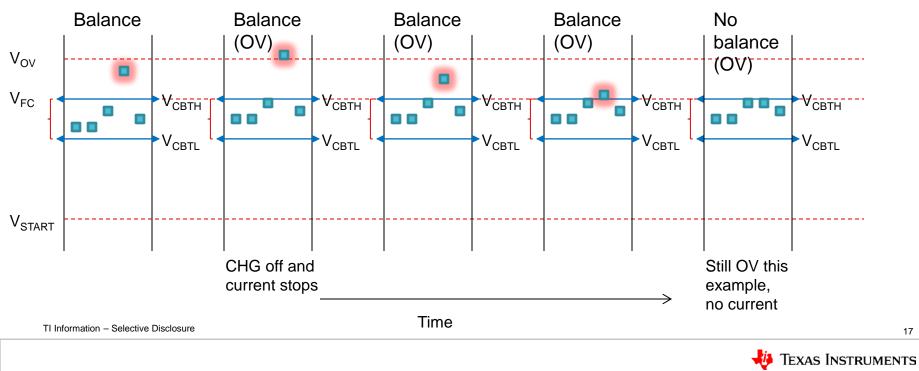

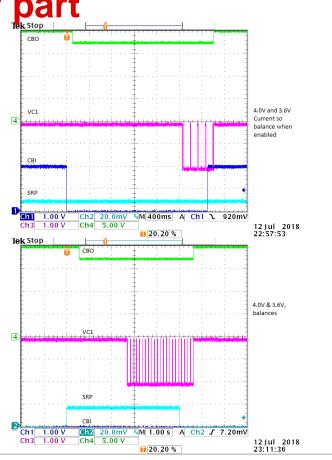

# **Balance in OV**

- OV will stop balance for upper devices

- Cell will balance in OV

- CBI required

- Current not required

- Balance continues until the cell voltage drops to  $V_{FC}$  or  $V_{OV} V_{HYS_OV}$ , whichever occurs earlier.

- If upper device has OV, CHG low

- CTRC low on lower device sets CBO low even with no current so upper device can balance the OV cell(s)

#### **Cells above OV balance**

- Balance continues until V<sub>FC</sub> or OV removed •

- Current stops with OV