# TPS650332-Q1 Automotive Camera PMIC

# 1 Features

- Qualified for automotive applications

- Systematic capability of up to ASIL D and SIL 3 targeted

- Hardware integrity up to ASIL B and SIL 2 targeted

- Advanced diagnostics and protection

- AEC-Q100 grade 1 qualified

- -40°C to +125°C ambient operating temperature range

- Three step-down converters:

- BUCK1 V<sub>IN</sub> range from 4.0 V to 18.3 V

- BUCK1 V<sub>OUT</sub> range from 2.5 V to 4.0 V

- BUCK1 output current up to 1500-mA

- BUCK2 and BUCK3 V<sub>IN</sub> range from 2.5 V to 5.5

- BUCK2 and BUCK3 V<sub>OUT</sub> range from 0.9 V to 1.9 V

- BUCK2 and BUCK3 output current up to 1200mΑ

- Spread-spectrum clock (SSC) generation for reduced EMI

- 2.3-MHz forced fixed switching frequency PWM operation

- One low dropout (LDO) regulator:

- V<sub>IN</sub> range from 2.5 V to 5.5 V

- V<sub>OUT</sub> range from 1.8 V to 3.3 V

- Low noise and high PSRR

- Adjustable output voltage through I<sup>2</sup>C

- Up to 300-mA output current

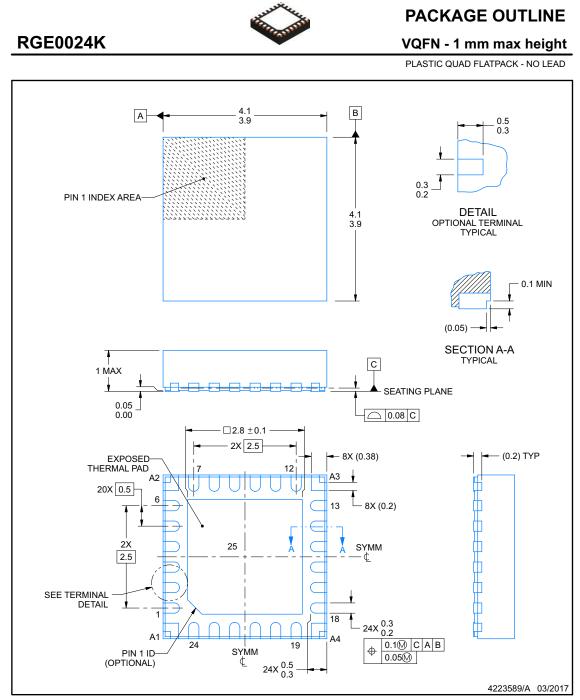

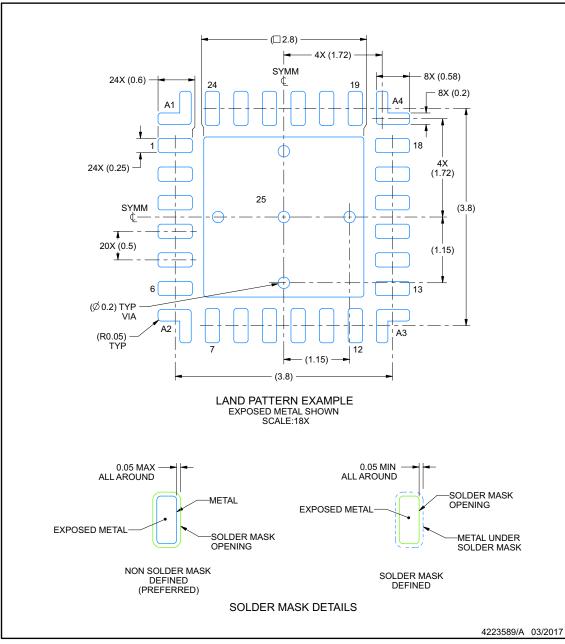

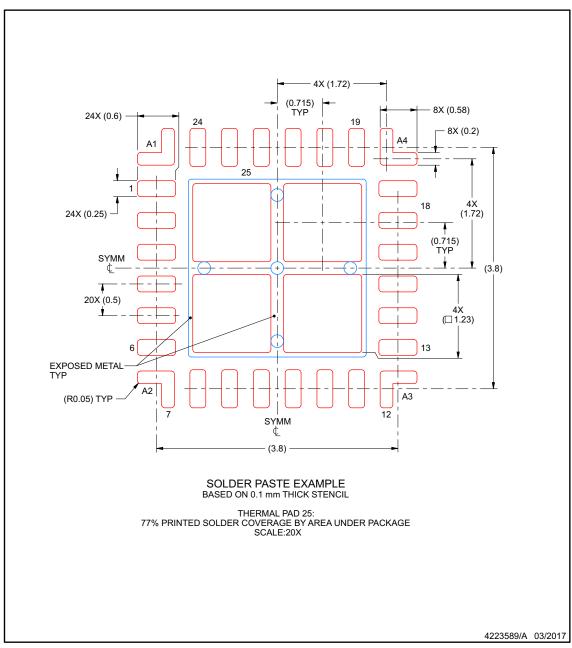

- 4.0-mm × 4.0-mm 24-pin VQFN with wettable flanks

# 2 Applications

- Automotive camera modules

- Surround view camera modules

- Rear view camera modules

- Driver monitor camera modules

- Power over coax (POC) camera modules

- E-mirror camera modules

- Front view camera modules

## **3 Description**

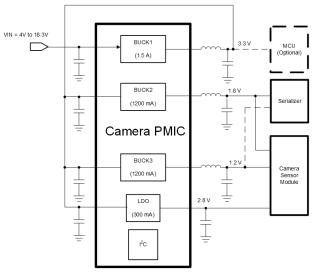

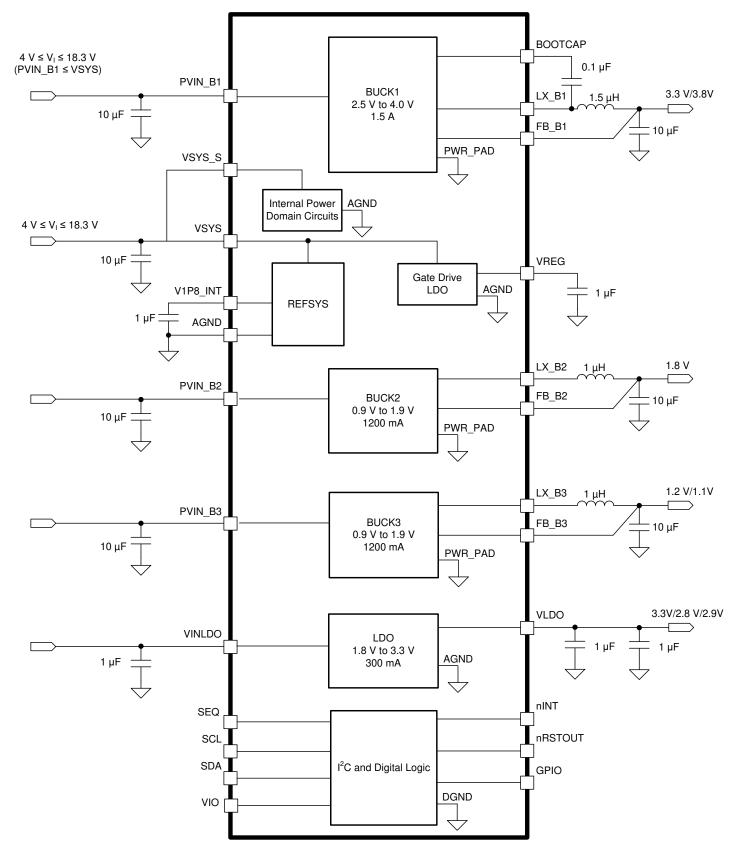

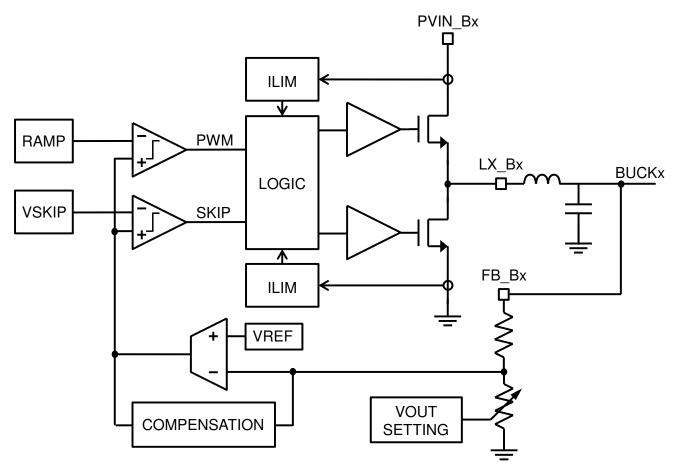

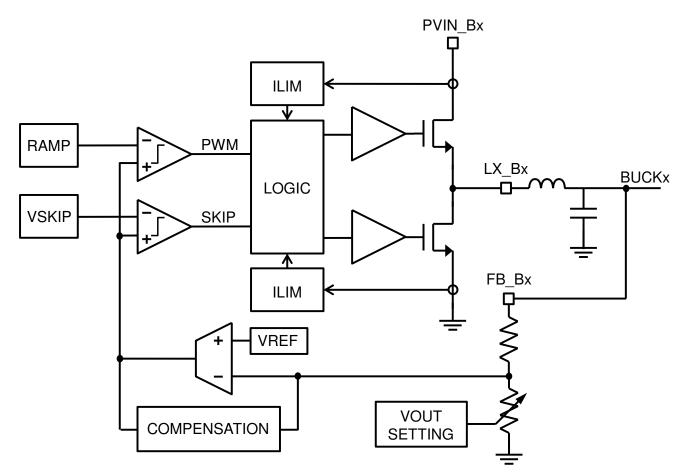

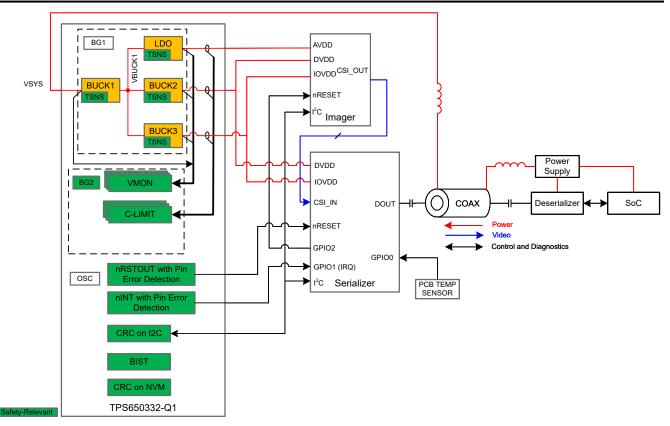

The TPS650332-Q1 device is a highly integrated power management IC for automotive camera modules. This device combines three step-down converters and one low-dropout (LDO) regulator. The BUCK1 step-down converter has an input voltage range up to 18.3 V for connections to power over coax (PoC). All converters operate in a forced fixedfrequency PWM mode. The LDO can supply 300 mA and operate with an input voltage range from 2.5 V to 5.5 V. The step-down converters and the LDO have separate voltage inputs that enable maximum design and sequencing flexibility.

The TPS650332-Q1 is available in a 24-pin VQFN package (4.00 mm × 4.00 mm).

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | PACKAGE   | BODY SIZE (NOM)   |  |

|----------------------------|-----------|-------------------|--|

| TPS650332-Q1               | VQFN (24) | 4.00 mm × 4.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

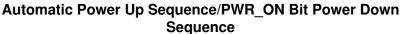

**TPS650332-Q1 Application Circuit**

# **Table of Contents**

| 1 Features1                           |

|---------------------------------------|

| 2 Applications1                       |

| 3 Description1                        |

| 4 Revision History                    |

| 5 Pin Configuration and Functions     |

| 6 Specifications                      |

| 6.1 Absolute Maximum Ratings5         |

| 6.2 ESD Ratings5                      |

| 6.3 Recommended Operating Conditions5 |

| 6.4 Thermal Information6              |

| 6.5 Reference System6                 |

| 6.6 BUCK1 Converter7                  |

| 6.7 BUCK2 and BUCK3 Converters8       |

| 6.8 Low Noise LDO9                    |

| 6.9 VIO10                             |

| 6.10 SEQ11                            |

| 6.11 nINT11                           |

| 6.12 nRSTOUT11                        |

| 6.13 GPIO                             |

| 6.14 I <sup>2</sup> C Interface12     |

| 6.15 Monitor Ref Sys 13               |

| 6.16 Monitor BUCK113                  |

| 6.17 Monitor BUCK214                  |

| 6.18 Monitor BUCK314                  |

| 6.19 Monitor LDO15                    |

| 6.20 Monitor Temperature Sensor       |

| 6.21 Monitor VREG                     |

| Monitor Loss of Ground 16             |

| 6.22 Monitor V1P8_INT                           | 16              |

|-------------------------------------------------|-----------------|

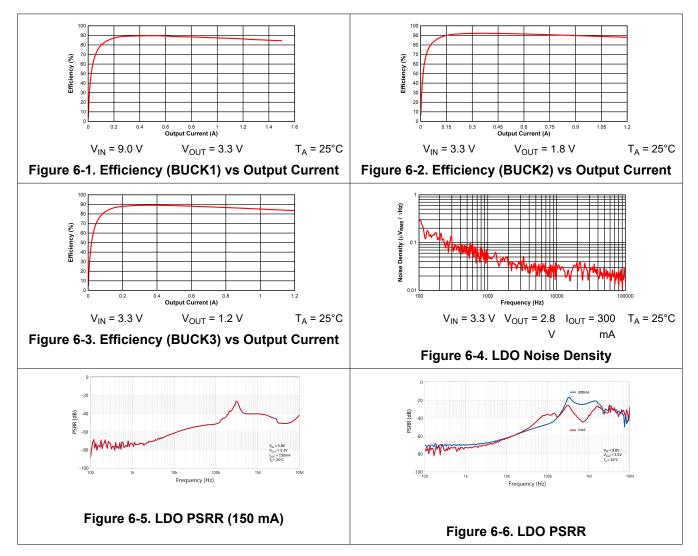

| 6.23 Typical Characteristics                    | 18              |

| 7 Detailed Description                          |                 |

| 7.1 Overview                                    | 19              |

| 7.2 Functional Block Diagram                    | <mark>20</mark> |

| 7.3 Feature Description                         |                 |

| 7.4 Safety Description                          |                 |

| 7.5 Device Functional Modes                     | 40              |

| 7.6 Register Map                                |                 |

| 8 Application and Implementation                |                 |

| 8.1 Application Information                     |                 |

| 8.2 Typical Application                         |                 |

| 9 Power Supply Recommendations                  | 107             |

| 10 Layout                                       |                 |

| 10.1 Layout Guidelines                          |                 |

| 10.2 Layout Example                             |                 |

| 11 Device and Documentation Support             |                 |

| 11.1 Device Support                             |                 |

| 11.2 Receiving Notification of Documentation Up |                 |

| 11.3 Support Resources                          |                 |

| 11.4 Trademarks                                 |                 |

| 11.5 Electrostatic Discharge Caution            |                 |

| 11.6 Glossary                                   | 109             |

| 12 Mechanical, Packaging, and Orderable         |                 |

| Information                                     |                 |

| 12.1 Package Option Addendum                    |                 |

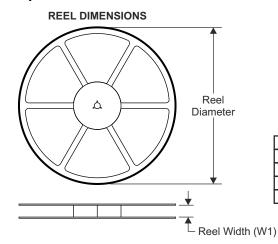

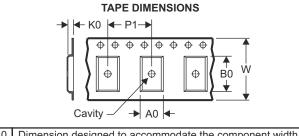

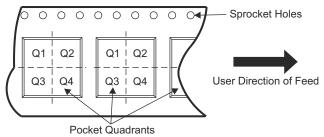

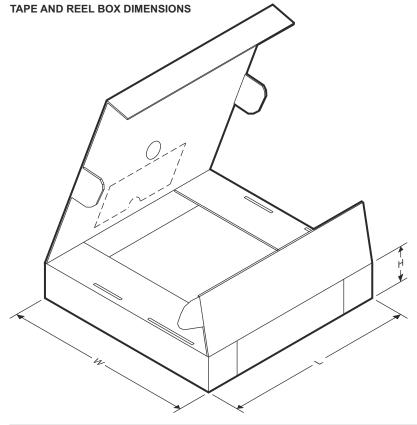

| 12.2 Tape and Reel Information                  | 111             |

|                                                 |                 |

**4 Revision History** NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | Changes from Revision * (November 2021) to Revision A (September 2022) Pa                          |         |  |  |  |  |

|---|----------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| • | Made cosmetic changes to registers with addresses 1Ah, 1Bh, 1Ch, 1Dh, 1Fh, 20h, 21h, 22h, 23h, 24h | n, 25h, |  |  |  |  |

|   | and 26h                                                                                            | 43      |  |  |  |  |

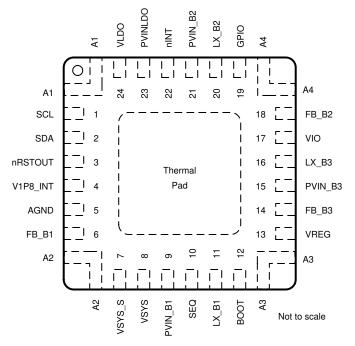

# **5** Pin Configuration and Functions

Figure 5-1 shows the 24-pin QFN pin assignments.

| NO. | NAME     | TYPE | DESCRIPTION                                                                                                                                   |

|-----|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCL      | Ι    | I2C Clock Line                                                                                                                                |

| 2   | SDA      | I/O  | I2C Data Line                                                                                                                                 |

| 3   | nRSTOUT  | 0    | Reset Output                                                                                                                                  |

| 4   | V1P8_INT | 0    | Internal Reference Voltage - For Internal Use Only                                                                                            |

| 5   | AGND     | GND  | Analog Ground                                                                                                                                 |

| 6   | FB_B1    | Ι    | BUCK1 (Mid Voltage Step-Down Converter) Feedback                                                                                              |

| 7   | VSYS_S   | PWR  | Device Input Power for Safety (Connect externally to the VSYS pin)                                                                            |

| 8   | VSYS     | PWR  | Device Input Power (Connect externally to the VSYS_S pin)                                                                                     |

| 9   | PVIN_B1  | PWR  | BUCK1 (Mid Voltage Step-Down Converter) Input Voltage. Apply the voltage on PVIN_B1 at the same time or after the voltage on VSYS is applied. |

| 10  | SEQ      | Ι    | Sequence Control Pin                                                                                                                          |

| 11  | LX_B1    | 0    | BUCK1 (Mid Voltage Step-Down Converter) Switch Node                                                                                           |

| 12  | BOOT     | 0    | BOOTCAP pin for BUCK1 (Mid Voltage Step-Down Converter)                                                                                       |

| 13  | VREG     | 0    | Gate Drive LDO Output for BUCK1 (Mid Voltage Step Down Converter)                                                                             |

| 14  | FB_B3    | I    | BUCK3 (Low Voltage Step-Down Converter) Feedback                                                                                              |

| 15  | PVIN_B3  | PWR  | BUCK3 (Low Voltage Step-Down Converter) Input Voltage. Apply the voltage on PVIN_B3 at the same time or after the voltage on VSYS is applied. |

| 16  | LX_B3    | 0    | BUCK3 (Low Voltage Step-Down Converter) Switch Node                                                                                           |

| 17  | VIO      | I    | IO Supply Voltage pin                                                                                                                         |

| 18  | FB_B2    | I    | BUCK2 (Low Voltage Step-Down Converter) Feedback                                                                                              |

| 19  | GPIO     | I/O  | General Purpose Input/Output                                                                                                                  |

| NO.                                                                            | NAME                  | TYPE                                                                                                                  | DESCRIPTION                                                                                               |

|--------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 20                                                                             | LX_B2                 | 0                                                                                                                     | BUCK2 (Low Voltage Step-Down Converter) Switch Node                                                       |

| 21                                                                             | PVIN_B2               | PWR BUCK2 (Low Voltage Step-Down Converter) Inp<br>PWR voltage on PVIN_B2 at the same time or after th<br>is applied. |                                                                                                           |

| 22                                                                             | 22 nINT O             |                                                                                                                       | Interrupt Request Output                                                                                  |

| 23                                                                             | PVINLDO               | PWR                                                                                                                   | LDO Input Voltage. Apply the voltage on PVINLDO at the same time or after the voltage on VSYS is applied. |

| 24                                                                             | VLDO                  | 0                                                                                                                     | LDO Output Voltage                                                                                        |

| A1-A4 Corner Anchors GND Corner Anchors for package stability (i<br>Power Pad) |                       | Corner Anchors for package stability (internally connected to the Power Pad)                                          |                                                                                                           |

|                                                                                | PowerPad <sup>™</sup> | GND                                                                                                                   | Device Thermal Pad and PGND connection. Must be connected to main ground plane for proper operation.      |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| POS      |                                                |                                                             | MIN  | MAX                      | UNIT |

|----------|------------------------------------------------|-------------------------------------------------------------|------|--------------------------|------|

| 4.1.1    |                                                | VSYS, VSYS_S                                                | -0.3 | 20                       |      |

| 4.1.2    |                                                | PVIN_B1                                                     | -0.3 | 20                       |      |

| 4.1.3    |                                                | FB_B1                                                       | -0.3 | 5.5                      |      |

| 4.1.4    |                                                | BOOT                                                        | -0.3 | V <sub>LX_B1</sub> + 5.5 |      |

| 4.1.5    | Input voltage                                  | PVIN_B2, PVIN_B3, PVINLDO                                   | -0.3 | 6.0                      | V    |

| 4.1.6    |                                                | FB_B2, FB_B3                                                | -0.3 | 5.5                      |      |

| 4.1.7    |                                                | VIO                                                         | -0.3 | 5.5                      |      |

| 4.1.8    |                                                | SEQ                                                         | -0.3 | 20                       |      |

| 4.1.9    |                                                | GPIO                                                        | -0.3 | 5.5                      |      |

| 4.1.10   |                                                | LX_B1 <sup>(2)</sup>                                        | -2.0 | 20                       |      |

| 4.1.10.a |                                                | LX_B1 for spikes with a pulse width less than 10ns $^{(2)}$ | -2.0 | 22                       |      |

| 4.1.11   |                                                | LX_B2, LX_B3 <sup>(2)</sup>                                 | -2.0 | 6.0                      |      |

| 4.1.12   | Output voltage                                 | VLDO                                                        | -0.3 | 5.0                      | V    |

| 4.1.13   |                                                | VREG                                                        | -0.3 | 5.5                      |      |

| 4.1.14   | _                                              | V1P8_INT                                                    | -0.3 | 1.98                     |      |

| 4.1.15   |                                                | SDA, SCL                                                    | -0.5 | 5.0                      |      |

| 4.1.16   |                                                | nINT, nRSTOUT                                               | -0.3 | 5.0                      |      |

| 4.1.20   | Operating junction temperature, T <sub>J</sub> |                                                             |      | 150                      | °C   |

| 4.1.21   | Storage tempera                                | ture, T <sub>stg</sub>                                      |      | 150                      | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Minimum voltage reduces from -2.0V to -0.4V at  $T_A = 125^{\circ}C$ .

# 6.2 ESD Ratings

| POS   |  |  | VALUE                      | UNIT                                                    |      |   |

|-------|--|--|----------------------------|---------------------------------------------------------|------|---|

| 4.2.1 |  |  | Human body model (HBM), pe | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |      |   |

| 4.2.2 |  |  |                            | Corner pins (1, 6, 7, 12, 13, 18, 19 and 24)            | ±750 | V |

| 4.2.3 |  |  | (CDM), per AEC Q100-011    | Other pins                                              | ±500 |   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

| POS   |                      |                                                 | MIN  | NOM | MAX                 | UNIT |

|-------|----------------------|-------------------------------------------------|------|-----|---------------------|------|

| 4.3.1 | VSYS,<br>VSYS_S      | Input voltage                                   | 4    |     | 18.3                | V    |

| 4.3.2 | PVIN_B1              | BUCK1 Input Voltage (PVIN_B1 ≤ VSYS/<br>VSYS_S) | 4    |     | 18.3                | V    |

| 4.3.3 | BOOT                 | BUCK1 Bootstrap Pin                             | 0    |     | $V_{LX_{B1}} + 5.0$ | V    |

| 4.3.4 | LX_B1                | BUCK1 Switch Node Pin <sup>(1)</sup>            | -0.5 |     | 20.0                | V    |

| 4.3.5 | C <sub>PVIN_B1</sub> | BUCK1 Input Capacitance                         | 6.8  | 10  |                     | uF   |

# 6.3 Recommended Operating Conditions (continued)

Over operating free-air temperature range (unless otherwise noted)

| POS    |                                               |                                                 | MIN  | NOM MAX | UNIT |

|--------|-----------------------------------------------|-------------------------------------------------|------|---------|------|

| 4.3.6  | FB_B1                                         | BUCK1 Feedback pin                              | 0    | 4.0     | V    |

| 4.3.7  | FB_B2,<br>FB_B3                               | BUCK2 and BUCK3 Feedback pin                    | 0    | 2.0     | V    |

| 4.3.8  | PVIN_B2,<br>PVIN_B3                           | BUCK2 and BUCK3 Input Voltage Pins              | 0    | 5.5     | V    |

| 4.3.9  | LX_B2, LX_B3                                  | BUCK2 and BUCK3 Switch Node Pins <sup>(1)</sup> | -0.5 | 5.5     | V    |

| 4.3.10 | C <sub>PVIN_B2,</sub><br>C <sub>PVIN_B3</sub> | BUCK2 and BUCK3 Input Capacitance               | 6.8  | 10      | uF   |

| 4.3.11 | PVINLDO                                       | LDO Input Voltage                               | 0    | 5.5     | V    |

| 4.3.12 | LDOOUT                                        | LDO Output Voltage Range                        | 0    | 3.3     | V    |

| 4.3.13 | C <sub>LDOOUT</sub>                           | LDO Output Capacitance                          | 1    | 4       | uF   |

| 4.3.14 | VREG                                          |                                                 | 0    | 5.0     | V    |

| 4.3.15 | V1P8_INT                                      |                                                 | 0    | 1.85    | V    |

| 4.3.16 | VIO                                           |                                                 | 0    | 3.3     | V    |

| 4.3.17 | nINT,<br>nRSTOUT,<br>SEQ, GPIO                |                                                 | 0    | 3.3     | V    |

| 4.3.18 | SCL and SDA                                   |                                                 | 0    | 3.3     | V    |

| 4.3.19 | T <sub>A</sub>                                | Operating free-air temperature                  | -40  | 125     | °C   |

| 4.3.20 | TJ                                            | Operating junction temperature                  | -40  | 150     | °C   |

(1) Minimum voltage reduces from -0.5V to -0.4V at  $T_A = 125^{\circ}C$ .

#### **6.4 Thermal Information**

|                               |                                              | RGE     |      |

|-------------------------------|----------------------------------------------|---------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | VQFN    | UNIT |

|                               |                                              | 24 PINS | _    |

| R <sub>OJA</sub>              | Junction-to-ambient thermal resistance       | 31.7    | °C/W |

| R <sub>OJC(top)</sub>         | Junction-to-case (top) thermal resistance    | 27.2    | °C/W |

| R <sub>OJB</sub>              | Junction-to-board thermal resistance         | 10.5    | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.3     | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 10.5    | °C/W |

| R <sub>OJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 1.2     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Reference System

| POS    |                            | PARAMETER                    | TEST CONDITIONS                                                                     | MIN | TYP M | x  | UNIT |  |  |  |

|--------|----------------------------|------------------------------|-------------------------------------------------------------------------------------|-----|-------|----|------|--|--|--|

| ELECTE | ELECTRICAL CHARACTERISTICS |                              |                                                                                     |     |       |    |      |  |  |  |

| 4.5.1  | VSYS ,<br>VSYS_S           | Operating Input Voltage      |                                                                                     | 4   | 18    | .3 | V    |  |  |  |

| 4.5.5  | I <sub>Q_ON</sub>          | Quiescent Current - On State | Measured on the VSYS pin, VSYS<br>≥ 4.0V, VSYS and VSYS_S are<br>connected together |     |       | 10 | mA   |  |  |  |

# 6.5 Reference System (continued)

Over operating free-air temperature range (unless otherwise noted)

| POS    |                       | PARAMETER                     | TEST CONDITIONS                                                                 | MIN  | TYP  | MAX | UNIT |

|--------|-----------------------|-------------------------------|---------------------------------------------------------------------------------|------|------|-----|------|

| 4.5.6  | I <sub>Q_OFF</sub>    | Quiescent Current - Off State | VSYS = 0V to 3.5V, slow ramp rate,<br>VSYS and VSYS_S are connected<br>together |      | 100  | 150 | uA   |

| 4.5.7  | C <sub>VSYS</sub>     | VSYS external Capacitance     |                                                                                 | 4.0  | 10   |     | uF   |

| 4.5.8  | V <sub>V1P8_INT</sub> | Internal LDO Output Voltage   | VIN = VSYS                                                                      | 1.7  | 1.85 | 2.0 | V    |

| 4.5.9  | C <sub>V1P8_INT</sub> | V1P8_INT external Capacitance |                                                                                 | 0.68 | 1    | 1.4 | uF   |

| 4.5.10 | V <sub>VREG</sub>     | BUCK1 Gate Drive LDO          | VIN = VSYS ≥ 4.3                                                                | 4.0  | 4.5  | 5.0 | V    |

| 4.5.12 | C <sub>VREG</sub>     | VREG external Capacitance     |                                                                                 | 0.68 | 1    | 1.4 | uF   |

# 6.6 BUCK1 Converter

| POS    |                                     |                                            | TEST CONDITIONS                                                                                       | MIN  | TYP | MAX  | UNIT |

|--------|-------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------|------|-----|------|------|

| ELECT  | RICAL CHARA                         | CTERISTICS                                 | · · · · ·                                                                                             |      |     |      |      |

| 4.6.1  | V <sub>IN</sub>                     | Input voltage                              |                                                                                                       | 4    |     | 18.3 | V    |

| 4.6.6  | I <sub>OFF_STATE</sub>              | Off State Current                          | BUCK1 disabled measured at<br>PVIN_B1                                                                 |      |     | 40   | μA   |

| 4.6.7  | V <sub>OUT_LOW_VI</sub>             | Output voltage - Low VIN Range             | V <sub>IN</sub> = 4.0V to 18.3V                                                                       | 2.5  | 3.3 | 3.5  | V    |

| 4.6.8  | V <sub>OUT_HIGH_VI</sub>            | Output voltage - High VIN Range            | V <sub>IN</sub> = 4.5V to 18.3V                                                                       | 2.5  | 3.8 | 4.0  | V    |

| 4.6.10 | V <sub>OUT_ACCUR</sub><br>ACY_DC    | DC Output Voltage Accuracy                 | V <sub>IN</sub> = 12.0V, I <sub>OUT</sub> = I <sub>OUT_MAX</sub> , V <sub>OUT</sub><br>= 2.5V to 4.0V | -1.5 |     | 1.5  | %    |

| 4.6.11 | V <sub>OUT_ACCUR</sub><br>ACY_TOT   | Total Output Voltage Accuracy (DC<br>+ AC) |                                                                                                       | -5   |     | 5    | %    |

| 4.6.12 | R <sub>FB_INPUT</sub>               | Feedback input impedance                   | Converter enabled                                                                                     | 100  |     | 900  | KΩ   |

| 4.6.13 | V <sub>LOAD_REGU</sub>              | DC Load Regulation                         | $V_{IN}$ = 12.0V, $V_{OUT}$ = 3.3V, $I_{OUT}$ = 0<br>to $I_{OUT_MAX}$                                 |      |     | 0.1  | %/A  |

| 4.6.15 | V <sub>LINE_REGUL</sub>             | DC Line Regulation                         | $V_{\text{IN}}$ = 4.0V to 18.3V, $I_{\text{OUT}}$ = 500mA and 1500mA                                  |      |     | 1.5  | %    |

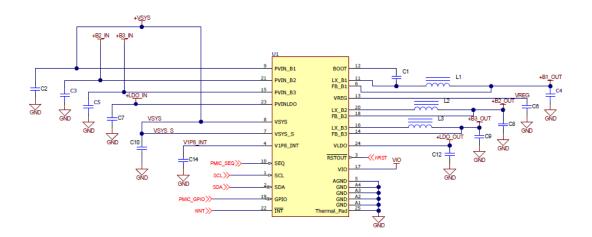

| 4.6.16 | V <sub>LOAD_TRANS</sub>             | Load Transient                             | $V_{IN}$ = 12.0V, $V_{OUT}$ = 3.3V, $I_{OUT}$ = 1mA to 50% of $I_{OUT\_MAX}$ in 1us,                  |      |     | 100  | mV   |

| 4.6.18 | V <sub>LINE_TRANSI</sub>            | Line Transient                             | $V_{IN}$ = 4.0V to 18.3V in 100uS, $V_{OUT}$ = 3.3V, $I_{OUT}$ = 1mA and $I_{OUT\_MAX}$ ,             |      |     | 100  | mV   |

| 4.6.19 | V <sub>RIPPLE_PWM</sub>             | PWM Mode                                   | $C_{OUT}$ = 10uF, X7R, ESR =<br>10mohms, L = 1.5uH, DCR = 110<br>m $\Omega$ , QFN Package             |      |     | 20   | mV   |

| 4.6.21 | I <sub>OUT_MAX</sub> <sup>(1)</sup> | Maximum Operating Current                  |                                                                                                       |      |     | 1.5  | А    |

| 4.6.22 | I <sub>CURRENT_LIM</sub>            | Short Circuit Current Limit                | V <sub>IN</sub> = (7.5 x 10 <sup>6</sup> ) x L, V <sub>OUT</sub> = 0V                                 | 1.8  | 2.4 | 3    | А    |

| 4.6.23 | R <sub>DSON_HS</sub>                | High Side MOSFET On Resistance             | Measured Pin to Pin                                                                                   |      |     | 300  | mΩ   |

| 4.6.24 | R <sub>DSON_LS</sub>                | Low Side MOSFET On Resistance              | Measured Pin to Pin                                                                                   |      |     | 165  | mΩ   |

| 4.6.25 | R <sub>DISCHARGE</sub>              | Output Discharge Resistance                | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '00'                         |      | off |      | KΩ   |

| 4.6.26 | R <sub>DISCHARGE</sub>              | Output Discharge Resistance                | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '01'                         | 60   | 125 | 250  | Ω    |

| 4.6.27 | R <sub>DISCHARGE</sub>              | Output Discharge Resistance                | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '10'                         | 120  | 250 | 450  | Ω    |

# TPS650332-Q1

SLVSG12A - NOVEMBER 2021 - REVISED SEPTEMBER 2022

## 6.6 BUCK1 Converter (continued)

Over operating free-air temperature range (unless otherwise noted)

| POS    |                                        | PARAMETER                                                                       | TEST CONDITIONS                                                               | MIN  | TYP | MAX  | UNIT   |

|--------|----------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|-----|------|--------|

| 4.6.28 | R <sub>DISCHARGE</sub>                 | Output Discharge Resistance                                                     | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '11' | 240  | 500 | 850  | Ω      |

| 4.6.34 | L <sub>SW_1_5</sub>                    | Output Inductance                                                               |                                                                               | 1.0  | 1.5 | 2.0  | μH     |

| 4.6.36 | C <sub>OUT_LC</sub>                    | LC Filter Output capacitance                                                    |                                                                               | 6.8  | 10  | 14   | μF     |

| 4.6.37 | C <sub>BOOT</sub>                      | Boot capacitance                                                                |                                                                               | 0.07 | 0.1 | 0.13 | μF     |

| TIMING | CHARACTER                              | ISTICS                                                                          |                                                                               |      |     |      |        |

| 4.6.50 | V <sub>IN_RAMP_TI</sub><br>ME_NORMAL   | Input voltage Ramp Time under<br>normal operating conditions                    | Input voltage controlled by a pre-<br>regulator. PVIN_B1 = 0V to 10V          | 0.1  |     | 100  | ms     |

| 4.6.51 | V <sub>IN_RAMP_TI</sub><br>ME_HOT_PLUG | Input voltage Ramp Time based on<br>a Hot Plug scenario                         | Hot Plug occurring at the input of the device. PVIN_B1 = 0V to 10V.           |      |     | 1    | V/µs   |

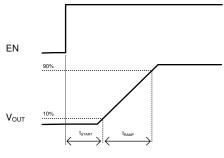

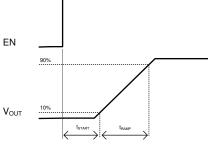

| 4.6.53 | t <sub>START</sub>                     | Start Time                                                                      | Time from completion of I2C command to output voltage at 10%                  |      |     | 200  | μs     |

| 4.6.54 | t <sub>RAMP</sub>                      | Ramp Time                                                                       | Measured from 10% to 90% of target value                                      | 200  | 480 | 800  | μs     |

| SWITCH | ING CHARAC                             | TERISTICS                                                                       |                                                                               |      |     |      |        |

| 4.6.60 | f <sub>SW</sub>                        | Switching Frequency                                                             | PWM - Fixed Frequency                                                         | 2.18 | 2.3 | 2.42 | MHz    |

| 4.6.62 | f <sub>SS_EN</sub>                     | Converter Switching Frequency with Spread Spectrum Enabled                      |                                                                               | 2.05 |     | 2.55 | MHz    |

| 4.6.63 | A <sub>DITHER_TRIA</sub>               | Dither Amplitude of Spread<br>Spectrum Clock for a Triangular<br>Dither pattern |                                                                               |      |     | 150  | KHz    |

| 4.6.64 | f <sub>DITHER_STEP</sub>               | Dither Step frequency                                                           |                                                                               |      |     | 18   | KHz    |

| 4.6.65 | M <sub>DITHER</sub>                    | Dither Slope of Spread Spectrum<br>Clock                                        |                                                                               |      |     | 4.5  | KHz/µs |

(1) Load current capability depends on the Input Voltage and Output Voltage. The following formula can be used to determine the limits.  $V_{IN} = [(R_{DSON} + L_{DCR}) * I_{LOAD}] + (V_{OUT} / 0.9)$

## 6.7 BUCK2 and BUCK3 Converters

| POS     |                                       | PARAMETER                                  | TEST CONDITIONS                                                                                          | MIN  | TYP | MAX | UNIT |

|---------|---------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| ELECT   | RICAL CHARA                           | ACTERISTICS                                | · · · · · · · · · · · · · · · · · · ·                                                                    |      |     |     |      |

| 4.7.1   | V <sub>IN</sub>                       | Input voltage                              |                                                                                                          | 2.5  |     | 5.5 | V    |

| 4.7.3   | I <sub>OFF_STATE</sub>                | Off State Current                          | 2.5V ≤ PVINx ≤ 5.5V. BUCKx<br>Disabled, measured at PVIN_Bx                                              |      |     | 25  | μA   |

| 4.7.5.a | V <sub>OUT</sub>                      | Output voltage -                           | V <sub>IN</sub> = 2.5V to 4.0V                                                                           | 0.9  | 1.2 | 1.9 | V    |

| 4.7.10  | V <sub>OUT_ACCUR</sub>                | DC Output Voltage Accuracy -<br>Overall    | V <sub>IN</sub> = 3.3V, I <sub>OUT</sub> = I <sub>OUT_MAX</sub> , V <sub>OUT</sub> = 0.9V to 1.9V        | -1.5 |     | 1.5 | %    |

| 4.7.11  | V <sub>OUT_ACCUR</sub><br>ACY_DC_1_8V | DC Output Voltage Accuracy                 | V <sub>IN</sub> = 3.3V, I <sub>OUT</sub> = I <sub>OUT_MAX</sub> , V <sub>OUT</sub> = 1.8V                |      |     | 30  | mV   |

| 4.7.12  | V <sub>OUT_ACCUR</sub><br>ACY_DC_1_2V | DC Output Voltage Accuracy                 | V <sub>IN</sub> = 3.3V, I <sub>OUT</sub> = I <sub>OUT_MAX</sub> , V <sub>OUT</sub> = 1.2V                |      |     | 20  | mV   |

| 4.7.13  | V <sub>OUT_ACCUR</sub><br>ACY_TOT     | Total Output Voltage Accuracy (DC<br>+ AC) | $V_{IN}$ = 2.5V to 5.5V, $V_{OUT}$ = 1.2V<br>and 1.8V, $I_{OUT}$ = 1mA to 50% of<br>$I_{OUT_MAX}$ in 1us | -5   |     | 5   | %    |

| 4.7.14  | R <sub>FB_INPUT</sub>                 | Feedback input impedance                   | Converter enabled                                                                                        | 100  |     | 900 | KΩ   |

| 4.7.15  | V <sub>LOAD_REGU</sub>                | DC Load Regulation                         | $V_{IN}$ = 3.3V, $V_{OUT}$ = 1.8V, $I_{OUT}$ = 0 to $I_{OUT\_MAX}$                                       |      |     | 0.1 | %/A  |

| 4.7.16  | V <sub>LINE_REGUL</sub>               | DC Line Regulation                         | $V_{\text{IN}}$ = 2.5V to 5.5V, $V_{\text{OUT}}$ = 1.8V and 1.2V, $I_{\text{OUT}}$ = 250mA and 1000mA    |      |     | 1.5 | %    |

# 6.7 BUCK2 and BUCK3 Converters (continued)

Over operating free-air temperature range (unless otherwise noted)

| POS    |                                  | PARAMETER                                                                       | TEST CONDITIONS                                                                                                                                                                    | MIN  | TYP | MAX  | UNIT   |

|--------|----------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|--------|

| 4.7.18 | V <sub>LOAD_TRANS</sub>          | Load Transient                                                                  | $\label{eq:VIN} \begin{array}{l} V_{IN} = 3.8V,  V_{OUT} = 1.8V \text{ and } 1.2V, \\ I_{OUT} = 1mA \text{ to } 500mA \text{ in } 1us, \end{array}$                                |      |     | 50   | mV     |

| 4.7.19 | V <sub>LINE_TRANSI</sub><br>ENT  | Line Transient                                                                  | $\label{eq:VIN} \begin{array}{l} V_{IN} = 2.5V \text{ to } 5.5V \text{ in } 50uS, \ V_{OUT} \\ = 1.8V \text{ and } 1.2V, \ I_{OUT} = 1mA \text{ and} \\ I_{OUT\_MAX}, \end{array}$ |      |     | 50   | mV     |

| 4.7.20 | V <sub>RIPPLE_PWM</sub><br>_PtoP | PWM Mode                                                                        | C <sub>OUT</sub> = 10uF, X7R, ESR =<br>10mohms, L = 1uH, DCR =<br>60mohms, QFN Package                                                                                             |      |     | 20   | mV     |

| 4.7.22 | I <sub>OUT_MAX</sub>             | Maximum Operating Current                                                       |                                                                                                                                                                                    |      |     | 1.2  | А      |

| 4.7.23 | I <sub>CURRENT_LIM</sub>         | Short Circuit Current Limit                                                     | V <sub>IN</sub> = 3.3V, V <sub>OUT</sub> = 0V                                                                                                                                      | 1.6  | 2.2 | 2.8  | А      |

| 4.7.26 | R <sub>DSON_HS</sub>             | High Side MOSFET On Resistance                                                  | Measured Pin to Pin, V <sub>IN</sub> = 3.8V                                                                                                                                        |      |     | 160  | mΩ     |

| 4.7.27 | R <sub>DSON_LS</sub>             | Low Side MOSFET On Resistance                                                   | Measured Pin to Pin, V <sub>IN</sub> = 3.8V                                                                                                                                        |      |     | 80   | mΩ     |

| 4.7.28 | R <sub>DISCHARGE</sub>           | Output Discharge Resistance                                                     | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '00'.                                                                                                     |      | off |      | KΩ     |

| 4.7.29 | R <sub>DISCHARGE</sub>           | Output Discharge Resistance                                                     | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '01'.                                                                                                     | 60   | 125 | 200  | Ω      |

| 4.7.30 | R <sub>DISCHARGE</sub>           | Output Discharge Resistance                                                     | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '10'.                                                                                                     | 120  | 250 | 400  | Ω      |

| 4.7.31 | R <sub>DISCHARGE</sub>           | Output Discharge Resistance                                                     | Active only when converter is disabled, R <sub>DISCHARGE</sub> Setting = '11'.                                                                                                     | 240  | 500 | 800  | Ω      |

| 4.7.37 | L <sub>SW</sub>                  | Output Inductance                                                               |                                                                                                                                                                                    | 0.68 | 1   | 1.2  | μH     |

| 4.7.38 | C <sub>OUT</sub>                 | Output capacitance                                                              |                                                                                                                                                                                    | 6.8  | 10  | 12   | μF     |

| TIMING | CHARACTER                        | ISTICS                                                                          | · · · · · ·                                                                                                                                                                        |      |     |      |        |

| 4.7.50 | t <sub>START</sub>               | Start Time                                                                      | Time from completion of I2C command to output voltage at 10%                                                                                                                       |      |     | 200  | μs     |

| 4.7.51 | t <sub>RAMP</sub>                | Ramp Time                                                                       | Measured from 10% to 90% of target value                                                                                                                                           | 200  | 480 | 800  | μs     |

| SWITCH | HING CHARAC                      | TERISTICS                                                                       | · · · · · ·                                                                                                                                                                        |      |     |      |        |

| 4.7.60 | f <sub>SW</sub>                  | Switching Frequency                                                             | PWM - Fixed Frequency                                                                                                                                                              | 2.18 | 2.3 | 2.42 | MHz    |

| 4.7.62 | f <sub>SS_EN</sub>               | Converter Switching Frequency with Spread Spectrum Enabled                      |                                                                                                                                                                                    | 2.05 |     | 2.55 | MHz    |

| 4.7.63 | A <sub>DITHER_TRIA</sub><br>N    | Dither Amplitude of Spread<br>Spectrum Clock for a Triangular<br>Dither pattern |                                                                                                                                                                                    |      |     | 150  | KHz    |

| 4.7.64 | f <sub>DITHER_STEP</sub>         | Dither Step frequency                                                           |                                                                                                                                                                                    |      |     | 18   | KHz    |

| 4.7.65 | M <sub>DITHER</sub>              | Dither Slope of Spread Spectrum<br>Clock                                        |                                                                                                                                                                                    |      |     | 4.5  | KHz/µs |

|        | 1                                | 1                                                                               |                                                                                                                                                                                    |      |     |      |        |

## 6.8 Low Noise LDO

| POS     |                                      | PARAMETER                                                                                   | TEST CONDITIONS                                                                         | MIN | TYP | MAX | UNIT |

|---------|--------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|------|

| ELECTR  | RICAL CHA                            | ARACTERISTICS                                                                               |                                                                                         |     |     |     |      |

| 4.8.1.a | V <sub>IN</sub>                      | Input voltage                                                                               |                                                                                         | 2.5 |     | 5.5 | V    |

| 4.8.3   | V <sub>OUT</sub>                     | Output voltage                                                                              | V <sub>IN</sub> = 2.5V to 3.8V                                                          | 1.8 |     | 3.3 | V    |

| 4.8.5   | R <sub>Bypass</sub>                  | Bypass resistance                                                                           | V <sub>IN</sub> = 3.3V, I <sub>OUT</sub> = 100mA, LDO<br>Bypass Enabled                 |     |     | 1   | Ω    |

| 4.8.6   | V <sub>OUT_DC</sub><br>_accura<br>cy | Total DC accuracy including DC load<br>and line regulation for all valid output<br>voltages | For all valid operating conditions,<br>measured after the output voltage has<br>settled | -1% |     | 1%  |      |

# 6.8 Low Noise LDO (continued)

Over operating free-air temperature range (unless otherwise noted)

| POS    |                                 | PARAMETER                        | TEST CONDITIONS                                                                                                                                                                      | MIN | TYP | MAX | UNIT              |

|--------|---------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------------|

| 4.8.11 | V <sub>LOAD_T</sub><br>RANSIENT | Load Transient                   | $\label{eq:VIN} \begin{array}{l} V_{IN} = 3.3V, \ V_{OUT} = 2.80V, \ I_{OUT} = 20\% \\ of \ I_{OUT\_MAX} \ to \ 80\% \ of \ I_{OUT\_MAX} \ in \ 1us, \\ C_{OUT} = 2.2uF \end{array}$ | -25 |     | 25  | mV                |

| 4.8.12 | V <sub>LINE_TR</sub><br>ANSIENT | Line Transient                   | VIN step = 600 mVPP, $T_R = T_F = 10$<br>µs, LDO not in dropout condition, $I_{OUT}$<br>= 1mA and $I_{OUT_MAX2}$                                                                     | -25 |     | 25  | mV                |

| 4.8.13 | V <sub>DROPO</sub><br>UT        | Dropout Voltage                  | For full $V_{\mbox{\scriptsize IN}}$ range and max operating current                                                                                                                 |     | 150 | 300 | mV                |

| 4.8.18 | NOISE <sub>R</sub><br>MS        | RMS Noise                        | f=100Hz to 100KHz, V <sub>IN</sub> = 3.3V, I <sub>OUT</sub> = 300mA, V <sub>OUT</sub> = 2.8V and 1.8V                                                                                |     | 15  |     | uV <sub>RMS</sub> |

| 4.8.19 | I <sub>OUT_MAX</sub>            | Maximum Operating Current low    |                                                                                                                                                                                      |     |     | 150 | mA                |

| 4.8.20 | I <sub>OUT_MAX</sub>            | Maximum Operating Current high   |                                                                                                                                                                                      |     |     | 300 | mA                |

| 4.8.21 | I <sub>CURREN</sub><br>T_LIMIT1 | Short Circuit Current Limit low  | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 0VTested under a<br>pulsed load condition                                                                                                 | 200 |     | 450 | mA                |

| 4.8.22 | I <sub>CURREN</sub><br>T_LIMIT2 | Short Circuit Current Limit high | $V_{IN}$ = 3.6V, $V_{OUT}$ = 0VTested under a pulsed load condition                                                                                                                  | 400 |     | 900 | mA                |

| 4.8.23 | I <sub>IN_RUSH</sub>            | LDO inrush current               | VIN = 3.3V and then LDO is enabled.                                                                                                                                                  |     |     | 650 | mA                |

| 4.8.24 |                                 |                                  | Active only when converter is disabled,<br>R <sub>DISCHARGE_OTP</sub> = '00'                                                                                                         | 35  | 50  | 65  | KΩ                |

| 4.8.25 | R <sub>DISCHA</sub>             | Output Discharge Resistance      | Active only when converter is disabled,<br>R <sub>DISCHARGE_OTP</sub> = '01'                                                                                                         | 60  | 125 | 200 | Ω                 |

| 4.8.26 | RGE                             |                                  | Active only when converter is disabled,<br>R <sub>DISCHARGE_OTP</sub> = '10'                                                                                                         | 120 | 250 | 400 | Ω                 |

| 4.8.27 |                                 |                                  | Active only when converter is disabled,<br>R <sub>DISCHARGE_OTP</sub> = '11'                                                                                                         | 240 | 500 | 800 | Ω                 |

| 4.8.28 | I <sub>Qoff</sub>               | Quiescent current off mode       |                                                                                                                                                                                      |     |     | 2   | μA                |

| 4.8.29 | I <sub>Qon</sub>                | Quiescent current on mode        | lload = 0A                                                                                                                                                                           |     |     | 40  | μA                |

| 4.8.31 | C <sub>IN</sub>                 | Input filtering capacitance      |                                                                                                                                                                                      | 1   |     |     | μF                |

| 4.8.32 | C <sub>OUT</sub>                | Output filtering capacitance     |                                                                                                                                                                                      | 1   |     | 4   | μF                |

| 4.8.34 | C <sub>ESR</sub>                | Filtering capacitor ESR max      | 1MHz to 10MHz                                                                                                                                                                        |     | 10  | 20  | mΩ                |

| TIMING | CHARACT                         | ERISTICS                         |                                                                                                                                                                                      |     |     |     |                   |

| 4.8.50 | t <sub>START</sub>              | Start Time                       | Time from completion of I2C command to output voltage at 10%                                                                                                                         |     |     | 150 | us                |

| 4.8.52 | t <sub>RAMP</sub>               | Ramp Time                        | Measured from 0.5V to 90% of target value                                                                                                                                            |     |     | 350 | us                |

| 4.8.53 | t <sub>RAMP_SL</sub><br>EW      | Ramp Up Slew Rate                | Measured from 0.5V to 90% of target value                                                                                                                                            |     |     | 25  | mv/us             |

| 4.8.54 | t <sub>REG</sub>                | Time to regulation               | From 90% to within +-2% of target                                                                                                                                                    |     |     | 100 | us                |

# 6.9 VIO

| POS    |                     | PARAMETER          | TEST CONDITIONS                                          | MIN | ТҮР | MAX | UNIT |

|--------|---------------------|--------------------|----------------------------------------------------------|-----|-----|-----|------|

| ELECTE | RICAL CHARA         | ACTERISTICS        |                                                          |     |     |     |      |

| 4.9.1  | V <sub>IN_VIO</sub> | VIC) Input voltade | VIO present at the same time or<br>after VREG is present | 1.8 |     | 3.6 | V    |

# 6.9 VIO (continued)

Over operating free-air temperature range (unless otherwise noted)

| POS   |                                | PARAMETER                                                                                                                            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| 4.9.2 | I <sub>IN_VIO</sub>            | Maximum input current on the VIO<br>pin (assumes all inputs, outputs<br>and input/outputs sourcing 2mA of<br>current simultaneously) | VIO = 3.6V      |     |     | 8   | mA   |

| 4.9.3 | I <sub>IN_VIO_STATI</sub><br>C | Maximum input current on the VIO pin when all buffers are static.                                                                    | VIO = 3.6V      |     |     | 10  | μΑ   |

| 4.9.5 | C <sub>IN_VIO</sub>            | Internal input pin capacitance on VIO pin                                                                                            |                 |     |     | 30  | pF   |

# 6.10 SEQ

Over operating free-air temperature range (unless otherwise noted)

| POS     |                       | PARAMETER                                      | TEST CONDITIONS       | MIN  | TYP | MAX  | UNIT |

|---------|-----------------------|------------------------------------------------|-----------------------|------|-----|------|------|

| ELECTE  | RICAL CHAR            | ACTERISTICS                                    | · ·                   |      |     |      |      |

| 4.10.1  | VIL                   | Low-level input voltage                        | VBIAS = VIO           |      |     | 0.54 | V    |

| 4.10.2  | V <sub>IH</sub>       | High-level input voltage                       | VBIAS = VIO           | 1.26 |     |      | V    |

| 4.10.3  | I <sub>LKG</sub>      | Input leakage current                          | VBIAS = VIO           |      |     | 4    | μA   |

| 4.10.4  | R <sub>INT_PD</sub>   | Internal pull-down resistance                  | V <sub>SEQ</sub> = 1V | 1    |     | 2    | MΩ   |

| 4.10.5  | C <sub>IN</sub>       | Internal input pin capacitance                 |                       |      |     | 10   | pF   |

| TIMING  | CHARACTE              | RISTICS                                        |                       |      |     | I    |      |

| 4.10.10 | t <sub>DEGLITCH</sub> | Deglitch time on both rising and falling edges |                       | 8    |     | 12   | μs   |

## 6.11 nINT

Over operating free-air temperature range (unless otherwise noted)

| POS     |                        | PARAMETER                                | TEST CONDITIONS                                                  | MIN | TYP | MAX | UNIT |

|---------|------------------------|------------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|

| ELECTR  | RICAL CHARA            | CTERISTICS                               |                                                                  |     |     | ·   |      |

| 4.11.1  | V <sub>OL_OD</sub>     | Low-level output voltage (open drain)    | VIO = 1.8V, I <sub>OL</sub> = 2mA                                |     |     | 0.4 | V    |

| 4.11.2  | R <sub>INT_PU_OD</sub> | Internal pull-up resistor                |                                                                  | 7   |     | 15  | kΩ   |

| 4.11.3  | V <sub>OL_PP</sub>     | Low-level output voltage (push-pull)     | VIO = 1.8V, I <sub>OL</sub> = 2mA                                |     |     | 0.4 | V    |

| 4.11.4  | V <sub>OH_PP</sub>     | High-level output voltage (push-pull)    | VIO = 1.8V, I <sub>OH</sub> = 2mA                                | 0.8 |     |     | V    |

| 4.11.5  | I <sub>LKG</sub>       | Input leakage current                    | VIO = 3.6V                                                       |     |     | 1   | μA   |

| TIMING  | CHARACTER              | ISTICS                                   |                                                                  |     |     |     |      |

| 4.11.11 | t <sub>R_PP</sub>      | Output Voltage Rise Time (push-<br>pull) | VIO = 1.8, C <sub>LOAD</sub> = 10pF, Measured<br>from 10% to 90% |     |     | 5   | ns   |

| 4.11.12 | t <sub>F_PP</sub>      | Output Voltage Fall Time (push-pull)     | VIO = 1.8, $C_{LOAD}$ = 10pF, Measured from 90% to 10%           |     |     | 10  | ns   |

# 6.12 nRSTOUT

| POS    |                            | PARAMETER                             | TEST CONDITIONS                   | MIN | TYP M | X   | UNIT |  |

|--------|----------------------------|---------------------------------------|-----------------------------------|-----|-------|-----|------|--|

| ELECTE | ELECTRICAL CHARACTERISTICS |                                       |                                   |     |       |     |      |  |

| 4.12.1 | V <sub>OL_OD</sub>         | Low-level output voltage (open drain) | VIO = 3.6V, I <sub>OL</sub> = 2mA |     | (     | ).4 | V    |  |

| 4.12.2 | R <sub>INT_PU_OD</sub>     | Internal pull-up resistor             |                                   | 7   |       | 15  | kΩ   |  |

| 4.12.3 | V <sub>OL_PP</sub>         | Low-level output voltage (push pull)  | VIO = 3.6V, I <sub>OL</sub> = 2mA |     | (     | ).4 | V    |  |

SLVSG12A - NOVEMBER 2021 - REVISED SEPTEMBER 2022

# 6.12 nRSTOUT (continued)

Over operating free-air temperature range (unless otherwise noted)

| POS     |                                    | PARAMETER                                      | TEST CONDITIONS                                                   | MIN         | TYP | MAX | UNIT |

|---------|------------------------------------|------------------------------------------------|-------------------------------------------------------------------|-------------|-----|-----|------|

| 4.12.4  | V <sub>OH_PP</sub>                 | High-level output voltage (push pull)          | VIO = 3.6V, I <sub>OL</sub> = 2mA                                 | 0.8<br>*VIO |     |     | V    |

| 4.12.5  | V <sub>OL_PP</sub>                 | Low-level output voltage (push pull)           | VIO = 1.8V, I <sub>OL</sub> = 2mA                                 |             |     | 0.4 | V    |

| 4.12.6  | V <sub>OH_PP</sub>                 | High-level output voltage (push pull)          | VIO = 1.8V, I <sub>OL</sub> = 2mA                                 | 0.7*VIO     |     |     | V    |

| 4.12.7  | I <sub>LKG</sub>                   | Input leakage current                          | VIO = 3.6V                                                        |             |     | 1   | μA   |

| TIMINIG | CHARACTER                          | RISTICS                                        |                                                                   |             |     | ·   |      |

| 4.12.10 | t <sub>R_PP</sub>                  | Output voltage rise time                       | VIO = 1.8V, C <sub>LOAD</sub> = 10pF,<br>Measured from 10% to 90% |             |     | 5   | ns   |

| 4.12.11 | t <sub>F_PP</sub>                  | Output voltage fall time                       | VIO = 1.8V, C <sub>LOAD</sub> = 10pF,<br>Measured from 90% to 10% |             |     | 5   | ns   |

| 4.12.12 | t <sub>DEGLITCH_RE</sub><br>ADBACK | Deglitch time on both rising and falling edges |                                                                   | 8           | 10  | 12  | μs   |

# 6.13 GPIO

Over operating free-air temperature range (unless otherwise noted)

| POS     |                  | PARAMETER                                                 | TEST CONDITIONS                                                  | MIN  | TYP | MAX  | UNIT |

|---------|------------------|-----------------------------------------------------------|------------------------------------------------------------------|------|-----|------|------|

| ELECTF  | RICAL CHARA      | ACTERISTICS                                               |                                                                  |      |     | I    |      |

| 4.13.1  | VIL              | Low-level input voltage                                   |                                                                  |      |     | 0.54 | V    |

| 4.13.2  | V <sub>IH</sub>  | High-level input voltage                                  |                                                                  | 1.26 |     |      | V    |

| 4.13.3  | I <sub>LKG</sub> | Input leakage current                                     |                                                                  | ·    |     | 1    | μA   |

| 4.13.4  | C <sub>IN</sub>  | Internal input pin capacitance                            |                                                                  | ÷    |     | 10   | pF   |

| 4.13.5  | V <sub>OL</sub>  | Low-level output voltage                                  | VIO = 3.6V, I <sub>OL</sub> = 2mA                                |      |     | 0.4  | V    |

| 4.13.6  | V <sub>OH</sub>  | High-level output voltage                                 | VIO = 3.6V, I <sub>OH</sub> = 2mA                                | 0.8  |     |      | V    |

| 4.13.8  | R <sub>PD</sub>  | Internal pull-down resistance when configured as an input | VIO = 1.8V or 3.3V                                               | 100  | 400 |      | ΚΩ   |

| TIMING  | CHARACTER        | RISTICS                                                   |                                                                  |      |     |      |      |

| 4.13.11 | t <sub>R</sub>   | Output Voltage Rise Time                                  | VIO = 1.8, C <sub>LOAD</sub> = 10pF, Measured<br>from 10% to 90% |      |     | 5    | ns   |

| 4.13.12 | t <sub>F</sub>   | Output Voltage Fall Time                                  | VIO = 1.8, C <sub>LOAD</sub> = 10pF, Measured<br>from 90% to 10% |      |     | 5    | ns   |

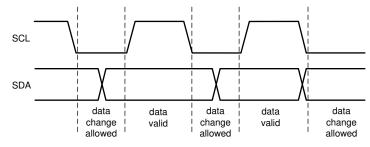

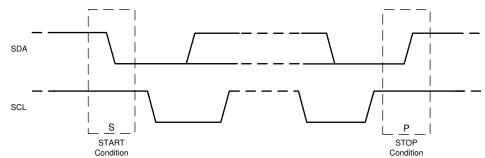

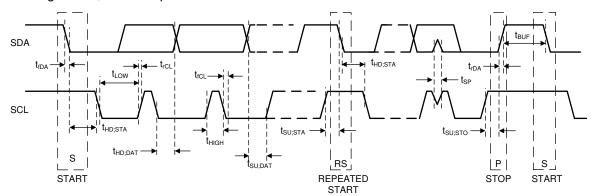

# 6.14 I<sup>2</sup>C Interface

| POS     |                      | PARAMETER                       | TEST CONDITIONS                                                 | MIN  | TYP  | MAX | UNIT |

|---------|----------------------|---------------------------------|-----------------------------------------------------------------|------|------|-----|------|

| ELECTR  | RICAL CHARA          | ACTERISTICS                     |                                                                 |      |      |     |      |

| 4.14.1  | V <sub>IL_I2C</sub>  | Input Low Voltage Threshold     |                                                                 |      |      | 0.4 | V    |

| 4.14.2  | V <sub>IH_I2C</sub>  | Input High Voltage Threshold    |                                                                 | 1.26 |      |     | V    |

| 4.14.3  | V <sub>OL_I2C</sub>  | DATA output low voltage         | V <sub>PULL_UP</sub> = 1.8V and 3.3V                            |      |      | 0.4 | V    |

| 4.14.4  | I <sub>LKG_I2C</sub> | Leakage Current                 | V <sub>PULL_UP</sub> = 1.8V and 3.3V                            |      | 0.01 | 0.3 | μA   |

| 4.14.9  | CI                   | Capacitance for each I/O pin    | Standard Mode, Fast Mode, Fast<br>Mode Plus and High-Speed Mode |      |      | 10  | pF   |

| 4.14.10 | C <sub>B</sub>       | Load capacitance on SDA and SCL | Standard Mode and Fast Mode                                     |      |      | 400 | pF   |

| 4.14.11 | C <sub>B</sub>       | Load capacitance on SDA and SCL | Fast Mode Plus                                                  |      |      | 550 | pF   |

| 4.14.12 | C <sub>B</sub>       | Load capacitance on SDA and SCL | High Speed Mode (3.4MHz)                                        |      |      | 100 | pF   |

# 6.15 Monitor Ref Sys

Over operating free-air temperature range (unless otherwise noted)

| POS    |                              | PARAMETER                                           | TEST CONDITIONS | MIN   | TYP | MAX | UNIT |

|--------|------------------------------|-----------------------------------------------------|-----------------|-------|-----|-----|------|

| ELECTR | RICAL CHARA                  | CTERISTICS                                          |                 |       |     |     |      |

| 4.15.1 | VSYS <sub>UVLO_R</sub>       | Internal under-voltage lockout threshold            | VSYS rising     | 3.5   |     | 3.9 | V    |

| 4.15.2 | VSYS <sub>UVLO_H</sub><br>YS | Internal under-voltage lockout threshold hysteresis | VSYS falling    | 100   | 150 | 200 | mV   |

| 4.15.3 | VSYS <sub>OVP</sub>          | Supply over-voltage protection threshold            | VSYS rising     | 18.5  |     |     | V    |

| 4.15.4 | VSYS <sub>OVP_H</sub><br>ys  | Supply over-voltage protection threshold hysteresis | VSYS falling    | 0.925 | 1.0 | 1.2 | V    |

## 6.16 Monitor BUCK1

| POS     |                         | PARAMETER                                                                                                                        | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT |

|---------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|------|------|

| ELECTE  | RICAL CHARA             | ACTERISTICS                                                                                                                      |                                                                  |      |      |      |      |

| 4.16.1  |                         |                                                                                                                                  |                                                                  | -5   | -4   | -3   |      |

| 4.16.2  | VBUCK1_U                | MV BUCK1 under-voltage detection                                                                                                 | VBUCK1 falling, Slew Rate =                                      | -5.5 | -4.5 | -3.5 | %    |

| 4.16.3  | V                       | threshold expressed in percentage of target regulation voltage                                                                   | 50mV/ms                                                          | -6   | -5   | -4   | 70   |

| 4.16.4  |                         |                                                                                                                                  |                                                                  | -6.5 | -5.5 | -4.5 |      |

| 4.16.5  | VBUCK1_U<br>V_HYS       | MV BUCK1 under-voltage detection<br>threshold hysteresis expressed in<br>percentage of absolute value of<br>VBUCK1_UV            | VBUCK1 rising, Slew Rate =<br>50mV/ms                            |      | 1.05 |      | %    |

| 4.16.6  |                         |                                                                                                                                  |                                                                  | 3    | 4    | 5    |      |

| 4.16.7  | VBUCK1 O                | MV BUCK1 over-voltage detection                                                                                                  | VBUCK1 rising, Slew Rate =                                       | 3.5  | 4.5  | 5.5  | %    |

| 4.16.8  | _v                      | threshold expressed in percentage of target regulation voltage                                                                   | 50mV/ms                                                          | 4    | 5    | 6    | 70   |

| 4.16.9  |                         |                                                                                                                                  |                                                                  | 4.5  | 5.5  | 6.5  |      |

| 4.16.10 | VBUCK1_O<br>V_HYS       | MV BUCK1 over-voltage detection<br>threshold hysteresis expressed in<br>percentage of absolute value of<br>VBUCK1_OV             | VBUCK1 falling, Slew Rate =<br>50mV/ms                           |      | 0.95 |      | %    |

| 4.16.11 | VBUCK1_O<br>VP          | MV BUCK1 over-voltage protection<br>detection threshold expressed in<br>percentage of target regulation<br>voltage               | VBUCK1 rising, Slew Rate = 50mV/ms                               | 9    | 12   | 15   | %    |

| 4.16.12 | VBUCK1_O<br>VP_HYS      | MV BUCK1 over-voltage protection<br>detection threshold hysteresis<br>expressed in percentage of<br>absolute value of VBUCK1_OVP | VBUCK1 falling, Slew Rate =<br>50mV/ms                           |      | 0.9  |      | %    |

| 4.16.13 | VBUCK1_S<br>CG          | MV BUCK1 short-circuit detection threshold                                                                                       | VBUCK1 falling, Slew Rate = 50mV/ms                              | 250  | 300  | 350  | mV   |

| 4.16.14 | VBUCK1_S<br>CG_HYS      | MV BUCK1 short-circuit detection threshold hysteresis                                                                            | VBUCK1 rising, Slew Rate = 50mV/ms                               |      | 100  |      | mV   |

| TIMING  | CHARACTER               | RISTICS                                                                                                                          |                                                                  |      |      |      |      |

| 4.16.20 | t <sub>BUCK1_VMON</sub> | MV BUCK1 output voltage fault detection deglitch time                                                                            | Measured from UV/OV/OVP event to respective status bit being set | 20   |      | 24   | μs   |

## 6.17 Monitor BUCK2

Over operating free-air temperature range (unless otherwise noted)

| POS     |                                 | PARAMETER                                                                                                                        | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT |

|---------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|------|------|

| ELECTR  |                                 | ACTERISTICS                                                                                                                      |                                                                  |      |      |      |      |

| 4.17.1  |                                 |                                                                                                                                  |                                                                  | -5   | -4   | -3   |      |

| 4.17.2  | VBUCK2 U                        | LV BUCK2 under-voltage detection                                                                                                 | VBUCK2 falling, Slew Rate =                                      | -5.5 | -4.5 | -3.5 | %    |

| 4.17.3  | V                               | threshold expressed in percentage of target regulation voltage                                                                   | 50mV/ms                                                          | -6   | -5   | -4   | 70   |

| 4.17.4  |                                 |                                                                                                                                  |                                                                  | -6.5 | -5.5 | -4.5 |      |

| 4.17.5  | VBUCK2_U<br>V_HYS               | LV BUCK2 under-voltage detection<br>threshold hysteresis expressed in<br>percentage of absolute value of<br>VBUCK2_UV            | VBUCK2 rising, Slew Rate =<br>50mV/ms                            |      | 1.05 |      | %    |

| 4.17.6  |                                 |                                                                                                                                  |                                                                  | 3    | 4    | 5    |      |

| 4.17.7  | VBUCK2_O                        | LV BUCK2 over-voltage detection threshold expressed in percentage                                                                | VBUCK2 rising, Slew Rate =                                       | 3.5  | 4.5  | 5.5  | %    |

| 4.17.8  | V                               | of target regulation voltage                                                                                                     | 50mV/ms                                                          | 4    | 5    | 6    | 70   |

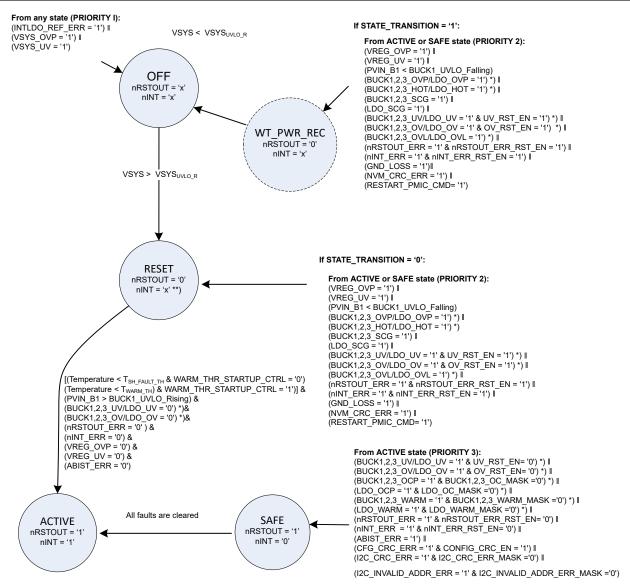

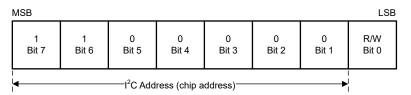

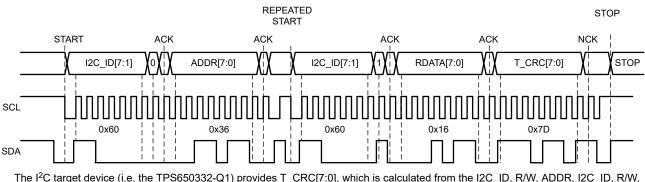

| 4.17.9  |                                 |                                                                                                                                  |                                                                  | 4.5  | 5.5  | 6.5  |      |