Application Report

SLAA750-July 2017

# DAC38RF8x Test Modes

Kyle Addington

#### Wireless Infrastructure

### ABSTRACT

The DAC38RF8x family of devices comes equipped with multiple test modes to assist users in verifying systems in rapid prototyping situations. This application report covers two of the available tests, the pseudorandom binary-sequence test and JESD204B short pattern test, in detail using the TI DAC38RF8xEVM and TSW14J56EVM capture card.

Contents

| 1 | Introd | Juction to PRBS Test                           |

|---|--------|------------------------------------------------|

|   | 1.1    | Required Hardware 2                            |

|   | 1.2    | Required Software 2                            |

|   | 1.3    | Hardware Setup 3                               |

|   | 1.4    | Configuring the DAC38RF8x 4                    |

|   | 1.5    | PRBS Register Writes for Custom Setup          |

|   | 1.6    | TSW14J56 SETUP for PRBS Tests                  |

|   | 1.7    | PRBS Test Results                              |

| 2 | Introd | Juction to JESD204B Short Pattern Test         |

|   | 2.1    | Required Hardware                              |

|   | 2.2    | Required Software                              |

|   | 2.3    | Hardware Setup                                 |

|   | 2.4    | Configuring the DAC38RF8x 10                   |

|   | 2.5    | Register Writes for Custom Setup 11            |

|   | 2.6    | TSW14J56 SETUP for JESD204B Short Pattern Test |

|   | 2.7    | Short Pattern Test Procedure                   |

|   | 2.8    | JESD204B Short Pattern Test Results 15         |

#### List of Figures

| 1  | PRBS Hardware Setup                                  | 3  |

|----|------------------------------------------------------|----|

| 2  | DAC38RF8x EVM GUI Quick Start Tab                    | 4  |

| 3  | DAC38RF8x EVM GUI Clocking Tab                       | 5  |

| 4  | DAC38RF8x EVM GUI Alarm Monitoring Tab               | 5  |

| 5  | DAC38RF8x EVM GUI SERDES and Lane Configuration Tab  | 6  |

| 6  | DAC38RF8x EVM GUI JESD Block Tab                     | 6  |

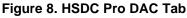

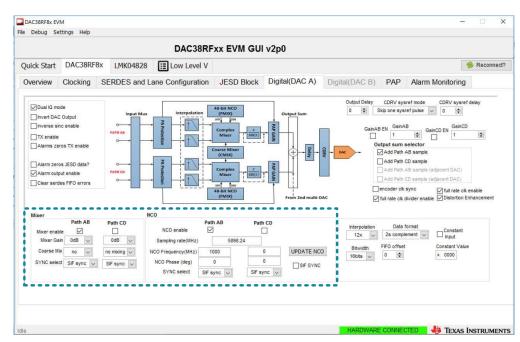

| 7  | HSDC Pro Select-Board Menu                           | 7  |

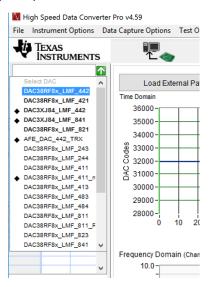

| 8  | HSDC Pro DAC Tab                                     | 7  |

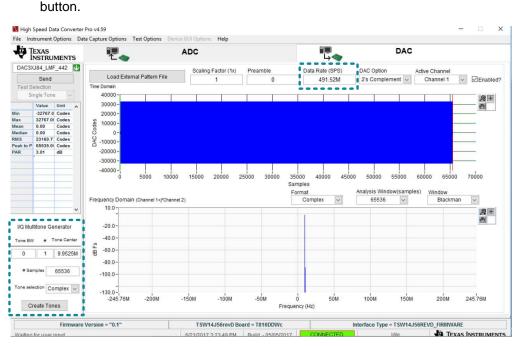

| 9  | PRBS Testing .ini File Selection                     |    |

| 10 | SERDES Test Options Menu                             | 8  |

| 11 | DAC38RF8x GUI (4421 External Clocking Configuration) | 10 |

| 12 | DAC38RF8xEVM GUI Digital (DAC A) Tab                 |    |

| 13 | HSDC Pro Select Board Menu                           | 12 |

| 14 | HSDC Pro DAC Tab                                     | 12 |

| 15 | HSDC Pro Select .ini File Menu                       |    |

| 16 | HSDC Pro Tone Creation                               | 13 |

|    |                                                      |    |

#### Introduction to PRBS Test

| 17 | Example Short Test Pattern File                                 | 14 |

|----|-----------------------------------------------------------------|----|

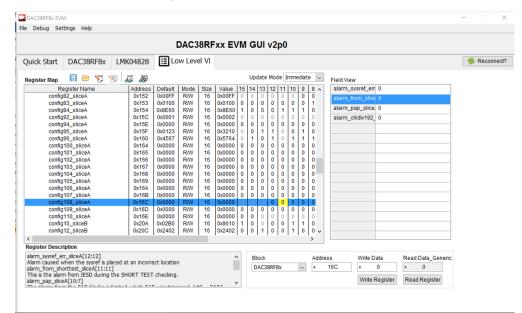

| 18 | DAC38RF8x EVM GUI Low Level View Tab Short Test Enable Register | 14 |

| 19 | DAC38RF8x EVM GUI Low Level View Tab Short Test Alarm Register  | 15 |

### Trademarks

All trademarks are the property of their respective owners.

## 1 Introduction to PRBS Test

A pseudorandom binary sequence (PRBS) is a stream of binary information often used in testing highspeed data-transmission signal integrity. Pseudorandom binary sequences are composed of an equal distribution of 0s and 1s and only repeat themselves after 2<sup>k - 1</sup> cycles, where k is the order of the PRBS test. The PRBS test replicates the worst-case data scenarios where the current received bit is unrelated to previous bits. For more information on pseudorandom binary sequences, refer to the Advantest document, *DSP-Based Testing - Fundamentals 50, PRBS (Pseudo Random Binary Sequence)* (Okawara 2013).

The DAC38RF8x supports three different PRBS testing options: PRBS7, PRBS23, and PRBS 31. In this test mode, the PRBS pattern is supplied to the DAC input, typically through an FPGA, and the pattern is compared with the internally generated pattern of the DAC. If the received pattern matches the generated pattern, the test will pass and confirm good signal integrity at the DAC input. Otherwise a flag in one of the DAC registers is set to notify the user of a possible issue.

The following sections outline the required steps to implement the PRBS test using the DAC38RF8x EVM by using the TSW14J56 capture card and corresponding TI GUI software. To run the test without using the TI EVMs and GUIs, configure the DAC to the desired operating state and perform the register writes provided in Section 1.5 to enable the PRBS test mode.

### 1.1 Required Hardware

This test procedure requires the following lab equipment:

- DAC38RF8xEVM RevE board

- TSW14J56 RevD board

- 5-V DC power supplies

- Signal generator

- Oscilloscope

# 1.2 Required Software

This test procedure requires the following software:

- HSDC Pro Version 4.8 or higher

- DAC38RF8x EVM GUI

# 1.3 Hardware Setup

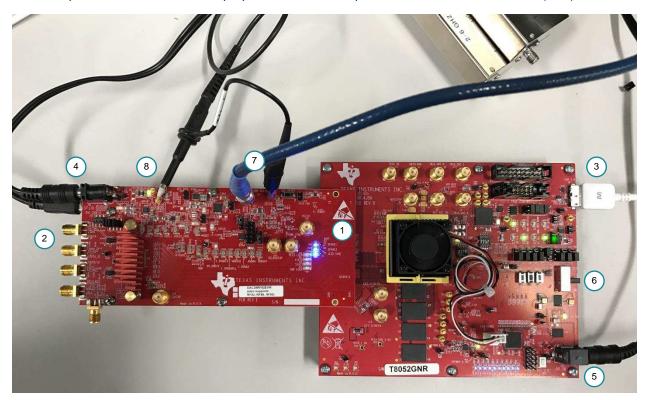

Follow these steps (see Figure 1) to set up the hardware:

- Step 1. Connect the TSW14J56 FMC interface connector (J4 of TSW14J56) to DAC38RF8x FMC interface connector (J20 of DAC38RF8x EVM).

- Step 2. Connect a USB 2.0 Type A to Mini-B cable from the PC to DAC38RF8x EVM USB Mini-B port (J16).

- Step 3. Connect a USB 3.0 Type A to Type B cable from the PC to TSW14J56 RevD USB 3.0 B port (J9).

- Step 4. Connect a 5-V power supply to the DAC38RF8x EVM board using J21.

- Step 5. Connect a 5-V power supply to the TSW14J56 board using J11.

- Step 6. Turn on the TSW14J56 board by moving switch 6 to the ON position.

- Step 7. Connect the signal-generator output to LMKCLKIN (J4) of the DAC38RF8x EVM board.

- Configure the signal generator to output a frequency of 368.64 MHz with an amplitude of 10 dBm.

- Ensure that JP10 is removed from the board to enable internal clocking.

Step 8. Attach an oscilloscope probe to the alarm pin of DAC38RF8x EVM board (TP9).

Figure 1. PRBS Hardware Setup

3

Introduction to PRBS Test

## 1.4 Configuring the DAC38RF8x

This procedure describes how to configure the DAC into the LMF = 841 mode with internal clocking. If a different configuration is needed, follow a similar procedure and simply vary the values in step 3 and step 4.

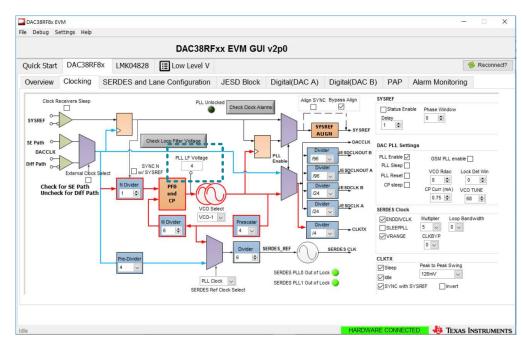

- Step 1. Launch the DAC38RF8x EVM GUI and select the Quick Start tab (see Figure 2).

- Step 2. Reset the board by clicking the *Not in RESET* button and then clicking the button again, after the button changes, to bring the board back out of reset. Click the *LOAD DEFAULT* button to load the default values into the registers.

- Step 3. Under the DAC MODE section, set

- The # of DACs field to Dual DAC

- The # of IQ pairs per DAC to 1 IQ pair

- The # of SerDes lanes per DAC field to 4 lanes

- The Desired Interpolation field to 12x

- Step 4. In the On-Chip PLL section check the PLL Enable box. Set the *M* field to 6, the *N* field to 1, and the multiplier to 368.64. The DAC Clock Frequency box should automatically change to 8847.36 MHz. Click the CONFIGURE DAC button. After this configuration is complete, click the PLL AUTO TUNE button. After this configuration is complete, click the Reset DAC JESD Core & SYSREF TRIGGER button.

| AC38RF8x EVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - 🗆 ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Debug Settings Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DAC38RFxx EVM GUI v2p0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Quick Start DAC38RF8x LMK04828 ELow Level V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 🗇 Reconnect?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Die Temp (Celcius) DAC38RF82 SELECT DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Update DAC RESETB Pin Quick Start Procedure -Reset the DAC. Toggle the RESET -LOAD DEFAULT -Load Default Register Settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DAC Clock Frequency (IMHz)       # of DACs       # of Dapring per DAC       # of series lanes per DAC       Desired Interpolation         B847.36       Dual DAC       # of IQ pairs per DAC       # of series lanes per DAC       Desired Interpolation       CONFIGURE DAC         On-chip PLL       Vald PLL Frequency       Vald PLL Frequency       Current Series Lane Rate =7372.80MHz       CONFIGURE DAC       PLL AUTO TUNE         M       6       94       x388.64       X388.64       PLL AUTO TUNE       PLL AUTO TUNE         SMA, 44 CLK       \$88.64       Serdes PLL Multipler = 5       HSDCPRO Ini File: DAC38RF8x_LMF_B41       PLL AUTO TUNE | -For External clock mode, enter the<br>external clock frequency and<br>select the desired no. of DACs,<br>no. of IQ pars, no. of serdes lanes<br>and the interpolation.<br>-Clck on CONFIGURE DAC button<br>to configure the DAC for the mode<br>selected<br>-For onchip PLL mode, check the<br>PLL Enable box and specify the<br>Reference frequency, M and N<br>divider values.<br>-Select the desired mode of the DAC<br>button.<br>-Clck on the PLL AUTO TUNE<br>button to automatically set the PLL<br>bloop filter voltage |

| Reset DAC -Reset the DAC JESD Core and JESD Core & SYSREF TRIGGER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | trigger sysref                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Idle HARDWARE CONNECTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | d 🕹 Texas Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Figure 2. DAC38RF8x EVM GUI Quick Start Tab

Step 5. Select the *DAC38RF8x* tab and navigate to the *Clocking* sub-tab (see Figure 3). The box labeled *PLL LF Voltage* should be populated with a value from 2 to 6. If this value is correct, the configuration and PLL tuning were performed correctly. Otherwise, verify that the contents of the *Quick Start* tab are correct and repeat the previous steps.

Figure 3. DAC38RF8x EVM GUI Clocking Tab

Step 6. Select the Alarm Monitoring sub-tab (see Figure 4). In the General Alarm and Test section, select Alarm Output in the ALARM Pin drop-down menu. Select the ALARM Pin Polarity field to be either Active High or Active Low. Active high causes the alarm pin voltage to be set high if a PRBS error occurs.

|                                  |                |                                                                                                                                                                                               | DAC38RF                                                                                                                                                                                                       | xx EVM GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | v2p0                                                                                             |                           |     |                 |   |          |

|----------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|-----|-----------------|---|----------|

| uick Start                       | DAC38RF8x      | LMK04828                                                                                                                                                                                      | E Low Level V                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                  |                           |     |                 | * | Reconnec |

| Overview                         | Clocking SI    | ERDES and L                                                                                                                                                                                   | ane Configuration                                                                                                                                                                                             | JESD Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Digital(DAC A                                                                                    | ) Digital(DAC B)          | PAP | Alarm Monitorin | g |          |

| General Ala                      | rm and Test    | Alarm Masking                                                                                                                                                                                 |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                  | Clear All Errors and Read |     | Read Errors     |   |          |

| Alarm Z                          | eros JESD Data |                                                                                                                                                                                               | Sysref Phase                                                                                                                                                                                                  | Lane Number<br>0 1 2 3 4 5 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                  | m and Error Report        | _   |                 |   |          |

| Alarm Ou<br>ALARM I<br>Active Hi | Pin Polarity   | PLL Out of Lot<br>RW0 Out of Lot<br>DAC A Alarm M<br>Lane Alarms<br>FFO Alarms<br>EO ZERO<br>DAC B Alarm<br>DAC B Alarm<br>FFO Alarms<br>FFO Alarms<br>E B Alarms<br>FFO Alarms<br>FFO Alarms | x g<br>lane Number<br>1 2 3 4 5 6 7<br>1 2 3 4 5 6 7<br>1 2 10 20 22 36 40 45<br>1 2 10 12 20 32 36 40 45<br>1 2 10 12 20 32 36 40 45<br>1 2 3 2 3 4 5 6 7<br>1 2 3 4 5 6 7<br>1 2 3 4 5 6 7<br>1 2 3 4 5 6 7 | Align to Rt         Align           ort Test Error         Y           'SREF error         Y           'der         64           'D         Y           'D         Y           oft Test Error         Y           oft Test Error         Y           oft Test Error         Y           oft Test Error         Y           'SREF error | 4 160 192<br>4 160 192<br>2 2<br>4 160 192<br>5 2<br>5 2<br>5 2<br>5 2<br>5 2<br>5 2<br>5 2<br>5 |                           |     | ~               |   |          |

Figure 4. DAC38RF8x EVM GUI Alarm Monitoring Tab

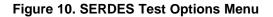

Step 7. Select the SERDES and Lane Configuration sub-tab (see Figure 5). In the Align drop-down menu select Disabled. Next, in the SERDES Test Pattern drop-down menu select the desired PRBS test. In the DTEST drop-down menu select TESTFAIL. In the DTEST Lane Select drop-down menu, select the lane to be tested.

|                      |            |                                                 | DAC38RF                                                                                                                                                                                                                                                                                                                                       | xx EVM GUI                             | v2p0                                                                 |                |                                                                                 |                          |              |

|----------------------|------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------|--------------------------|--------------|

| Quick Start          | DAC38RF8x  | LMK04828                                        | E Low Level V                                                                                                                                                                                                                                                                                                                                 |                                        |                                                                      |                |                                                                                 |                          | % Reconnect? |

| Overview             | Clocking S | ERDES and L                                     | ane Configuration                                                                                                                                                                                                                                                                                                                             | JESD Block                             | Digital(DAC A)                                                       | Digital(DAC B) | PAP                                                                             | Alarm Monitoring         |              |

| SERDES Configuration |            | None SLICEO                                     | CCE (PNN)  GP00 SVNCB Vcm 12 V V GP01 SVNCB Sleep SVNCB SLICE0 Lane Configuration SKRDES Lanes JESD Lane                                                                                                                                                                                                                                      |                                        | - 0                                                                  |                |                                                                                 | SLICE 1<br>JESO<br>BLOCK |              |

| 7-bit PRBS           | e Testing  | Invert?  RX0  RX1  RX2  RX3  RX4  RX5  RX6  RX7 | EN         Lane D         Which RX7           I         0         y         3           I         1         2           I         1         2           I         1         2           I         1         2           S         0         5           I         5         7           I         6         6           I         7         4 | 0 ×<br>1 ×<br>2 ×<br>3 ×<br>4 ×<br>5 × | heh R/?<br>5 v 0<br>7 v 0<br>6 v 0<br>3 v 0<br>2 v 0<br>1 v 0<br>0 v |                | Sampler,<br>Descrializer,<br>Musing<br>and<br>FIFOs<br>SLICE 0<br>JESO<br>BLOCK |                          |              |

Step 8. Select the *JESD Block* sub-tab (see Figure 6). Ensure that the *Comma Align EN* boxes are not checked.

|                                                                                                                                                                                                                   |                                                 |                | DAC38RF                  | XX EVM GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | v2p0                |                                                                                                                                                                                |                                   |             |                  |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|------------------|-----------|

| uick Start                                                                                                                                                                                                        | DAC38RF8x                                       | LMK04828       | E Low Level V            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |                                                                                                                                                                                |                                   |             |                  | 👶 Reconne |

| Overview                                                                                                                                                                                                          | Clocking SE                                     | ERDES and L    | ane Configuration        | JESD Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Digital(DAC A       | ) Digita                                                                                                                                                                       | al(DAC B)                         | PAP         | Alarm Monitoring |           |

| AC A                                                                                                                                                                                                              |                                                 |                |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |                                                                                                                                                                                |                                   |             |                  |           |

| Link Config                                                                                                                                                                                                       | uration                                         |                |                          | Elastic Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | E                   | Frors for SYN                                                                                                                                                                  | IC Request and                    | Reporting   |                  |           |

| L                                                                                                                                                                                                                 | M F K                                           | S DID          | BID ADJONT PHADJ         | RBD should be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | latch Char.         | SR                                                                                                                                                                             | S = Enable S'<br>R = Enable Er    |             | Thuse mode       |           |

| 3                                                                                                                                                                                                                 | 1 0 19                                          | 0 0            | 0 0 0                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ar. to Match        |                                                                                                                                                                                | R = Enable Er<br>ame alignment er |             | 8 phases         | ~         |

|                                                                                                                                                                                                                   | N' JESDV<br>15 JESD204B                         | ADJDIR         | CS CF Lane Skew<br>0 0 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | atch what?          | Frame alignment error     Link configuration error     Elastic buffer over flow     Elastic buffer over flow     Code synchronization error     Solv Do nch-n-table code error |                                   | Init SLICE0 |                  |           |

|                                                                                                                                                                                                                   |                                                 | - hereit i i i | v is SYSREF used?        | 19 CC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NTROL 🗸             |                                                                                                                                                                                |                                   | OFF         | ~                |           |

| Subclass 1         0         0         Use only the next pulse         v           SCR         HD                                                                                                               < |                                                 |                |                          | FIFO errors zeros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.4.4               | Code synchronization error                                                                                                                                                     |                                   |             | Permett          |           |

|                                                                                                                                                                                                                   |                                                 |                |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     | 8b/10b not-in-table code error<br>8b/10b disparity error                                                                                                                       |                                   |             |                  |           |

| SCRAME                                                                                                                                                                                                            | BLE OFF V ON                                    | $\sim$         |                          | TX Does not allow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Comma Align EN      |                                                                                                                                                                                |                                   |             |                  |           |

| AC B                                                                                                                                                                                                              |                                                 |                |                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                                                                                                                                                                                |                                   |             |                  |           |

| Link Config                                                                                                                                                                                                       | uration                                         |                |                          | Elastic Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | Frrors for SY                                                                                                                                                                  | NC Request and                    | d Reporting | Phase mode       |           |

| L                                                                                                                                                                                                                 | M F K                                           | S DID          | BID ADJCNT PHADJ         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Match Char.         | S =                                                                                                                                                                            | Enable SYNC Re                    | quest       | 8 phases         | 1         |

| 3                                                                                                                                                                                                                 | 1 0 19                                          | 0 0            | 0 0 0                    | less than or C<br>equal to K.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | har. to Match       |                                                                                                                                                                                | Enable Error Rep                  |             |                  | -         |