# SN9226 Single-Ended to Differential 2.3 - 2.9 GHz RF Amplifier with Integrated Balun

### 1 Features

- Single channel, single ended 50  $\Omega$  input to differential 50/100  $\Omega$  output RF gain block amplifier

- SN9226 supports 2.6 GHz center frequency with 400 MHz 1-dB BW

- 16.5 dB (or 16.8 dB) typical gain when driving differential matched Z<sub>LOAD</sub> = 50 Ω (or 100 Ω)

- 3 dB Noise figure in 1-dB bandwidth

- 33 dBm OIP3 at P<sub>OUT/TONE</sub> = 2 dBm

- 18-dBm output P1dB

- 275 mW Power consumption on +3.3-V single supply

- Up to  $T_A = 105^{\circ}C$  operating temperature

## 2 Applications

- 5G m-MIMO TDD systems

- Small cell base stations

- Low-cost radios

- Cellular base station

- Single-ended to differential conversions

- Balun alternatives

- RF gain blocks

- Differential driver for high GSPS ADCs

## **3 Description**

The SN9226 is high performance, single channel, single ended 50  $\Omega$  input to differential 50  $\Omega$  or 100  $\Omega$  output RF gain block amplifier supporting 2.6 GHz center frequency band with 400 MHz 1-dB Bandwidth (BW). The device is well suited to support requirements for the next generation 5G m-MIMO or Small Cell base station applications, where it is used as the last stage to drive the full-scale differential input of an analog front-end (AFE) or ADC.

The device provides 16.5 dB (or 16.8 dB) typical gain with good linearity performance of +33 dBm Output IP3 when driving a differential 50  $\Omega$  (or 100  $\Omega$ ) matched output at 2.6 GHz. Noise figure of less than 3 dB is maintained across the whole 1dB Bandwidth. The device is internally matched for 50- $\Omega$  impedance at the single-ended input. The differential output easily interfaces to a TI transceiver - SN1710796 without any external matching circuitry. The differential output can interface to 100  $\Omega$  impedance with (or without) external matching circuitry at 2.6 GHz, providing approximately 0.5 dB gain increase (or decrease) compared to the 50  $\Omega$  output impedance scenario at 2.6 GHz.

Operating on a single 3.3 V supply, the device consumes about 275 mW of stand-by power making it suitable for high-density 5G massive MIMO applications. Also, the device is available in a space saving 2mm x 2mm, 12-pin WQFN package. The device is rated for an operating temperature of up to  $T_A = 105^{\circ}$ C providing a robust system design. There is a 1.8-V JEDEC compliant power down pin available for fast power down and power up of the device suitable for time division duplex (TDD) systems.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| SN9226      | WQFN (12) | 2.00 mm × 2.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### SN9226: 2.3 to 2.9 GHz Single Ended Input to Differential Output RF Gain Block Amplifier

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCT PREVIEW Information. Product in design phase of development. Subject to change or discontinuance without notice.

Texas Instruments

#### www.ti.com

# **Table of Contents**

| 1 | Feat           | tures                            | 1              |  |  |

|---|----------------|----------------------------------|----------------|--|--|

| 2 | Applications 1 |                                  |                |  |  |

| 3 | Des            | cription                         | 1              |  |  |

| 4 | Rev            | ision History                    | 2              |  |  |

| 5 | Pin            | Configuration and Functions      | 3              |  |  |

| 6 | Spe            | cifications                      | 3              |  |  |

|   | 6.1            |                                  |                |  |  |

|   | 6.2            | ESD Ratings                      | 4              |  |  |

|   | 6.3            | Recommended Operating Conditions |                |  |  |

|   | 6.4            | Thermal Information              | 4              |  |  |

|   | 6.5            | Electrical Characteristics       | 4              |  |  |

| 7 | Deta           | ailed Description                | <mark>6</mark> |  |  |

|   | 7.1            | Overview                         | 6              |  |  |

|   | 7.2            | Functional Block Diagram         | 6              |  |  |

|   |                |                                  |                |  |  |

|    | 7.3  | Feature Description                             | . 6 |

|----|------|-------------------------------------------------|-----|

|    | 7.4  | Device Functional Modes                         | . 7 |

| 8  | Арр  | lication and Implementation                     | . 8 |

|    | 8.1  | Application Information                         | . 8 |

|    | 8.2  | Typical Application                             | . 8 |

| 9  | Pow  | er Supply Recommendations                       | 11  |

| 10 | Lay  | out                                             | 12  |

|    | 10.1 | Layout Guidelines                               | 12  |

|    | 10.2 | Layout Example                                  | 12  |

| 11 | Dev  | ice and Documentation Support                   | 13  |

|    | 11.1 | Receiving Notification of Documentation Updates | 13  |

|    | 11.2 | Trademarks                                      | 13  |

|    | 11.3 | Electrostatic Discharge Caution                 | 13  |

| 12 | Mec  | hanical, Packaging, and Orderable               |     |

|    | Info | rmation                                         | 14  |

|    |      |                                                 |     |

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE | REVISION | NOTES            |

|------|----------|------------------|

| TBD  | *        | Initial release. |

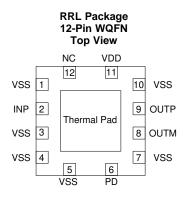

## 5 Pin Configuration and Functions

#### **Pin Functions**

|        | PIN I/O |        | DESCRIPTION                                                                          |  |

|--------|---------|--------|--------------------------------------------------------------------------------------|--|

| NO.    | NAME    | 1/0    | DESCRIPTION                                                                          |  |

| 1      | VSS     | Power  | Analog Ground                                                                        |  |

| 2      | INP     | Input  | RF single-ended input into amplifier                                                 |  |

| 3      | VSS     | Power  | Analog Ground                                                                        |  |

| 4      | VSS     | Power  | Analog Ground                                                                        |  |

| 5      | VSS     | Power  | Analog Ground                                                                        |  |

| 6      | PD      | Input  | Power down connection. PD = $0 V$ = normal operation; PD = $1.8 V$ = power off mode. |  |

| 7      | VSS     | Power  | Analog Ground                                                                        |  |

| 8      | OUTM    | Output | F single-ended output negative                                                       |  |

| 9      | OUTP    | Output | RF single-ended output positive                                                      |  |

| 10     | VSS     | Power  | Ground                                                                               |  |

| 11     | VDD     | Power  | Positive supply voltage (3.3 V)                                                      |  |

| 12     | NC      | _      | Do not connect this pin                                                              |  |

| Therma | al Pad  | —      | Connect the thermal pad to Ground                                                    |  |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                     |                                  | MIN  | MAX | UNIT |

|-------------------------------------|----------------------------------|------|-----|------|

| Supply voltage                      | VDD                              | -0.3 |     | V    |

| RF Pins                             | INP, OUTP, OUTM                  | -0.3 | VDD | V    |

| Digital Input PIN                   | PD                               | -0.3 | VDD | V    |

| Continuous<br>wave (CW)<br>overload | F <sub>in</sub> = 2.6 GHz at INP |      | 25  | dBm  |

| TJ                                  | Junction temperature             |      | 150 | °C   |

| T <sub>stg</sub>                    | Storage temperature              | -65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

STRUMENTS

EXAS

## 6.2 ESD Ratings

|                    |                         |                                                                                         | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|-------|------|

| M                  | Electrostatic discharge | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001, allpins <sup>(1)</sup>           | ±1000 | M    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. [Following sentence optional; see the wiki.] Manufacturing with less than 500-V HBM is possible with the necessary precautions. [Following sentence optional; see the wiki.] Pins listed as ±WWW V and/or ±XXX V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. [Following sentence optional; see the wiki.] Manufacturing with less than 250-V CDM is possible with the necessary precautions. [Following sentence optional; see the wiki.] Pins listed as ±YYY V and/or ±ZZZ V may actually have higher performance.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                      | MIN  | NOM | MAX  | UNIT |

|----------------|----------------------|------|-----|------|------|

| VDD            | Supply voltage       | 3.15 | 3.3 | 3.45 | V    |

| T <sub>A</sub> | Ambient temperature  | -40  |     | 105  | °C   |

| TJ             | Junction temperature | -40  |     | 125  | °C   |

### 6.4 Thermal Information

|                       |                                              | DEVICE            | UNIT |  |

|-----------------------|----------------------------------------------|-------------------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | PKG DES (PKG FAM) |      |  |

|                       |                                              | PINS              | -    |  |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 74.8              | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 72.4              | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 37.1              | °C/W |  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 3.2               | °C/W |  |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 37.1              | °C/W |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 14.2              | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$T_A = +25^{\circ}C$ , VDD = 3.3V, Center Frequency ( $F_{in}$ ) = 2.6 GHz, Single-Ended Input Impedance ( $Z_{IN}$ ) = 50  $\Omega$ , Differential Output Impedance ( $Z_{LOAD}$ ) = 50  $\Omega$  or 100  $\Omega$ ,  $P_{OUT(TOTAL)}$  = 8 dBm (unless otherwise noted)

|                              | PARAMETER                               | TEST CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNIT   |

|------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|------|------|------|--------|

| RF PER                       | FORMANCE - SN9226                       |                                                                                          |      |      |      |        |

| F <sub>RF</sub>              | RF frequency range                      |                                                                                          | 2200 |      | 2900 | MHz    |

| $\mathrm{BW}_{\mathrm{1dB}}$ | 1dB Bandwidth                           | Center Frequency $(F_{in}) = 2.6 \text{ GHz}$                                            |      | 400  |      | MHz    |

|                              |                                         | $F_{in}$ = 2.6 GHz, $Z_{LOAD}$ = 50 $\Omega$                                             |      | 16.5 |      | dB     |

| S21                          | Gain                                    | $F_{in}$ = 2.6 GHz, $Z_{LOAD}$ = 100 $\Omega$ unmatched                                  |      | 16   |      | dB     |

|                              |                                         | $F_{in}$ = 2.6 GHz, $Z_{LOAD}$ = 100 $\Omega$ matched                                    |      | 16.8 |      | dB     |

| NF                           | Noise Figure                            | $F_{in}$ = 2.6 GHz, $Z_{SOURCE}$ = 50 $\Omega$                                           |      | 3    |      | dB     |

| OIP1                         | Output P1dB                             | $F_{in}$ = 2.6 GHz, $Z_{LOAD}$ = 50 $\Omega$                                             |      | 18.2 |      | dBm    |

| OIP3                         | Output IP3                              | $F_{in} = 2.6 \text{ GHz} \pm 10 \text{ MHz}$ Spacing,<br>$P_{OUT/TONE} = 2 \text{ dBm}$ |      | 33   |      | dBm    |

|                              | Differential output Gain Imbalance (1)  |                                                                                          |      | ±0.5 |      | dB     |

|                              | Differential output Phase Imbalance (1) |                                                                                          |      | ±4   |      | degree |

| S11                          | Input return loss                       | $F_{in}$ = 2.6 GHz, BW = 400 MHz, $Z_{LOAD}$ = 50 or 100 $\Omega$                        |      | -9.2 |      | dB     |

(1) Measured at  $F_{in} {=}\ 2.6 GHz,$  over the  $BW_{1dB}$

### **Electrical Characteristics (continued)**

$T_{A} = +25^{\circ}C, VDD = 3.3V, Center Frequency (F_{in}) = 2.6 \text{ GHz}, Single-Ended Input Impedance (Z_{IN}) = 50 \Omega, Differential Output Impedance (Z_{LOAD}) = 50 \Omega \text{ or } 100 \Omega, P_{OUT(TOTAL)} = 8 \text{ dBm} (unless otherwise noted)$

|                     | PARAMETER                                  | TEST CONDITIONS                                                        | MIN | TYP  | MAX | UNIT |

|---------------------|--------------------------------------------|------------------------------------------------------------------------|-----|------|-----|------|

| Z <sub>IN</sub>     | Single Ended Input Reference<br>Impedance  |                                                                        |     | 50   |     | Ω    |

|                     |                                            | $F_{in}$ = 2.6 GHz, BW = 400 MHz, $Z_{LOAD}$ = 50 $\Omega$             |     | -9.5 |     | dB   |

| S22                 | Differential output return loss            | $F_{in}$ = 2.6 GHz, BW = 400 MHz, $Z_{LOAD}$ = 100 $\Omega$ un-matched |     | -4.6 |     | dB   |

|                     |                                            | $F_{in}$ = 2.6 GHz, BW = 400 MHz, $Z_{LOAD}$ = 100 $\Omega$ matched    |     | -9.7 |     | dB   |

|                     | Differential Ouput Reference Impedance     |                                                                        |     | n/a  |     | Ω    |

| S12                 | Reverse isolation                          | F <sub>in</sub> = 2.6 GHz                                              |     | -25  |     | dB   |

| CMRR                | Common Mode Rejection Ratio <sup>(2)</sup> |                                                                        |     | 28   |     | dB   |

| Switchir            | ng and Digital input characteristics       |                                                                        |     |      | ¥   |      |

|                     | Fast Turnon-time                           |                                                                        |     | 0.5  |     | μs   |

| V <sub>IH</sub>     | High-Level Input Voltage                   | EN pin                                                                 | 1.4 |      |     | V    |

| V <sub>IL</sub>     | Low-Level Input Voltage                    | EN pin                                                                 |     |      | 0.5 | V    |

| I <sub>IH</sub>     | High-Level Input Current                   | EN pin                                                                 |     | 50   | 250 | μA   |

| IIL                 | Low-Level Input Current                    | EN pin                                                                 |     | 2    | 5   | μA   |

| DC curre            | ent and Power Consumption                  |                                                                        |     |      | ¥   |      |

| I <sub>VDD_ON</sub> | Supply Current                             |                                                                        |     | 84   |     | mA   |

| I <sub>VDD_PD</sub> | Power Down Current                         |                                                                        |     | 10   |     | mA   |

| P <sub>dis</sub>    | Power Dissipation on 3.3 V Supply          |                                                                        |     | 275  |     | mW   |

(2) CMRR is calculated using (S21-S31)/(S21+S31) for Receive (1 is input port, 2 & 3 are differential output ports)

## 7 Detailed Description

### 7.1 Overview

The SN9226 is a single-ended 50  $\Omega$  input to differential 50  $\Omega$  or 100  $\Omega$  output RF gain block amplifier used in 5G m-MIMO base station for TDD receive application. The device provides ~ 16.5 dB power gain with excellent linearity and noise performance at 2.6 GHz center frequency across the 1dB bandwidth of 400 MHz. The device is internally matched for 50- $\Omega$  input impedance. The device differential output matches to a TI transceiver - SN1710796 impedance which has Zero-IF analog front end, as shown in Application and Implementation. The differential output can interface to 100  $\Omega$  impedance with (or without) external matching circuitry at 2.6 GHz, providing approximately 0.5 dB gain increase (or decrease) compared to the 50  $\Omega$  output impedance scenario. See Typical Application for differential 50  $\Omega$  or 100  $\Omega$  output matching interface information.

The SN9226 has an on-chip active bias circuitry to maintain device performance over a wide temperature and supply voltage range. The included power down function allows the amplifier to shut down and saving power when the amplifier is not needed. Fast shut down and start up enable the amplifier to be used in a host of time division duplex (TDD) applications.

Operating on a single 3.3 V supply and consuming 84 mA of typical supply current, the devices are available in a 2 mm x 2mm 12-pin QFN package.

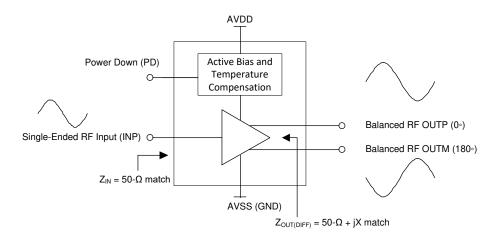

### 7.2 Functional Block Diagram

### 7.3 Feature Description

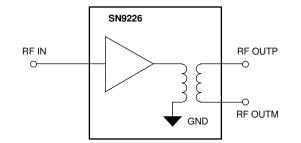

The SN9226 device is single-ended 50  $\Omega$  input to differential 50  $\Omega$  or 100  $\Omega$  output RF gain block amplifier operating at 2.6 GHz to provide active balun functionality. The device integrates the functionality of a single-ended RF amplifier and passive balun in traditional receive applications achieving small form factor with comparable linearity and noise performance, as shown in Figure 1.

The active balun implementation coupled with higher operating temperature of 105°C allows for more robust receiver system implementation compared to passive balun that is prone to reliability failures at high temperatures. The high temperature operation is achieved by the on-chip active bias circuitry which maintains device performance over a wide temperature and supply voltage range.

### Feature Description (continued)

### Figure 1. Single-Ended Input to Differential Output, Active Balun Implementation

### 7.4 Device Functional Modes

The SN9226 features a PD pin which should be connected to GND for normal operation. For power off mode, connect the PD pin to a logic high voltage of 1.8V.

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The SN9226 is a single-ended 50  $\Omega$  input to differential 50  $\Omega$  or 100  $\Omega$  output RF gain block amplifier, used in the receive path of a 2.6 GHz center frequency 5G wireless base station. The device replaces the traditional single ended RF amplifier and passive balun offering a smaller foot-print solution to the customer. It is recommended to follow good RF layout and grounding techniques to maximize the device performance.

### 8.2 Typical Application

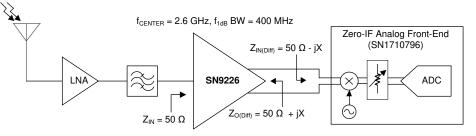

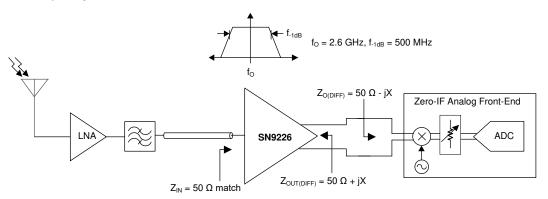

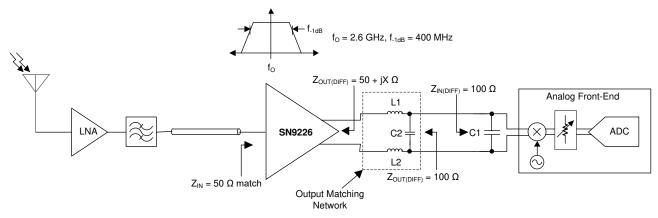

The SN9226 is typically used in a four transmit and four receive (4T/4R) array of active antenna system for 5G TDD m-MIMO or Small cell base station applications. A single receive channel of such a system (see Figure 2) consists of a low noise amplifier (LNA) that sits close to the antenna and drives the signal into a long single-ended 50  $\Omega$  coaxial cable. The SN9226 converts this single ended RF signal received from the coax into differential signal offering low noise and distortion performance while interfacing with the receiver analog front-end (AFE).

It is important that the SN9226 input impedance is matched to 50  $\Omega$  to prevent any signal reflections due to the long coax cable. The device differential output interfaces directly with the differential input of TI Zero-IF analog front end without the need of any external matching components (see Figure 2). The matching is optimized for 2.6 GHz center frequency with 400MHz of 1dB Bandwidth.

Figure 2. SN9226 in Receive application driving a TI Analog Front-End

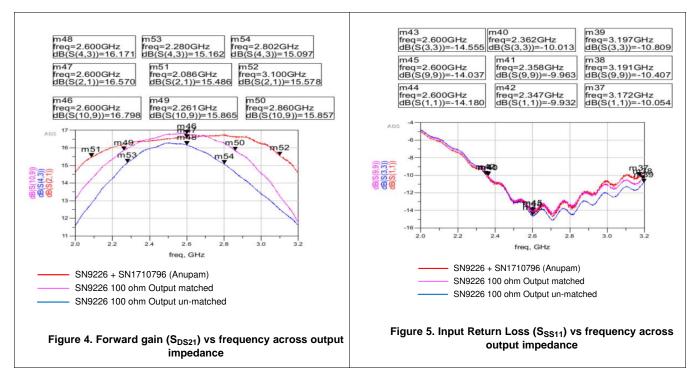

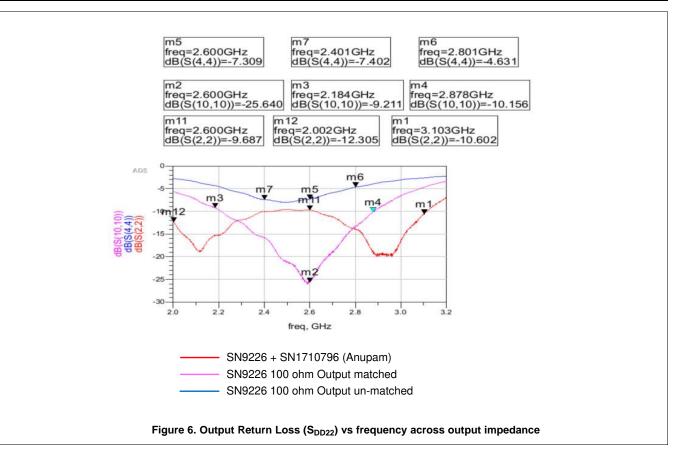

For interfacing with 100  $\Omega$  differential input analog front-end, an external matching circuitry can be used close to the LMH9226 output as shown in Figure 3. Table 1 shows example recommended component values while transforming the SN9226 output impedance from 50  $\Omega$  to 100  $\Omega$ . The component values for 100  $\Omega$  matching scenario will need to be tweaked on board depending upon the trace length between the matching circuitry and the analog front end input. It is important to select LC component values with Q(min) > 30 and that have the self resonant frequency (SRF) sufficiently higher than the desired frequency of operation. Figure 4 to Figure 6 gives the SN9226 device performance when interfacing with SN1710796. The curves also give device performance with and without matching when driving a 100  $\Omega$  differential output. As you can see in Figure 4, the forward path gain (S<sub>DS21</sub>) is slightly lower (approximately 0.8 dB) for the 100  $\Omega$  differential output impedance when it is driving an unmatched 100  $\Omega$  compared to a matched 100  $\Omega$  load.

#### **SN9226** <u>SBOS990 – DECEMBER</u> 2019

#### www.ti.com

### **Typical Application (continued)**

Table 1. Recommended Component values for 100 Ω matching

| Component | Values |

|-----------|--------|

| L1, L2    | 2.4 nH |

| C2        | 0.7 pF |

### 8.2.1 Design Requirements

### 8.2.2 Detailed Design Procedure

### 8.2.3 Application Curves

### 9 Power Supply Recommendations

The SN9226 device operates on a common nominal 3.3 V supply voltage. It is recommended to isolate the supply voltage through decoupling capacitors placed close to the device. Select capacitors with self-resonant frequency near the application frequency. When multiple capacitors are used in parallel to create a broadband decoupling network, place the capacitor with the higher self-resonant frequency closer to the device.

SN9226 SBOS990 - DECEMBER 2019

## 10 Layout

- 10.1 Layout Guidelines

- 10.2 Layout Example

www.ti.com

Figure 7.

TBD

### **11** Device and Documentation Support

### 11.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.2 Trademarks

All trademarks are the property of their respective owners.

#### 11.3 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

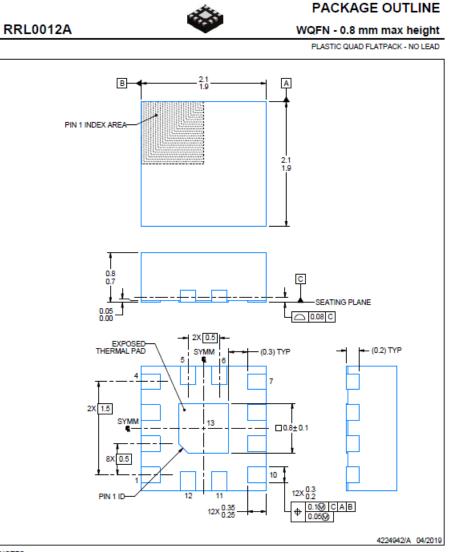

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

NOTES:

Submit Documentation Feedback

All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

14

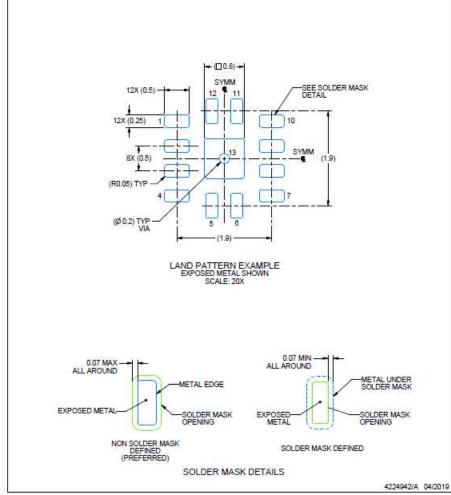

**RRL0012A**

#### www.ti.com

### EXAMPLE BOARD LAYOUT

#### WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

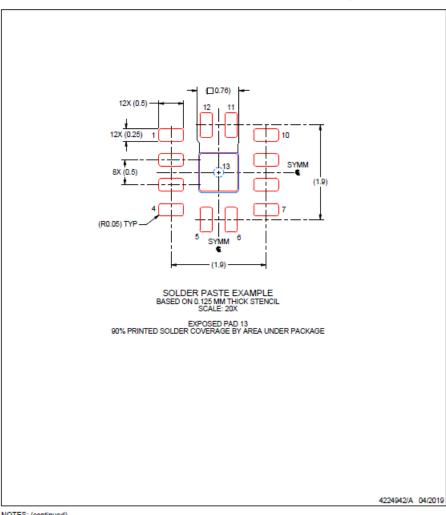

**RRL0012A**

Texas INSTRUMENTS

www.ti.com

## EXAMPLE STENCIL DESIGN

#### WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

16 Submit Documentation Feedback

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated