## DRV110 Non-Uniform PWM Explanation

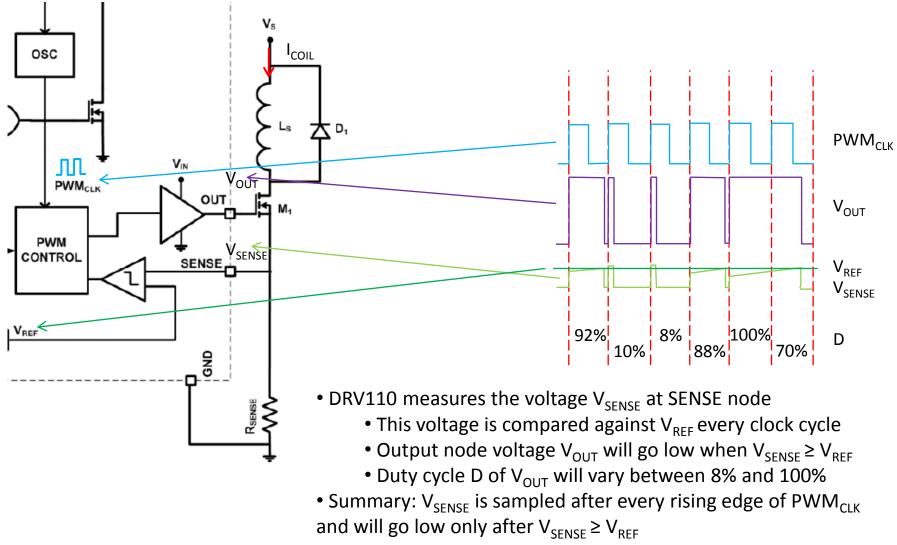

## **Current Control of DRV110**

• Minimum D=8%

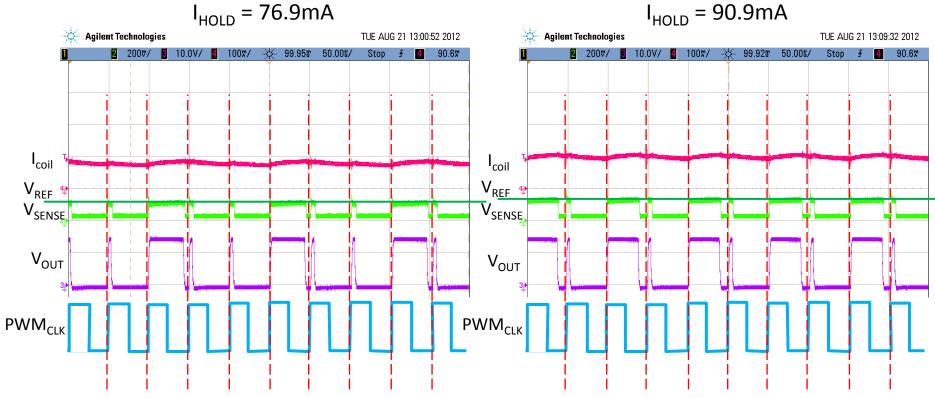

## Measurement Plots Explained – Medium I<sub>HOLD</sub> Settings

- $PWM_{CLK}$  is internal PWM clock signal, not visible outside

- Decision made by current control during every clk cycle (50us interval for PWM 20kHz frequency)

- At least ~8% (duty cycle) pulse given out every clock cycle

- Duty cycle can go up to 100%, even for several consecutive clk cycles

- $\rightarrow$  <u>V<sub>out</sub> signal does not always show the PWM frequency, especially with high I<sub>HOLD</sub> settings</u>

- Note that the sensing comparator has also tens of mV hysteresis

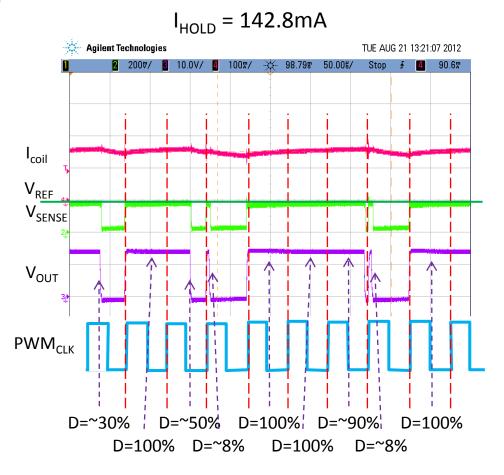

## Measurement Plots Explained – High I<sub>HOLD</sub> Setting

- Duty cycle explained for each PWM cycle

- of the  $I_{HOLD}$  =142.8mA setting

- Measured value 151mA

- Accuracy ~6%

- In line with data sheet

- As seen from the individual duty cycle values, duty cycle can for each pulse

- $\bullet$  Due to cycle-by-cycle control of  $V_{\text{SENSE}}$  against  $V_{\text{REF}}$

- Duty cycle depends on the inductance and on-resistance of the coil

- This control helps to reduce EMI issues

- Internal PWM clock PWM<sub>CLK</sub> is fixed frequency, but this signal not visible outside of IC

- $\bullet$  If you want to verify the  $f_{PWM}$  setting, need to use so small  $I_{HOLD}$  setting that you always have duty cycle <100%