Table 8-102. IC\_CTRL1 Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                   |

|-----|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EN_DRV   | R/W  | 0b    | Enable gate drivers.  0b = Gate driver output disabled and passive pulldowns enabled.  1b = Gate driver outputs enabled.                                                                                      |

| 6   | EN_OLSC  | R/W  | Ob    | Enable offline open load and short circuit diagnostic.  0b = Disabled.  1b = VDS monitors set into real-time voltage monitor mode and offline diagnostics current sources enabled.                            |

| 5-4 | BRG_MODE | R/W  | 00b   | Israge PVM control mode<br>00b = Independent Half-Bridge<br>01b = H-Bridge FH/EN<br>10b = H-Bridge PVM<br>11b = Solenoid Control                                                                              |

| 3-1 | LOCK     | R/W  | 011b  | Lock and unlock the control registers. Bit settings not listed have no effect. 011b = Unlock all control registers. 110b = Lock the control registers by ignoring further writes except to the LOCK register. |

| 0   | CLR_FLT  | R/W  | 0b    | Clear latched fault status information.  0b = Default state. 1b = Clear latched fault bits, resets to 0b after completion. Will also clear SPI fault and watchdog fault status.                               |

## Ω1

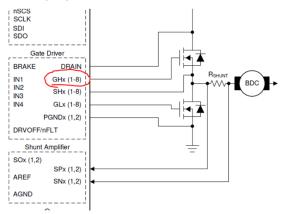

When EN\_OLSC function is activated (1b), is the overcurrent protection function via VDS below unusable? Even if VDS\_LVL below is adjusted, the protection function is not activated. Is there no way to use VDS Overcurrent protection function while EN\_OLSC function is activated?

Table 8-52. DRV\_CTRL1 Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                                                                                                                                                              |

|-----|------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6 | VGS_MODE   | R/W  | 00b   | VGS gate fault monitor mode for half-bridges 1-8.  00b = Latched fault.  01b = Cycle by cycle.  10b = Warning report only.  11b = Disabled.                                                              |

| 5   | VGS_IND    | R/W  | 0b    | VGS fault independent shutdown mode configuration.  0b = Disabled. VGS fault will shut down all half-bridge drivers.  1b = Enabled. VGS gate fault will only shutdown the associated half-bridge driver. |

| 4   | VGS_LVL    | R/W  | 0b    | VGS threshold comparator level for dead-time handshake and VGS fault monitor for half-bridge drivers.<br>0b = 1.4 V   1b = 1 V                                                                           |

| 3   | VGS_HS_DIS | R/W  | 0b    | VGS dead-time handshake monitor disable. 0b = 0x0 1b = Disabled. Half-bridge transition is based only on TDRIVE and programmable digital dead-time delays.                                               |

| 2-1 | VDS_MODE   | R/W  | 00Ь   | UDS. cuercurrant monitor mode for half-bridges 1-8.  00b = Latched fault.  01b = Cycle by cycle. 10b = Warning report only. 11b = Disabled.                                                              |

| 0   | VDS_IND    | R/W  | 0b    | VDS fault independent shutdown mode configuration.  0b = Disabled. VDS fault will shut down all half-bridge drivers.  1b = Enabled. VDS gate fault will only shutdown the associated half-bridge driver. |

| Table 8-58. VDS_CTRL1 Register Field Descriptions |           |      |       |                                                                                                                                                                                                                               |  |  |  |  |

|---------------------------------------------------|-----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit                                               | Field     | Туре | Reset | Description                                                                                                                                                                                                                   |  |  |  |  |

| 7-4                                               | VOS_LVL_1 | R/W  | 1101b | Half-bridge 1 VDS overcurrent monitor threshold.  00001b = 0.08 V  0001b = 0.08 V  0001b = 0.10 V  0011b = 0.12 V  0101b = 0.14 V  0101b = 0.18 V  0110b = 0.18 V  0110b = 0.3 V  1001b = 0.4 V  1001b = 0.4 V  1001b = 0.4 V |  |  |  |  |

## Q2.

When DRV8718 enters ACTIVE MODE, the VGS of the external HIGH SIDE FET automatically becomes HIGH. Is there any way to turn that function OFF?