### LMK05318B TICS Pro GUI Overview

2022-09-01

**CTS Apps & Systems**

### Introduction

In order to program the LMK05318B using TICS Pro, the following procedure must be performed:

- 1. Establish communication between the LMK05318B and TICS Pro

- 2. Initialize key features of the device on the Wizard home page

- 3. Configure the XO input

- 4. Set the outputs

- 5. Set the reference and its validation detectors

- 6. Configure the DPLL

### **Step 1: Establish Connection**

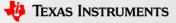

### Step 1a: Open the LMK05318B Profile

Navigate to Select Device → Network

Synchronizer Clock (Digital PLLs) →

LMK05318B to open the correct profile.

4

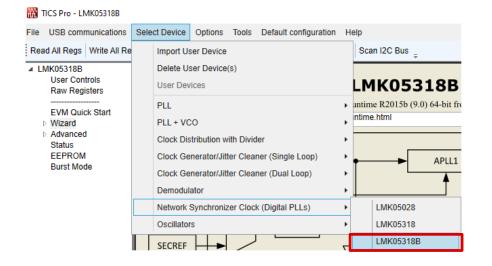

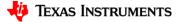

### Step 1b: Establish Connection between TICS Pro and the LMK05318B (I2C)

- To establish connection between the device and GUI, navigate to USB communications → Interface in the toolbar.

- Once **Interface** has been selected, a communication setup window will appear.

- In the window, select the USB2ANY interface, select a USB2ANY ID number, set the protocol to I2C and then press Scan I2C Bus.

- Once the I2C bus has been scanned and a address is found, you will have obtain successful connection.

### Step 1b: Establish Connection between TICS Pro and the LMK05318B (SPI)

- To establish connection between the device and GUI, navigate to USB communications → Interface in the toolbar.

- Once **Interface** has been selected, a communication setup window will appear.

- In the window, select the USB2ANY interface, select a USB2ANY ID number, and then set the protocol to SPI.

- When using SPI, ensure that the jumpers are set as shown here:

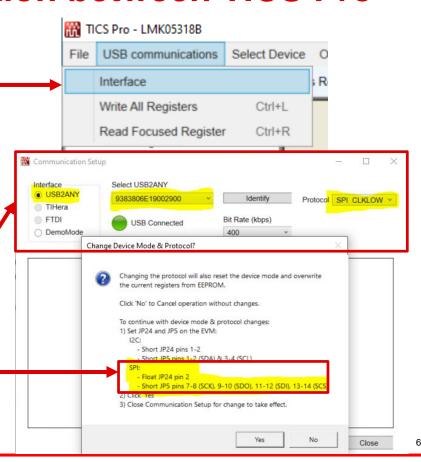

# Step 2: Initialize key features of the device on the Wizard home page

# Step 2: Initialize key features of the device on the Wizard home page

- Navigate to the Wizard home page

- The wizard home page will be used to initialize key devices.

- Key features:

- Select whether the DPLL will be used.

- Determine APLL2's reference clock.

- VCO1 Cascaded Mode

- Recommended setting as it will result in better output phase noise performance for APLL2 clocks.

- XO

- Decide if PRIREF or SECREF is 1PPS.

- Decide if the register settings need to be compatible with the non-B version.

### **Step 3: Configure the XO input**

### **Step 3: Configure the XO input**

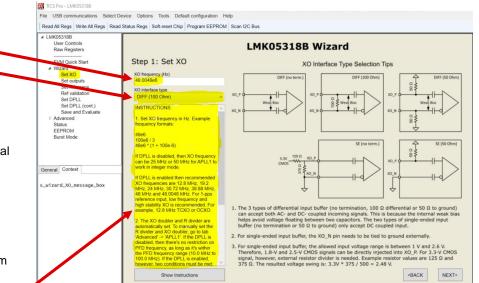

- Navigate to the Set XO page

- The Set XO page is used to configure the XO input

- Enter your desired XO frequency

- Enter your desired XO interface type

- Interface options are:

- DIFF (no term.)

- Used for AC or DC coupled differential input types where terminations are external to the input.

- DIFF (100 Ohm)

- Used for AC or DC coupled differential input types. 100 ohm termination set internal to LMK05318B, so no external termination required.

- DIFF (50 Ohm)

- Used for DC-coupled HCSL input.

- SE (no term.)

- Used for DC-coupled LVCMOS input.

- SE (50 ohm)

- Used for DC-coupled LVCMOS input and places a 50 ohm to GND on XO\_P pin.

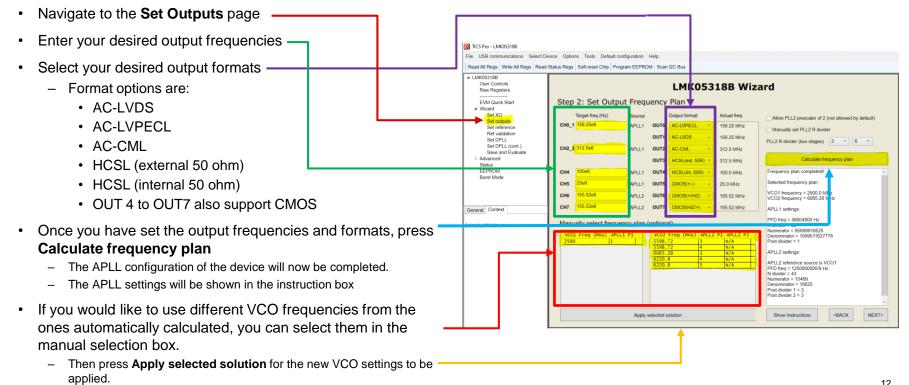

# Step 4: Set the output frequencies and output format types

#### Step 4: Set the output frequencies and output format types

# **Step 5: Set the reference and its validation detectors**

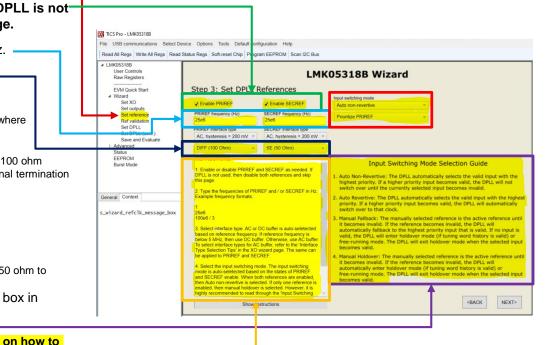

### **Step 5A: Set the reference**

- Navigate to the **Set reference** page

- Enable or disable PRIREF and SECREF as needed. If DPLL is notused, then disable both references and skip this page.

- Type the frequencies of PRIREF and / or SECREF in Hz.

- · Enter your desired REF interface type-

- Interface options are:

- DIFF (no term.)

- Used for AC or DC coupled differential input types where terminations are external to the input.

- DIFF (100 Ohm)

- Used for AC or DC coupled differential input types. 100 ohm termination set internal to LMK05318B, so no external termination required.

- DIFF (50 Ohm)

- Used for DC-coupled HCSL input.

- SE (no term.)

- Used for DC-coupled LVCMOS input.

- SE (50 ohm)

- Used for DC-coupled LVCMOS input and places a 50 ohm to GND on the \_P pin of the reference

- Select the input switching mode and priorities inside red box in image

- descriptions of each mode are shown here

- The Instructions message box provides more information on how to configure your reference inputs. Please read for greater details.

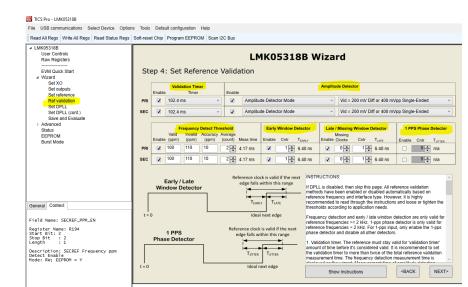

## **Step 5B: Set the reference validation detectors overview**

- If DPLL is disabled, then skip this page.

- All reference validation methods have been enabled or disabled automatically based on reference frequency and interface type.

- However, it is highly recommended to read through the instructions and loose or tighten the thresholds according to application needs.

- The Frequency Detect Threshold, Early Window Detector, and Late/Missing Window Detector are only valid for reference frequencies >= 2 kHz.

- The **1-PPS Phase Detector** is only valid for reference frequencies < 2 kHz.

- For 1-pps input, only enable the **1-pps phase** detector and disable all other detectors.

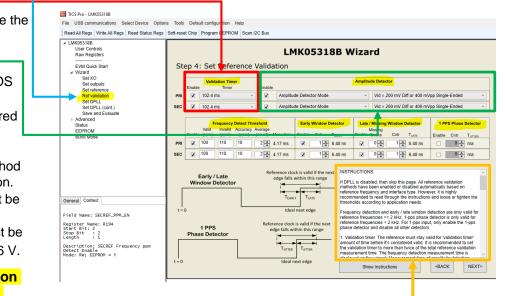

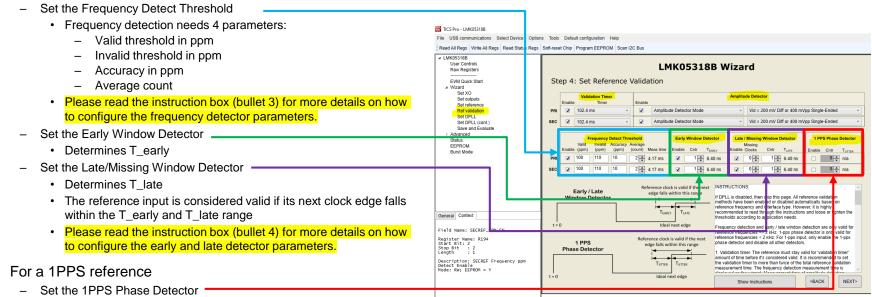

# **Step 5C: Set the reference validation detectors configuration**

- Navigate to the Ref validation page

- Set the Validation Timer

- The validation timer setting determines the amount of time the reference must stay valid before it's considered valid.

- Set the Amplitude Detector

٠

- There are two modes: amplitude detector mode and CMOS slew rate detector mode

- In amplitude detector mode, the reference is considered valid if the signal swing is higher than the selected threshold.

- In CMOS slew rate detector mode, the detection method can be either slew rate detection or VIH / VIL detection.

- For slew rate detection, the input slew rate must be faster than 0.2 V/ns.

- For VIH / VIL detection, the input high level must be above 1.8 V and the low level must be below 0.6 V.

- The Instructions message box provides more information on how to configure your reference validation settings. Please read for greater details.

# **Step 5C: Set the reference validation detectors configuration (continued)**

• For reference frequencies >= 2 kHz

• Determines T\_jitter

٠

• The reference input is considered valid if its next clock edge falls within the T\_jitter range

🦆 Texas Instruments

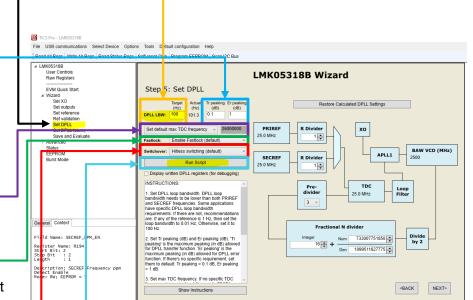

## **Step 6: Configure the DPLL**

### **Step 6: Configure the DPLL**

- Navigate to the Set DPLL page-

- Set the DPLL loop bandwidth

- The DPLL loop bandwidth needs to be lower than both PRIREF and SECREF frequencies

- Set Tr peaking (dB) and Er peaking (dB)

- Tr peaking is the maximum peaking (in dB) allowed for DPLL transfer function

- default: Tr peaking = 0.1 dB

- Er peaking is the maximum peaking (in dB) allowed for DPLL error function.

- Default: Er peaking = 1 dB

- Set max TDC frequency

- If no specific TDC frequency is required, set the max to 26 MHz

- · Fastlock should only be disabled for 1pps input

- For most use cases, switchover method should always be set to 'hitless switching'.

- Click 'Run Script' button and wait for 1 ~ 2 minutes while the script is running. Make sure that the MATLAB runtime is installed as instructed in the first wizard page.

### Step 6: Configure the DPLL (continued)

- Navigate to the Set DPLL (cont.) page

- Configure the BAW Frequency Lock Detect

- Disable if DPLL is enabled

- Used to determine if BAW (VCO1) is locked

- Configure the DPLL Frequency Lock Detect

- Used to determine if DPLL is frequency locked

- Configure the DPLL Phase Lock Detect

- Used to determine if DPLL is phase locked

- Configure the Tuning Word History

- This block sets the tuning word history for holdover.

- Refer to datasheet section '9.3.7.4 Tuning Word History' for details.

- The Instructions message box provides more information on how to configure the lock detectors and tuning word history settings. Please read for greater details.

| MK05318B Wizard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAW Frequency Lock Detect         [2] enable         Set Default           Immediad to         Lock gom         Unit gom         Average         Accy (gom)         Meas           bibid         This         10         2         1         19.20         1         19.20           bibid         This         DPLL Frequency Lock Detect         [2] enable         Set Default         Set Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| tended to be consistent of the second secon |

| tended to be consistent of the second secon |

| tended to Lock port Unik port Average Accy (port) Meast<br>bled. This<br>foce works in<br>reschold in The BAVY DPLL Frequency Lock Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| blod. This<br>for works in<br>reshold in<br>DPLL Frequency Lock Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Intershold in<br>The BAW DPLL Frequency Lock Detect I I enable Set Default Set Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nreshold in<br>. The BAW DPLL Frequency Lock Detect  ✓ enable Set Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| is locked, 1 10 10 1 96.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| old in ppm =<br>BAW lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DPLL Phase Lock Detect Recommende                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| esholds in Lock cot Lock thresh Lielk cot Lielk thresh Meas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| cy error 28 - 384,96 ps 32 - 6.16 ns 9.87 r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| nold. The Tuning Word History ✓ enable Min Values Requ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| letect, click Hist cnt Avg time Delay cnt Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8 115 34 ms 44 20 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| calculated HIST_INTMD No intermediate update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| nce and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LL is phase DPLL_TUNING_FREE_RUN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LLIS phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### **Appendix: Additional GUI Features**

### **Appendix Introduction**

- The following appendix slides will display additional features of the LMK05318B.

- Please note that these are features are not required for obtaining an initial configuration, but can be beneficial features after the initial configuration is created by following steps 1 to 6 on the previous slides.

- The additional features include:

- Status page

- DCO and ZDM page

- Outputs page

- EEPROM page

- APLL1 page

- APLL2 page

- User controls page

- Raw registers page

### **Status Page**

- The Status Page can be used to validate the device is locking properly

- LOS\_FDET\_XO and LOS\_XO indicate whether a clock is present at the XO input for the APLLs to lock to

- When the bits are low, the XO is present and valid

- LOL\_PLL1 and LOL\_PLL2 indicate whether the APLLs are locking to the XO input

- When the bits are low, the APLLs are locked properly

- LOPL\_DPLL and LOFL\_DPLL indicate whether the DPLL is frequency and phase locked to the REF input

- When the bits are low, the DPLL has successful locked to the REF input

- HLDOVER indicates whether the device is in holdover

- PRIREF\_VALSTAT and SECREF\_VALSTAT indicate whether the PRIREF or SECREF are present and validated by the reference validation detectors set in step 5

- When the bits are high, the reference is valid

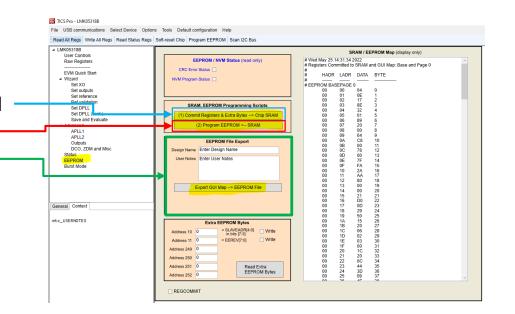

### **EEPROM Page**

- The EEPROM page contains the following features:

- Program the EEPROM

- To program the EEPROM, you must

- Commit the register to the SRAM

- Program the EEPROM

- Export the GUI Map to a EEPROM file

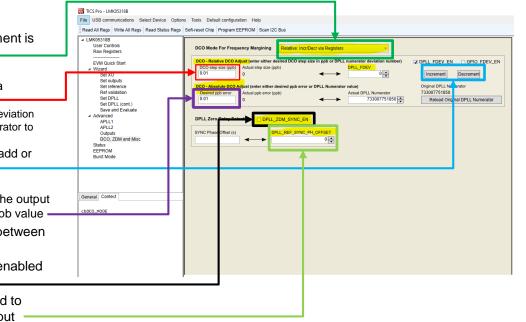

### **DCO and ZDM Page**

- The DCO and ZDM Page can be used to:

- Perform frequency/phase adjustments with the DCO

- DCO adjustments can be performed relatively or absolutely

- Relative adjustment

- » Enter a ppb adjustment that is required and a DPLL\_FDEV will be calculated

- » The DPLL\_FDEV will be the numerator deviation that will be adjusted from the DPLL numerator to result in the required ppb adjustment

- » Press the Increment or decrement button to add or subtract the required ppb adjustment

- Absolute adjustment

- » Enter a ppb adjustment that is required and the output clock will automatically be adjusted by that ppb value –

- Enable zero-delay mode to achieve phase alignment between the input clock and output clock on OUT7

- When the DPLL\_ZDM\_SYNC\_EN is set, ZDM is enabled to achieve input and output phase alignment

- The DPLL\_REF\_SYNC\_PH\_OFFSET can be used to adjust the phase offset between the input and output clocks

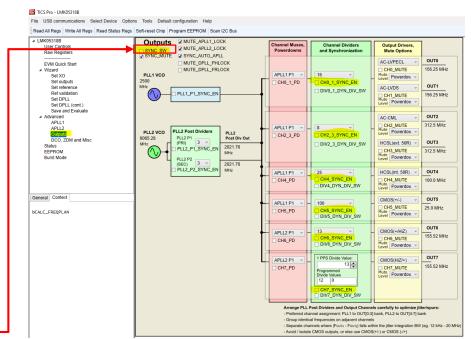

### **Outputs Page**

- The channel muxes, channel dividers, output formats, and output frequencies shown on the outputs page are configured in step 4

- The outputs page provides the following additional features:

- Output clock synchronization

- Output sync can be accomplished by enabling the CHx\_SYNC\_EN bits highlighted in the image to the right

- For the synchronization to take place, the SYNC\_SW bit must be toggled (turned on/off)

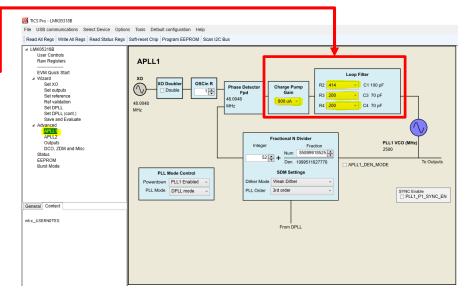

### **APLL1 Page**

- The APLL1 page can be used to configure the charge pump current and loop filter to optimize the output clocks performance

- The rest of the controls on this page will be configured in step 4 and should not be change

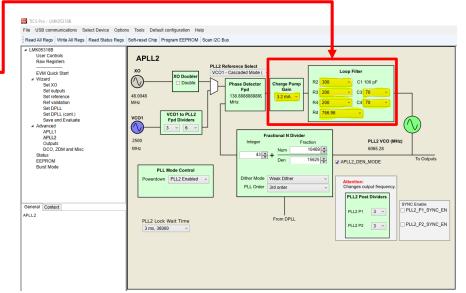

### **APLL2 Page**

- The APLL2 page can be used to configure the charge pump current and loop filter to optimize the output clocks performance

- The rest of the controls on this page will be configured in step 4 or step 2 and should not be change

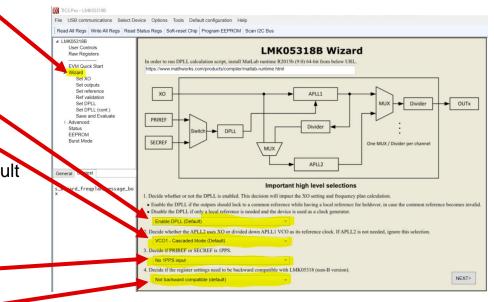

### **User Controls Page**

- The user control page contains register controls that may not be included on the other GUI pages

- For example, the device info registers such as PRTID, PRODID, etc.

| 🛗 TICS Pro - LMK05318B                                                                                | - 0                                 | × |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|-------------------------------------|---|--|--|--|--|--|

| File USB communications Select Device Option                                                          | ns Tools Default.configuration Help |   |  |  |  |  |  |

| Read All Regs   Write All Regs   Soft-reset Chip   Program EEPROM   Scan 12C Bus                      |                                     |   |  |  |  |  |  |

| LMK05318B     User Controls                                                                           | Collapse All Expand All             |   |  |  |  |  |  |

| Raw Registers                                                                                         | Device info                         |   |  |  |  |  |  |

| EVM Quick Start<br>Wizard                                                                             | Device Control Registers            |   |  |  |  |  |  |

| Set XO<br>Set outputs                                                                                 | START UP                            |   |  |  |  |  |  |

| Set reference<br>Ref validation<br>Set DPLL                                                           | €EPROM                              |   |  |  |  |  |  |

| Set DPLL (cont.)<br>Save and Evaluate                                                                 | O DPLL                              |   |  |  |  |  |  |

| <ul> <li>Advanced</li> <li>APLL1</li> </ul>                                                           | O DEPUG REGISTERS                   |   |  |  |  |  |  |

| APLL2<br>Outputs                                                                                      | DEVICE CONTROL 1 NVMBASE REGISTERS  |   |  |  |  |  |  |

| DCO, ZDM and Misc<br>Status<br>EEPROM                                                                 | DEVICE CONTROL 2 NVMPAGE REGISTERS  |   |  |  |  |  |  |

| Burst Mode                                                                                            | NVM COMMON NVMBASE REGISTERS        |   |  |  |  |  |  |

|                                                                                                       | MEMORY NONNUM REGISTERS             |   |  |  |  |  |  |

|                                                                                                       | O DPLL REF NVMPAGE REGISTERS        |   |  |  |  |  |  |

| General Context                                                                                       | Pns                                 |   |  |  |  |  |  |

| User Controls                                                                                         |                                     |   |  |  |  |  |  |

| This page generally contains register<br>controls that may NOT be included on<br>the other GUI pages. |                                     |   |  |  |  |  |  |

|                                                                                                       |                                     |   |  |  |  |  |  |

### **Raw Registers Page**

The raw register page allows for low-level register write/read operations by register address

|                                       | Read All Regs   Withe All Regs   Self-reset Chip   Program EEPROM   Scan IZC Bus |                                         |                     |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|---------------------|--|--|--|

| LMK05318R                             |                                                                                  |                                         |                     |  |  |  |

| User Controls                         | Register Map                                                                     | 2 2 2 2 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 |                     |  |  |  |

| Raw Registers                         | Register Name Address/Value                                                      | 3210 9876 5432 10 98 7654 3210          | Deta                |  |  |  |

| Edited Street, Solar State            | R0 0x000010                                                                      | 0000 0000 0000 0000 0001 0000           | 0x                  |  |  |  |

| EVM Quick Start                       | R1 0x00010B                                                                      |                                         |                     |  |  |  |

| ▲ Wizard                              | R2 0x000235                                                                      |                                         | Write Register      |  |  |  |

| Set XO                                | R3 0x000332                                                                      | 0000 0000 0000 0011 0011 0010           |                     |  |  |  |

| Set outputs                           | R4 0x000404                                                                      | 0000 0000 0000 0100 0000 0100           | Read Register       |  |  |  |

| Set reference                         | R5 0x00050E                                                                      | 0000 0000 0000 0101 0000 1110           | Read All Registers  |  |  |  |

| Ref validation                        | R6 0x000617                                                                      | 0000 0000 0000 0110 0001 0111           | Reau All Registers  |  |  |  |

| Set DPLL                              | R7 0x00078E                                                                      | 0000 0000 0000 0111 1000 1110           | Write All Registers |  |  |  |

| Set DPLL (cont.)                      | R8 0x000802                                                                      | 0000 0000 0000 1000 0000 0010           | tring to registers  |  |  |  |

| Save and Evaluate<br>Advanced         | R10 0x000AC8                                                                     | 0000 0000 0000 1010 1100 1000           |                     |  |  |  |

| Advanced<br>APLL1                     | R11 0x000800                                                                     | 0000 0000 0000 1011 0000 0000           |                     |  |  |  |

| APLL1<br>APLL2                        | R12 0x000C18                                                                     | 0000 0000 0000 1100 0001 1011           | Import Register Map |  |  |  |

| Outputs                               | R13 0x000008                                                                     | 0000 0000 0000 1101 0000 1000           |                     |  |  |  |

| DCO. ZDM and Misc                     | R14 0x000E00                                                                     | 0000 0000 0000 1110 0000 0000           | Export Register Map |  |  |  |

| Status                                | R15 0x000F0D                                                                     | 0000 0000 0000 1111 0000 0000           |                     |  |  |  |

| EEPROM                                | R16 0x001000<br>R17 0x001110                                                     | 0000 0000 0001 0000 0000 0000           |                     |  |  |  |

| Burst Mode                            | R17 0x001110<br>R18 0x0012FF                                                     |                                         | Register/Field Name |  |  |  |

|                                       | R19 0x001308                                                                     |                                         | Name                |  |  |  |

|                                       | R20 0x001420                                                                     |                                         | Value               |  |  |  |

|                                       | R21 0x001501                                                                     |                                         | Verue               |  |  |  |

|                                       | R22 0x001600                                                                     | 0000 0000 0001 0110 0000 0000           | Read                |  |  |  |

|                                       | R23 0x001755                                                                     | 0000 0000 0001 0111 0101 0101           |                     |  |  |  |

| · · · · · · · · · · · · · · · · · · · | R24 0x001855                                                                     | 0000 0000 0001 1000 0101 0101           |                     |  |  |  |

| Seneral Context                       | R25 0x001900                                                                     | 0000 0000 0001 1001 0000 0000           | Address Bits        |  |  |  |

| aw Registers                          | R26 0x001A00                                                                     | 0000 0000 0001 1010 0000 0000           |                     |  |  |  |

| his page allows low-level register    | R27 0x001B00                                                                     | 0000 0000 0001 1011 0000 0000           |                     |  |  |  |

| rite/read operations by register      | R28 0x001C01                                                                     | 0000 0000 0001 1100 0000 0001           |                     |  |  |  |

| ddress, or read by register field     | R29 0x001D13                                                                     | 0000 0000 0001 1101 0001 0011           |                     |  |  |  |

| ane.                                  | R30 0x001E40                                                                     | 0000 0000 0001 1110 0100 0000           |                     |  |  |  |

|                                       | R32 0x002044                                                                     | 0000 0000 0010 0000 0100 0100           |                     |  |  |  |

|                                       | R35 0x002300                                                                     |                                         |                     |  |  |  |

|                                       | R36 0x002403                                                                     | 0000 0000 0010 0100 0000 0011           |                     |  |  |  |

|                                       | R37 0x002500                                                                     |                                         |                     |  |  |  |

|                                       | R38 0x002600<br>R39 0x002702                                                     |                                         |                     |  |  |  |

|                                       | R40 0x002803                                                                     |                                         |                     |  |  |  |

|                                       | R41 0x002900                                                                     |                                         |                     |  |  |  |

|                                       | R42 0x002401                                                                     |                                         |                     |  |  |  |

|                                       | R43 0x0028C2                                                                     |                                         |                     |  |  |  |

|                                       | R44 0x002C00                                                                     |                                         |                     |  |  |  |

|                                       | R45 0x002003                                                                     | 0000 0000 0010 1101 0000 0011           |                     |  |  |  |

|                                       | R46 0x002E11                                                                     | 0000 0000 0010 1110 0001 0001           |                     |  |  |  |

|                                       | R47 0x002F07                                                                     | 0000 0000 0010 1111 0000 0111           |                     |  |  |  |

|                                       | R48 0x003050                                                                     | 0000 0000 0011 0000 0101 0000           |                     |  |  |  |

|                                       | R49 0x00314A                                                                     | 0000 0000 0011 0001 0100 1010           |                     |  |  |  |

|                                       | R50 0x003200                                                                     | 0000 0000 0011 0010 0000 0000           |                     |  |  |  |

|                                       | R51 0x003318                                                                     | 0000 0000 0011 0011 0001 1000           |                     |  |  |  |

|                                       | R52 0x003410                                                                     | 0000 0000 0011 0100 0001 0000           |                     |  |  |  |

|                                       | R53 0x00350F                                                                     | 0000 0000 0011 0101 0000 1111           | 2                   |  |  |  |