# LMK5B12204 Schematic Review

The recommended pin terminations for the LMK5B12204 schematic are as follows.

## Notes:

1. P = Power, G = Ground, I = Input, O = Output, I/O = Input or Output, A = Analog, S = Configuration.

| PIN    |     |   | DESCRIPTION                                                                                                                          | PIN TERMINATION                                                                                                                                                                                                                                                        | TI Feedback                                                                                                                                                                                                              |

|--------|-----|---|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | - |                                                                                                                                      |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |

| POWER  |     |   |                                                                                                                                      |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |

| VDDO_0 | 18  | Р | <ul><li>These pins power the outputs.</li><li>1. Place a 0.1 uF</li></ul>                                                            | Step 1-3:<br>1.8/2.5/3.3V<br>FB5 WDDOx                                                                                                                                                                                                                                 | We recommend placing 6 0.1 uF capacitors                                                                                                                                                                                 |

| VDDO_1 | 19  | Р | <ul> <li>capacitor close to the supply</li> <li>2. Place a ferrite bead (recommended 220 ohm) to reduce</li> </ul>                   | C25 220 ohm C26<br>0.1µF 10µF                                                                                                                                                                                                                                          | (one 0.1 uF for each VDDO pin) for best<br>power supply filtering and output phase<br>noise performance.                                                                                                                 |

| VDDO_2 | 37  | Р | <ul> <li>crosstalk</li> <li>3. Place a 10 uF<br/>decoupling capacitor</li> <li>4. Place a 0.1 uF<br/>decoupling capacitor</li> </ul> | <u>Step 4:</u>                                                                                                                                                                                                                                                         | We recommend outputs with different<br>frequencies have their own filtering circuit<br>(steps 1-3). I believe your outputs will all be<br>the same frequency, so it is fine to share steps<br>1-3 for all the VDDO pins. |

| VDDO_2 | 40  | Р | close to each power<br>pin.<br><b>NOTE:</b> Outputs with the<br>same frequencies can                                                 | $\frac{VDDOx = 1.8, 2.5, \text{ or } 3.3 \text{ V (DIFF or HCSL)}}{VDDOx = 1.8 \text{ V (} 1.8 \text{-V LVCMOS)}}$                                                                                                                                                     |                                                                                                                                                                                                                          |

| VDDO_3 | 43  | Р | share steps 1-3 above, but<br>each pin requires its own<br>0.1 uF (step 4).                                                          | VDD0_23         37         VDD04         0.1µF         C10           VDD0_5         40         VDD05         0.1µF         C12           VDD0_6         43         VDD06         0.1µF         C13           VDD0_7         46         VDD07         0.1µF         C14 |                                                                                                                                                                                                                          |

| VDDO_3 | 46  | Р |                                                                                                                                      |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |

| VDD_XO   | 33 | Р | Power supply for XO                                                                                                                                                                                                                                                                                                 | <u>Step 1-3:</u>                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                |

|----------|----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |    |   | <ol> <li>Place a 0.1 uF<br/>capacitor close to the<br/>supply</li> <li>Place a ferrite bead<br/>(recommended 220<br/>ohm) to reduce<br/>crosstalk</li> <li>Place a 10 uF<br/>decoupling capacitor</li> <li>Place a 0.1 uF<br/>decoupling capacitor<br/>close to the pin.</li> </ol>                                 | $\frac{3.3V}{\underbrace{-0.1\mu F}} \xrightarrow{FB3} \underbrace{VDDXO}_{10\mu F}$<br>Step 4:<br>$\frac{VDDXO}{33} \underbrace{VDD_XO}_{VDD_XO}$                                                                                                                                                                                                                                            | We recommend each VDD pin have its own<br>power supply filtering circuit (steps 1-4 on<br>left) for best supply noise filtering and output<br>clock perfromance.<br>Current termination is sufficient as well. |

| VDD_PLL1 | 27 | P | <ol> <li>Power supply for APLL1</li> <li>Place a 0.1 uF<br/>capacitor close to the<br/>supply</li> <li>Place a ferrite bead<br/>(recommended 220<br/>ohm) to reduce<br/>crosstalk</li> <li>Place a 10 uF<br/>decoupling capacitor</li> <li>Place a 0.1 uF<br/>decoupling capacitor<br/>close to the pin.</li> </ol> | Step 1-3:         3.3V         FB2       VDDPLL1         C6         0.1 $\mu$ F       C6         0.1 $\mu$ F       C6         VDDPLL1         0.1 $\mu$ F       C1         VDDDIG       4         VDD DIG         VDD PLL1         VDD PLL2         VDD PLL2         VDD PLL2 | We recommend each VDD pin have its own<br>power supply filtering circuit (steps 1-4 on<br>left) for best supply noise filtering and output<br>clock perfromance.<br>Current termination is sufficient as well. |

| VDD_PLL2 | 36 | Р | Power supply for APLL2                                                                                                                                                                                                                                                              | <u>Step 1-3:</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                |

|----------|----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |    |   | <ol> <li>Place a 0.1 uF<br/>capacitor close to the<br/>supply</li> <li>Place a ferrite bead<br/>(recommended 220<br/>ohm) to reduce<br/>crosstalk</li> <li>Place a 10 uF<br/>decoupling capacitor</li> <li>Place a 0.1 uF<br/>decoupling capacitor<br/>close to the pin.</li> </ol> | $\frac{3.3V}{FB4} + \frac{VDDPLL2}{220 \text{ ohm}} + \frac{C21}{10\mu F}$ $\frac{0.1\mu F}{C} + \frac{C1}{C} + \frac{VDDDKG}{C} + \frac{4}{C} + \frac{VDD}{VDD} + \frac{10\mu F}{VDD} + \frac{10\mu F}{C} + $ | We recommend each VDD pin have its own<br>power supply filtering circuit (steps 1-4 on<br>left) for best supply noise filtering and output<br>clock perfromance.<br>Current termination is sufficient as well. |

| VDD_DIG  | 4  | P | <ul> <li>Power supply for digital</li> <li>1. Place a 1 uF capacitor close to the supply</li> <li>2. Place a 0.1 uF decoupling capacitor close to the pin.</li> </ul>                                                                                                               | Step 1:<br>3.3V<br>VDDDIG<br>C24<br>$\downarrow$<br>$\downarrow$<br>$\downarrow$<br>$\downarrow$<br>$\downarrow$<br>$\downarrow$<br>$\downarrow$<br>$\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | We recommend placing an additional 1 uF on<br>the VDD_DIG pin.                                                                                                                                                 |

|          |    |   |                                                                                                                                                                                                                                                                                     | Step 2:           0.1µF         C1         VDDDIG         4           0.1µF         C7         VDDIN         5           0.1µF         C9         VDDPLL1         27           0.1µF         C1         VDDPLL2         36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                |

| VDD_IN | 5   | Р | <ol> <li>Power supply for inputs</li> <li>Place a 0.1 uF<br/>capacitor close to the<br/>supply</li> <li>Place a ferrite bead<br/>(recommended 220<br/>ohm) to reduce<br/>crosstalk</li> <li>Place a 10 uF<br/>decoupling capacitor</li> <li>Place a 0.1 uF<br/>decoupling capacitor<br/>close to the pin.</li> </ol> | $\frac{\text{Step 1-3:}}{3.3V} + \frac{\text{FB1}}{220 \text{ ohm}} + \frac{\text{VDDN}}{C4} + \frac{\text{C4}}{10\mu\text{F}}$ $\frac{\text{Step 4:}}{5} + \frac{0.1\mu\text{F}}{0.1\mu\text{F}} + \frac{\text{C1}}{C7} + \frac{\text{VDDDKG}}{10} + \frac{4}{5} + \frac{\text{VDD}}{10} + \frac{10}{10} + \frac{10}{1$ | We recommend each VDD pin have its own<br>power supply filtering circuit (steps 1-4 on<br>left) for best supply noise filtering and output<br>clock perfromance.<br>Current termination is sufficient as well. |

|--------|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAP    | PAD | G | Tie GND (DAP) to GND                                                                                                                                                                                                                                                                                                 | PAD 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Correct termination. No changes needed.                                                                                                                                                                        |

| PIN         |     | TYPE | DESCRIPTION                                                                                                                                        | PIN TERMINATION                                                                                                                                          | TI Feedback                             |

|-------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| NAME        | NO. |      |                                                                                                                                                    |                                                                                                                                                          |                                         |

| CORE BLOCKS |     | T    |                                                                                                                                                    |                                                                                                                                                          |                                         |

| LF1         | 29  | A    | <ol> <li>Place a 470 nF<br/>capacitor on LF1</li> <li>NOTE: This is the<br/>external loop filter<br/>capacitor for APLL1</li> </ol>                | 0.47uF C22 29 LF1<br>0.1uF C23 34 LF2                                                                                                                    | Correct termination. No changes needed. |

| LF2         | 34  | A    | <ol> <li>Place a 100 nF<br/>capacitor on LF2</li> <li>NOTE: This is the<br/>external loop filter<br/>capacitor for APLL2</li> </ol>                |                                                                                                                                                          | Correct termination. No changes needed. |

| CAP_DIG     | 3   | A    | <ol> <li>Place a 10 uF<br/>capacitor on<br/>CAP_DIG</li> <li>NOTE: This is the<br/>external bypass capacitor<br/>for Digital Core Logic</li> </ol> |                                                                                                                                                          | Correct termination. No changes needed. |

| CAP_PLL1    | 28  | A    | <ol> <li>Place a 10 uF<br/>capacitor on<br/>CAP_PPL1</li> <li>NOTE: This is the<br/>external bypass capacitor<br/>for APLL1 VCO</li> </ol>         | 10μF         C15         3         CAP_DIG           10μF         C16         28         CAP_PLL1           10μF         C17         35         CAP_PLL2 | Correct termination. No changes needed. |

| CAP_PLL2    | 35  | A    | <ol> <li>Place a 10 uF<br/>capacitor on<br/>CAP_PPL2</li> <li>NOTE: This is the<br/>external bypass capacitor<br/>for APLL2 VCO</li> </ol>         |                                                                                                                                                          | Correct termination. No changes needed. |

| PIN          |     | TYPE | DESCRIPTION                                                                                                             | PIN TERMINATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TI Feedback                             |

|--------------|-----|------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| NAME         | NO. |      |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

| INPUT BLOCKS |     |      |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

| XO_P         | 31  | Ι    | <ol> <li>XO/TCXO/OCXO Input</li> <li>Please select a termination shown</li> </ol>                                       | $\begin{array}{c} VDD \\ \hline \\ LVCMOS \\ Driver \\ (R_{OUT}) \\ \hline \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ \\ R_{S} = 50 - R_{OUT} \\ \hline \\ \\ $                                                                                                                          | Correct termination. No changes needed. |

| XO_N         | 32  | Ι    | on the right that<br>matches your XO<br>input type.                                                                     | VDD         R1 (Ω)         R2 (Ω)           3.3 V         125         375           2.5 V         0         open           1.8 V         0         open           Copyright © 2020, Texas Instruments Incorporated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Correct termination. No changes needed. |

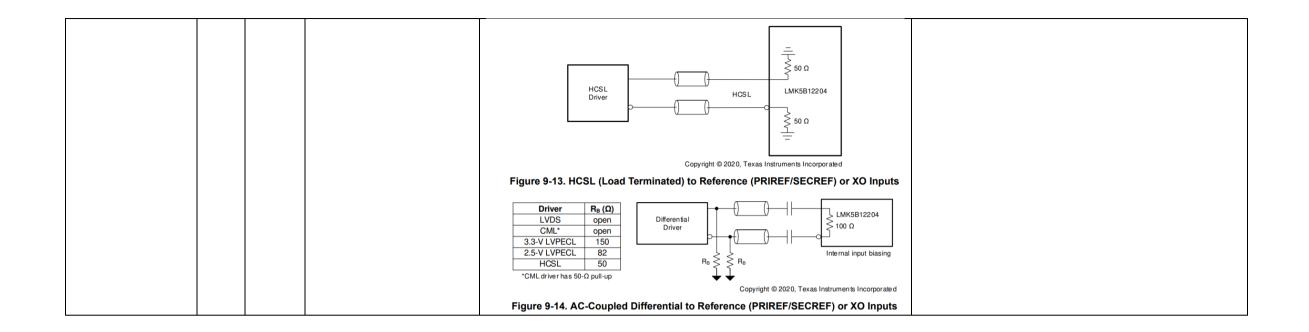

| PRIREF_P     | 6   | T    | Clock Inputs                                                                                                            | Figure 9-8. Single-Ended LVCMOS to XO Input (XO_P)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |

|              | 0   |      | <ol> <li>Please select a<br/>termination shown<br/>on the right that<br/>matches your input<br/>format type.</li> </ol> | 3.3V LVCMOS       Rs         Driver       LMK5B12204         Copyright © 2020, Texas Instruments Incorporated         Figure 9-9. Single-Ended LVCMOS (1.8, 2.5, 3.3 V) to Reference (PRIREF_P/SECREF_P)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Correct termination. No changes needed. |

| PRIREF_N     | 7   | Ι    |                                                                                                                         | LVPECL Driver<br>LVPECL Driver<br>SO Q<br>SO Q | Correct termination. No changes needed. |

|              |     |      |                                                                                                                         | LMK5B122.04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |

| SECREF_P     | 10  | I    |                                                                                                                         | LVDS Driver<br>LVDS Driver<br>Copyright © 2020, Texas Instruments Incorporated<br>Figure 9-11. DC-Coupled LVDS to Reference (PRIREF/SECREF) or XO Inputs<br>CML<br>Driver<br>CML<br>CML<br>CML<br>CML<br>CML<br>CML<br>CML<br>CML                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Correct termination. No changes needed. |

| SECREF_N     | 11  | I    |                                                                                                                         | Figure 9-12. DC-Coupled CML (Source Terminated) to Reference (PRIREF/SECREF) or XO Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Correct termination. No changes needed. |

| PIN                |     | TYPE | DESCRIPTION                                                                  | PIN TERMINATION                                                                                                                                                                | TI Feedback                             |

|--------------------|-----|------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| NAME               | NO. | -    |                                                                              |                                                                                                                                                                                |                                         |

| <b>OUTPUT BLOC</b> | CKS |      |                                                                              |                                                                                                                                                                                |                                         |

| OUT0_P             | 17  | 0    | <ol> <li>Clock Outputs</li> <li>Please select a termination shown</li> </ol> | LWK5B12204       LVCMOS       1.8 V LVCMOS         Figure 9-26. 1.8-V LVCMOS Output to 1.8-V LVCMOS Receiver                                                                   |                                         |

| OUT0_N             | 16  | 0    | on the right that<br>matches your<br>output format type.                     | LMK5B12204 AC-LVDS 100 Ω LVDS<br>AC-LVDS 100 Ω Receiver<br>Copyright © 2020, Texas Instruments Incorporated                                                                    |                                         |

| OUT1_P             | 20  | 0    |                                                                              | Figure 9-27. AC-LVDS Output to LVDS Receiver With Internal Termination/Biasing                                                                                                 |                                         |

|                    |     |      |                                                                              | LMK5B12204 AC-CML S0 Q CML Receiver                                                                                                                                            | Correct termination. No changes needed. |

| OUT1_N             | 21  | 0    |                                                                              |                                                                                                                                                                                |                                         |

|                    |     |      |                                                                              | Copyright © 2020, Texas Instruments Incorporated<br>Figure 9-28. AC-CML Output to CML Receiver With Internal Termination/Biasing                                               |                                         |

|                    |     |      |                                                                              |                                                                                                                                                                                |                                         |

| OUT2_P             | 42  | 0    | -                                                                            | LMK5B12204 AC-LVPECL CLUPECL Receiver                                                                                                                                          |                                         |

|                    |     |      |                                                                              | 50 Ω Š Š 50 Ω                                                                                                                                                                  |                                         |

| OUT2_N             | 41  | 0    | -                                                                            | VDD_IN - 1.3 V<br>Copyright © 2020, Texas Instruments Incorporated                                                                                                             |                                         |

| _                  |     |      |                                                                              | Figure 9-29. AC-LVPECL Output to LVPECL Receiver With External Termination/Biasing                                                                                             |                                         |

|                    |     |      |                                                                              | 33 Ω (optional)       LMK5B12204       HCSL                                                                                                                                    |                                         |

| OUT3_P             | 45  | 0    |                                                                              | $ \begin{array}{c c} & & & & \\ & & & & \\ & & & & \\ & & & & $                                                                                                                |                                         |

| OUT3_N             | 44  | 0    | -                                                                            | Copyright © 2020, Texas Instruments Incorporated If HCSL Internal Termination (50- $\Omega$ to GND) is enabled, short 33- $\Omega$ and remove 50- $\Omega$ external resistors. |                                         |

|                    |     |      |                                                                              | Figure 9-30. HCSL Output to HCSL Receiver With External Source Termination                                                                                                     |                                         |

|                    |     |      |                                                                              |                                                                                                                                                                                |                                         |

|              |        | TYPE | DESCRIPTION                                                                                                                                                                                                                        | N                                                                               | PIN TERMINATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TI Feedback                                                           |

|--------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| NAME         | NO.    | -    |                                                                                                                                                                                                                                    |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

| LOGIC CONTRO | L/STAT | US   |                                                                                                                                                                                                                                    |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

| HW_SW_CTRL   | 9      | I    | table below to de         6.1 Device Start-U         The HW_SW_CTRL         or ROM) used to ini         initial register setting         registers can be acc         will function as defini         INPUT LEVEL <sup>(1)</sup> O | Up Mode<br>Up Mode<br>L input pir<br>hitialize the<br>logs determinicessed thro | n selects the device start-up mode that determines the memory page (EEPROM<br>e registers, the serial interface, and the logic pin functions at power-on reset. The<br>ine the frequency configuration of the device on start-up. After start-up, the device<br>bugh the serial interface for device monitoring and programming, and the logic pins<br>selected mode.<br>Table 6-2. Device Start-Up Modes<br>MODE DESCRIPTION<br>Registers are initialized from EEPROM, and I <sup>2</sup> C interface is enabled.<br>Logic pins:<br>• SDA/SDI, SCL/SCK: I <sup>2</sup> C Data, I <sup>2</sup> C Clock (open-drain)                               | Tied low for EEPROM + I2C. Correct<br>termination. No changes needed. |

|              |        |      | (V <sub>IM</sub> ) (Sof                                                                                                                                                                                                            | PROM + SPI<br>fft pin mode)<br>ROM + I <sup>2</sup> C<br>rd pin mode)           | Registers are initialized from EEPROM, and SPI interface is enabled.         Logic pins:         • SDA/SDI, SCL/SCK: SPI Data In (SDI), SPI Clock (SCK)         • GPI00/SYNCN: Output SYNC Input (active low). Pull up externally if not used.         • GPI01/SCS: SPI Chip Select (SCS)         • GPI02/SDO/FINC: SPI Data Out (SDO)         Registers are initialized from the ROM page selected by GPIO pins, and I <sup>2</sup> C interface is enabled.         Logic pins:         • SDA/SDI, SCL/SCK: I <sup>2</sup> C Data, I <sup>2</sup> C Clock (open-drain)         • GPI02:0] (1): ROM Page Select Inputs (000b to 111b) during POR. |                                                                       |

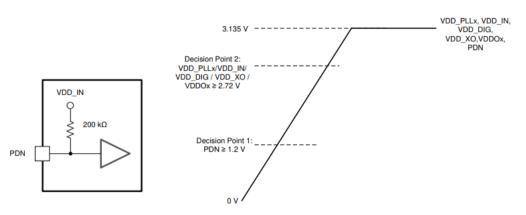

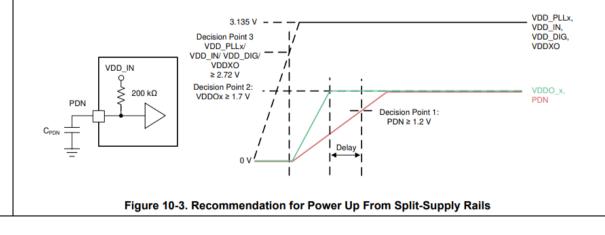

| PDN          | 13     | I    |                                                                                                                                                                                                                                    | ins are only a                                                                  | After POR, GPIO2/SDO/FINC and STATUS1/FDEC pins can function the same as for<br>HW_SW_CTRL = 0.      Ire sampled only during POR.     Ivailable when DCO mode and GPIO pin control are enabled by registers.      Stive low).                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |