# WEBENCH® Clock Architect

Project Report

Project: 1198841/11 Project 11 - [LMX2581] Created: 11/10/16 8:14:34 PM

### **Block Diagram**

### **My Comments**

No comments

### System Specification and Parameters

| Fixed | Out | puts |

|-------|-----|------|

|-------|-----|------|

| Name   | Freq (MHz) | Format | Count |  |

|--------|------------|--------|-------|--|

| fixed0 | 144        | Any    | 1     |  |

| Options              |              |  |  |  |

|----------------------|--------------|--|--|--|

| Name                 | Design Value |  |  |  |

| Automatically Select | No           |  |  |  |

| Input Frequencies    |              |  |  |  |

### **Properties**

| Name             | Design Value         |

|------------------|----------------------|

| External Sources | none                 |

| Total BOM Cost   | \$7.0                |

| Total Current    | 198.0 mA             |

| Total Footprint  | 32.0 mm <sup>2</sup> |

User ID = 1198841 Design Id = 386 Device = LMX2581 Created = 11/10/16 8:14:34 PM

## WEBENCH <sup>®</sup> Clock Design Report

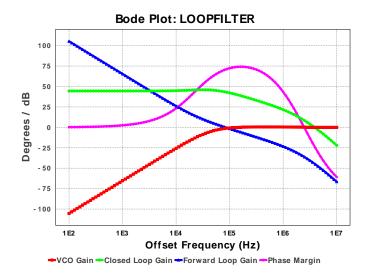

Loop Filter: LMX2581 LOOPFILTER

### **Preferences**

| Name                  | Design Value          |

|-----------------------|-----------------------|

| Filter Type           | Passive               |

| Filter Order          | 3rd Order             |

| Op Amp Gain           | 1.00                  |

| Charge Pump Gain      | 2.64 mA               |

| VCO Gain              | 30.00 MHz/V           |

| VCO Input Capacitance | 0.00 pF               |

| VCO Frequency         | 2016.00 MHz           |

| Phase Det. Frequency  | 12.00 MHz             |

| Filter type           | designed              |

| Brickwall Bandwidth   | 84.17697826086406 kHz |

| Delta Sigma Order     | 3                     |

| Randomization Factor  | 0.0 %                 |

| PLL Whole Part        | 168                   |

| PLL Numerator         | 0.0                   |

| PLL Denominator       | 1.0                   |

| Reference spurs       | enabled               |

| Fractional spurs      | enabled               |

| Subfractional spurs   | enabled               |

| Other spurs           | enabled               |

|                       |                       |

### **Parameters**

| Name           | Design Value | Forced | Actual Value |  |

|----------------|--------------|--------|--------------|--|

| Loop Bandwidth | 84.636 kHz   | N      | 84.177 kHz   |  |

| Phase Margin   | 70.00 deg    | N      | 70.843 deg   |  |

| T3/T1Ratio     | 50.00 %      | N      | 50.857 %     |  |

| T4/T3Ratio     | 0.00 %       | N      | 0.00 %       |  |

| Gamma          | 0.24         | N      | 0.265        |  |

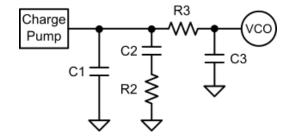

### **Loop Filter Components**

| Name | Target Value | Fixed | Forced |  |

|------|--------------|-------|--------|--|

| C1   | 0.039 nF     | N     | N      |  |

| C2   | 3.90 nF      | N     | N      |  |

| C3   | 0.004 nF     | N     | N      |  |

| C4   | Open         | N     | N      |  |

| R2   | 1.80 kohms   | N     | N      |  |

| R3   | 15.00 kohms  | N     | N      |  |

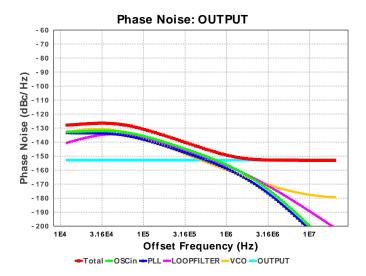

## Output Block: LMX2581 LMX2581: OUTPUT as SINEWAVE output, 144.0 MHz

### Integrated Noise Info 12000.0 Hz - 2.0E7 Hz

| Name               |           | Design Value    |

|--------------------|-----------|-----------------|

| Calculated Area    |           | 0.00            |

| Equivalent Flat N  | loise     | -147.871 dBc/Hz |

| RMS Jitter         |           | 282.371 fs      |

| RMS Phase Erro     | or (deg)  | 0.015 deg       |

| RMS Phase Erro     | or        | 0.255 mrad      |

| EVM                |           | 0.026%          |

| SNR                |           | 71.853 dB       |

| Spur               |           | -74.853 dBc     |

| Jitter (Pk-Pk)     |           | 2013.445 fs     |

| Jitter (Cycle to C | ycle Pk)  | 4026.891 fs     |

| Jitter (Cycle to C | ycle RMS) | 399.333 fs      |

| A/D ENOB           |           | 11.65 bits      |

| TIE (Time Interva  | al Error) | -0.286          |

| UI (Unit Interval) |           | 0.00            |

| Lower Integration  | n Limit   | 12.00 kHz       |

| Upper Integration  | n Limit   | 20.00 MHz       |

### Phase Noise Values (dBc/Hz)

| Offset    | Total   | OSCin   | PLL     | LOOPFILTER | VCO     | OUTPUT |  |

|-----------|---------|---------|---------|------------|---------|--------|--|

| 12 kHz    | -127.88 | -132.79 | -133.26 | -140.53    | -132.69 | -153   |  |

| 100 kHz   | -130.82 | -135.75 | -138.02 | -137.03    | -136.98 | -153   |  |

| 20000 kHz | -152.99 | -217.53 | -220.13 | -201.22    | -179.39 | -153   |  |

Texas Instruments' WEBENCH simulation tools attempt to recreate the performance of a substantially equivalent physical implementation of the design. Simulations are created using Texas Instruments' published specifications as well as the published specifications of other device manufacturers. While Texas Instruments does update this information periodically, this information may not be current at the time the simulation is built. Texas Instruments does not warrant the accuracy or completeness of the specifications or any information contained therein. Texas Instruments does not warrant that any designs or recommended parts will meet the specifications you entered, will be suitable for your application or fit for any particular purpose, or will operate as shown in the simulation in a physical implementation. Texas Instruments does not warrant that the designs are production worthy.

You should completely validate and test your design implementation to confirm the system functionality for your application prior to production.

Use of Texas Instruments' WEBENCH simulation tools is subject to Texas Instruments' Site Terms and Conditions of Use. Prototype boards based on WEBENCH created designs are provided AS IS without warranty of any kind for evaluation and testing purposes and are subject to the terms of the Evaluation License Agreement.