# **CC256x eHCILL Low Power Protocol**

### Contents

Introduction

Terms and Abbreviations

#### **Protocol Description**

HCILL Deep Sleep Commands List HCILL Deep Sleep Commands Description Enhanced HCILL Rules for Host Host Deep Sleep State Machine eHCILL Implementation Guidelines Wakeup ISR on CTS Sleep Procedure Wakeup by Baseband Controller Wakeup by Host Sleep and Wakeup Diagrams Wakeup by Baseband Controller Wakeup by Host Wakeup Collision 1 Wakeup Collision 2 Configuring eHCILL Enabling Deep Sleep **Alternative Implementations**

Host Cannot Wakeup from the CTS Signal Host Cannot Control the RTS Line

Baseband Controller Hardware Behavior Performing HCI\_Reset

# Introduction

The HCILL is a TI proprietary protocol, providing the baseband controller and the Bluetooth host with a deterministic way to independently go into respective sleep modes. In order to maintain the synchronization between the host and the Bluetooth (BT) device, it is important for each side to know when the other is going into sleep mode.

The enhanced HCILL (eHCILL) protocol includes several additions to the original HCILL specification that provide easier implementation on the host side and, at the same time, continuing to offer backward compatibility so that modifications are not required for a host that has implemented the original HCILL.

# **Terms and Abbreviations**

The table lists many of the terms and abbreviations used in this document.

Terms and Abbreviations

| Abbreviation<br>/Term  | Meaning / Explanation                                    |  |  |  |  |  |

|------------------------|----------------------------------------------------------|--|--|--|--|--|

| Baseband<br>Controller | TI Bluetooth single-chip solution                        |  |  |  |  |  |

| FW                     | Firmware                                                 |  |  |  |  |  |

| GPIO                   | General-purpose input / output                           |  |  |  |  |  |

| Host                   | The host processor that controls the baseband controller |  |  |  |  |  |

| HCI                    | Host controller interface                                |  |  |  |  |  |

| HCILL                  | Host controller interface, low level                     |  |  |  |  |  |

| eHCILL                 | Enhanced host controller interface, low level            |  |  |  |  |  |

| HW                     | Hardware                                                 |  |  |  |  |  |

| SW                     | Software                                                 |  |  |  |  |  |

# **Protocol Description**

# **HCILL Deep Sleep Commands List**

The table below lists HCILL commands related to deep sleep mode:

| List of HCILL Commands |        |  |  |  |  |  |

|------------------------|--------|--|--|--|--|--|

| HCILL Command          | Opcode |  |  |  |  |  |

| HCILL_GO_TO_SLEEP_IND  | 0x30   |  |  |  |  |  |

| HCILL_GO_TO_SLEEP_ACK  | 0x31   |  |  |  |  |  |

| HCILL_WAKE_UP_IND      | 0x32   |  |  |  |  |  |

| HCILL_WAKE_UP_ACK      | 0x33   |  |  |  |  |  |

## **HCILL Deep Sleep Commands Description**

HCILL\_GO\_TO\_SLEEP\_IND This command is sent by the baseband controller only (the host does not need to send it) to indicate that it is requesting to go into the Sleep state.

HCILL\_GO\_TO\_SLEEP\_ACK This command is sent by the host in response to a HCILL\_GO\_TO\_SLEEP\_IND command to indicate that both the host and baseband controller can go to a low-power mode.

HCILL\_WAKE\_UP\_IND This command is sent to wake up the sleeping party (host or controller).

HCILL\_WAKE\_UP\_ACK This message is a response to HCILL\_WAKE\_UP\_IND to acknowledge a state of being awake and ready to communicate.

## **Enhanced HCILL Rules for Host**

Situation: HCILL\_GO\_TO\_SLEEP\_IND received. Host should: Pull RTS high, enable wakeup from CTS, and send HCILL\_GO\_TO\_SLEEP\_ACK.

**Situation:** Wakeup from CTS. **Host should:** Disable CTS interrupt and release RTS.

Situation: HCILL\_WAKE\_UP\_IND received. Host should: Send HCILL\_WAKE\_UP\_ACK

**Situation:** HCILL\_WAKE\_UP\_IND sent and HCILL\_WAKE\_UP\_IND received. **Host should:** Go directly to AWAKE state without sending an ACK.

Situation: Host is in sleep state and has data or a command to send.

Host should: Disable wakeup from CTS, send HCILL\_WAKE\_UP\_IND, and lower RTS.

NOTE:If an HCI command is sent immediately before an HCILL\_SLEEP\_IND message is received, the host must complete the sleep preparation procedure (pull RTS high, enable wakeup from CTS, and send HCILL\_SLEEP\_ACK). The baseband controller then goes through the wakeup procedure to return the HCI\_Command\_Complete\_Event.

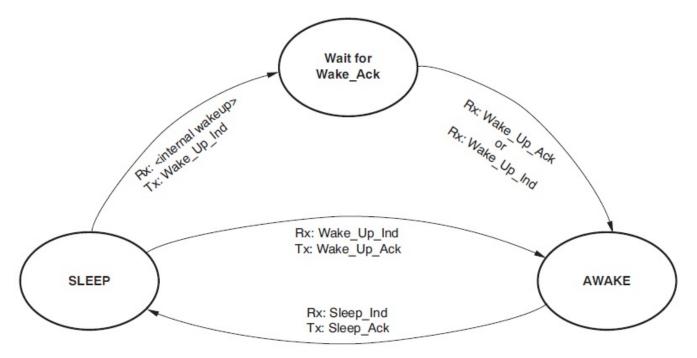

## Host Deep Sleep State Machine

The figure below shows the basic host state-machine diagram in the host Bluetooth deep-sleep implementation. As part of the eHCILL, the host is not required to send SLEEP\_IND (see the Inactivity TimeOut feature in Section 2.7 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Protocol#Configuring\_eHCILL), Configuring eHCILL) but can if desired. Also, the host is programmed to wake up from asserted CTS and assert RTS on going to sleep to prevent the baseband controller from sending data.

As below figure shows, the state-machine states are logical states; that is, a device can be in sleep state but not in actual low-power mode.

Deep-Sleep Basic State-Machine

## **eHCILL Implementation Guidelines**

The following summary is a general description of the sleep procedure, the wakeup procedure, and the CTS interrupt service routine (ISR) from a host perspective.

#### Wakeup ISR on CTS

- Inform the power manager system (if applicable) that Bluetooth is awake (for example, turn on the UART clock).

- Release RTS.

#### **Sleep Procedure**

- HCILL\_SLEEP\_IND is received from baseband controller (see the Inactivity TimeOut feature in <u>Section 2.7 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Prot</u> ocol#Configuring\_eHCILL), Configuring eHCILL).

- Enable the Wakeup CTS ISR.

- Pull RTS high.

- Reply with HCILL\_SLEEP\_ACK→change HCILL state to Sleep.

- Inform power manager system (if applicable) that Bluetooth is asleep (for example, the UART clock can be shut off).

#### Wakeup by Baseband Controller

- Wakeup ISR is executed because of CTS interrupt (see the RTS pulse width feature in <u>Section 2.7 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Protocol#Configuring\_eHCILL</u>).

- Disable the Wakeup CTS ISR.

- Release RTS.

- HCILL\_WAKEUP\_IND is received.

- Reply with HCILL\_WAKEUP\_ACK → change HCILL state to Awake (see the WAKEUP\_IND retransmission feature in Section 2.7 (http://processors.wiki.ti.com/index.php/CC256x\_eHCI\_LL\_Low\_Power\_Protocol#Configuring\_eHCILL), Configuring eHCILL).

#### Wakeup by Host

- Disable Wakeup ISR.

- Turn UART on (if turned off).

- Release RTS.

- Send HCILL\_WAKEUP\_IND.

- Wait for HCILL\_WAKEUP\_ACK (or HCILL\_WAKEUP\_IND in case of a collision type 1; see Section 2.6.3 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Protoc ol#Wakeup\_Collision 1, and Section 2.6.4 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Protocol#Wakeup\_Collision\_2), Wakeup Collision 2) → change HCILL state to Awake.

## **Sleep and Wakeup Diagrams**

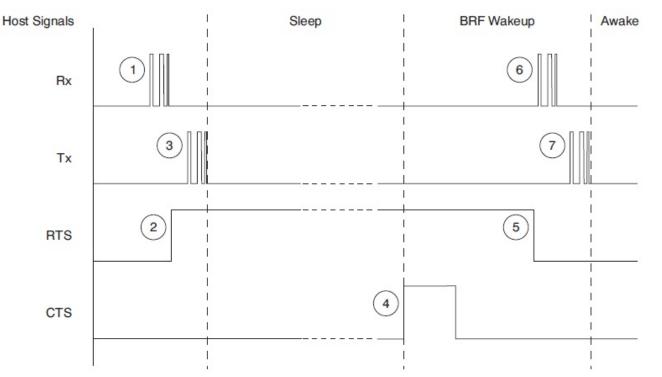

#### Wakeup by Baseband Controller

The figure below shows the process of the baseband controller waking up the device.

Wake-Up by Baseband Controller

1) HCILL\_SLEEP\_IND received from baseband controller.

2) Host pulls RTS high and enables wake-up from CTS. Pulling RTS is so the baseband controller can send the HCILL\_WAKEUP\_IND to the host only when the host is awake and ready for it.

3) Host sends HCILL\_SLEEP\_ACK.

4) Baseband controller wakes up host by asserting CTS for 150µs (recommended pulse width).

5) Host wakes up and lowers its RTS so the baseband controller can send the HCILL\_WAKEUP\_IND.

6) HCILL\_WAKEUP\_IND received from baseband controller once RTS is low.

7) Host sends HCILL\_WAKEUP\_ACK.

NOTE: If the host cannot control the RTS level, the RTS pin functionality might need to be changed to GPIO and asserted/deasserted as needed. When the device is awake, the pin functionality might need to be changed back to RTS.

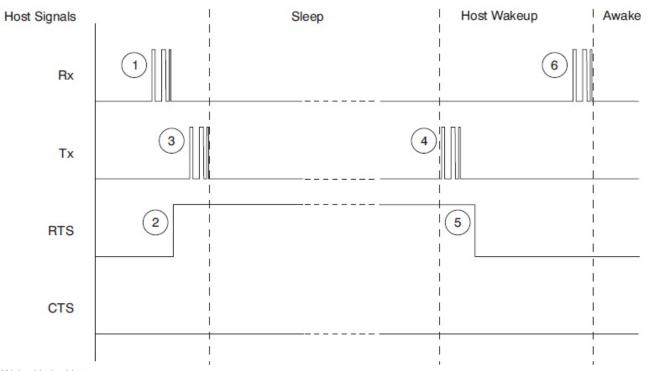

#### Wakeup by Host

The figure below shows the procedure for the host to wake up the device.

Wake-Up by Host

1) HCILL\_SLEEP\_IND is received from baseband controller.

2) Host pulls RTS high and enables wake-up from CTS so that the baseband controller can send HCILL\_WAKEUP\_IND to the host only when the host is awake and ready.

3) Host sends HCILL\_SLEEP\_ACK.

4) Host wakes up the baseband controller by sending a HCILL\_WAKEUP\_IND message.

5) Host lowers RTS so that the baseband controller can reply with HCILL\_WAKEUP\_ACK.

6) Host receives HCILL\_WAKEUP\_ACK once the baseband controller physically wakes up.

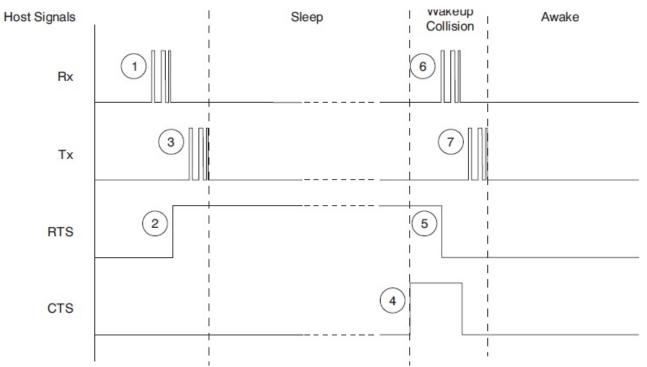

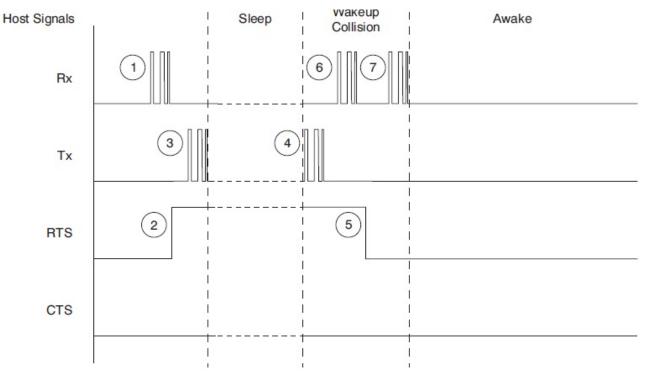

#### Wakeup Collision 1

The figure below shows the process of a wakeup collision type 1.

CC256x eHCILL Low Power Protocol - Texas Instruments Wiki

Wake-Up Collision Type 1

1) HCILL\_SLEEP\_IND is received from baseband controller.

2) Host pulls RTS high and enables wake-up from CTS so that the baseband controller can send HCILL\_WAKEUP\_IND to the host only when the host is awake and ready.

3) Host sends HCILL\_SLEEP\_ACK.

4) Baseband controller wakes up host by asserting CTS for 150 µs.

5) Host lowers RTS so that the baseband controller can reply with HCILL\_WAKEUP\_ACK (it is not aware this is a collision).

6) HCILL\_WAKEUP\_IND is received from the baseband controller (once RTS is low).

7) Host wakes up the baseband controller by sending a HCILL\_WAKEUP\_IND (delayed until CTS is low).

NOTE: If the host sends an HCILL\_WAKEUP\_IND, the host should consider reception of an HCILL\_WAKEUP\_IND as an HCILL\_WAKEUP\_ACK and go directly to the Wakeup state. Sending an HCILL\_WAKEUP\_ACK to the baseband controller in this case does not harm its state-machine.

#### Wakeup Collision 2

The figure below shows the process of a wakeup collision type 2.

Wake-Up Collision Type 2

1) HCILL\_SLEEP\_IND is received from baseband controller.

2) Host pulls RTS high and enables wake-up from CTS so the baseband controller can send the HCILL\_WAKEUP\_IND to the host only when the host is awake and ready.

3) Host sends HCILL\_SLEEP\_ACK.

4) Host wakes up the baseband controller by sending a HCILL\_WAKEUP\_IND message.

5) Host lowers RTS so that the baseband controller can reply with HCILL\_WAKEUP\_ACK.

6) HCILL\_SLEEP\_IND is received from the baseband controller. This command has been in the queue and must be ignored by the host (sent until RTS goes low; it is not aware of a collision).

7) Host must wait to receive HCILL\_WAKEUP\_ACK (acknowledge to Step 4) to wake up.

## **Configuring eHCILL**

As part of the eHCILL, the following three features must be configured: Inactivity timeout, WAKEUP\_IND retransmission, and RTS pulse width.

Inactivity timeout is a timer implemented in the baseband controller that determines when to send the HCILL\_SLEEP\_IND. If there is no activity on the UART line, the baseband controller is assumed to allow the host to go to sleep. This time is separate from the actual power mode the baseband controller can enter because, in some cases, the host can enter

a low-power mode even though the baseband controller cannot (an active voice call, for example).

- WAKEUP\_IND retransmission specifies the interval time to retransmit the WAKEUP\_IND message until acknowledged (until WAKEUP\_ACK is received successfully at baseband controller) to increase protocol robustness. This feature can also be used on hosts that do not support a wakeup interrupt on the CTS line (see Section 3.1 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Protocol#Host\_Cannot\_Wakeup\_from\_the\_CTS\_Signal), Host Cannot Wakeup from the CTS Signal). In this case, the UART RX is routed to an internal interruptible GPIO. The first WAKEUP\_IND message is used for the wakeup interrupt and the second WAKEUP\_IND is accepted as a WAKEUP byte on the host UART RX.

- RTS pulse width sets the minimum pulse width of the baseband RTS that is followed by a WAKEUP\_IND message. The minimum pulse width should be set to 150 µs in case high baud rates require waking up some HLOS platforms.

The following command sets up eHCILL(for more information, see the HCI Vendor-Specific Commands documentSection 2.2.21 (http://processors.wiki.ti.com/index.php/CC256x\_VS\_HCI\_Com mands#HCI\_VS\_HCILL\_Parameters\_.280xFD2B.29)):

$HCI\_VS\_HCILL\_Parameters(Inactivity\_Timeout, WakeUp\_Ind\_Retransmission\_TimeOut, RTS\_pulse\_width)$

where:

- Inactivity\_TimeOut is in Bluetooth frame units (1.25 ms); that is, an Inactivity\_TimeOut value of 80 sets a timeout of 100 ms (80 × 1.25 ms). Default value is 100 ms.

- WakeUp\_Ind\_Retransmission\_TimeOut is the timeout, in Bluetooth frame units (1.25 ms), for resending WAKEUP\_IND if no acknowledgement is received. A value of 0 means no retransmission. Default value is 500 ms (400 × 1.25 ms).

- RTS\_pulse\_width sets the minimum pulse width of RTS (μs). A 0 value disables the pulse. Default value is 1 μs; however, 150 μs should be used.

## **Enabling Deep Sleep**

Deep-sleep operation is disabled by default at power up. To enable the baseband controller deep-sleep feature and activate the eHCILL protocol, the host must send the HCI\_VS\_Sleep\_Mode\_Configurations command first(for more information, see the HCI Vendor-SpecificCommands document Section 2.2.22 (http://processors.wiki.ti.com/index.php/CC256x\_VS\_HCI\_Commands#HCI\_VS\_Sleep\_Mode\_Configurations\_.280xFDoC.29)).

- HCI\_VS\_Sleep\_Mode\_Configurations 0xFD0C, 1, Deep\_Sleep\_Enable, Deep\_Sleep\_Mode, 0xFF, 0xFF, 0xFF, 0xFF, 100

- Deep\_Sleep\_Enable = 0 (disable), 1 (enable).

- Default = 0 (disable).

- Deep\_Sleep\_Mode = 0 (HCILL),...,0xFF (Don't change).

- Default = 0 (HCILL).

For the current deep-sleep status, send HCI\_VS\_Get\_System\_Status oxFE1F, oxFE1F(for more information, see the HCI Vendor-SpecificCommands documentSection 2.2.23 (http://processors. wiki.ti.com/index.php/CC256x\_VS\_HCI\_Commands#HCI\_VS\_Get\_System\_Status\_.280xFE1F.29)).

# **Alternative Implementations**

Previous sections describe the recommended way to implement the eHCILL mechanism on the host. This section provides more implementation options that can be used when it is difficult to use the host RTS and CTS for purposes other than flow control.

# Host Cannot Wakeup from the CTS Signal

There are three possibilities in this case, from a host perspective:

1) Normally, each UART line can be multiplexed with a GPIO line. Thus, instead of using the CTS input pin as CTS, first change its functionality to be GPIO (interruptible). Then, apply the wake-up ISR previously described for CTS to this new GPIO. In some cases, the hardware flow control might need to be disabled first.

2) At hardware design time, connect the host CTS signal to a separate GPIO and apply the wake up ISR described previously for CTS to this new GPIO.

3) If the CTS cannot be controlled, the UART RX can be routed to an internal interruptible GPIO. In this case, the first WAKEUP\_IND message is used for the wakeup interrupt and the second WAKEUP\_IND is accepted as a WAKEUP byte on the host UART RX. WAKEUP\_IND retransmission value in HCI\_VS\_HCILL\_Parameters command must be configured accordingly (see Section 2.7 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Po wer\_Protocol#Configuring\_eHCILL), Configuring eHCILL).

### Host Cannot Control the RTS Line

There are two possibilities in this case:

1) Normally, each UART line can be multiplexed with a GPIO line. Thus, instead of controlling the RTS output pin as RTS, first change its functionality to be GPIO. Asserting or de-asserting a GPIO should not be a problem. In some cases, the hardware flow control might need to be disabled first.

2) The purpose of asserting the host RTS line during sleep mode is so the host can wake up from a HCILL\_WAKEUP\_IND byte only if awake and ready. If the RTS is not asserted (during sleep mode) and baseband controller must wake up, it sends the HCILL\_WAKEUP\_IND immediately after sending a CTS wakeup pulse whether the host is ready or not. In this case, the host must respond with a HCILL\_WAKEUP\_ACK as a result of the CTS wake-up indication regardless whether the HCILL\_WAKEUP\_IND is received or not. Recall that the baseband controller may keep sending HCILL\_WAKEUP\_IND messages until acknowledged(see Section 2.7 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Protocol#Configuring\_eHCILL), Configuring eHCILL).

# **Baseband Controller Hardware Behavior**

The baseband controller hardware behaves according to these parameters:

- The baseband controller wakes up on a falling edge of the RX\_HCI signal.

- The first byte received while in deep sleep (HCI\_WAKE\_UP\_IND) wakes up the device but is discarded because reception is usually corrupted (first few bits are lost).

- To allow the host to send the HCI\_WAKE\_UP\_IND byte, RTS is always low while in deep-sleep mode(enabling data reception).

# **Performing HCI\_Reset**

The power management protocol relies on both the baseband controller and the host being aware of the counterpart state. Breaking this synchronization can cause the baseband controller to seem inaccessible to the host. During normal operation, power management sequencing performs smoothly if the rules discussed here are followed.

However, to ensure that power management operation continues to run after an HCI\_Reset, the host must implement the following steps as the reset procedure:

Step 1. Disable Deep-Sleep mode (see Section 2.8 (http://processors.wiki.ti.com/index.php/CC256x\_eHCILL\_Low\_Power\_Protocol#Enabling\_Deep\_Sleep) Enabling Deep Sleep).

Step 2. Wait for Command Complete event.

Step 3. Send HCI\_Reset.

Step 4. Wait for Command Complete event (and wait for CTS indication that baseband controller is active again).

| <ul> <li>{{</li> <li>1. switchcategory:MultiCore=</li> <li>For technical support on<br/>MultiCore devices, please<br/>post your questions in the<br/><u>C6000 MultiCore Forum</u></li> <li>For questions related to<br/>the BIOS MultiCore SDK<br/>(MCSDK), please use the<br/><u>BIOS Forum</u></li> <li>Please post only comments related<br/>to the article CC256x eHCILL Low</li> <li>Power Protocol here.</li> </ul> | <ul> <li>questions in the<br/><u>C6000 MultiCore</u><br/><u>Forum</u></li> <li>For questions<br/>related to the<br/>BIOS MultiCore<br/>SDK (MCSDK),<br/>please use the<br/><u>BIOS Forum</u></li> <li><sup>1</sup> Please post on</li> </ul> | please<br>post your<br>questions<br>on The<br>C2000<br>Forum.<br>Please<br>post only<br>comments<br>about the<br>article<br>y CC256x<br>e eHCILL<br>Low<br>Power | DaVinci=For<br>technical<br>support on<br>DaVincoplease<br>post your<br>questions on<br>The DaVinci<br>Forum. Please<br>post only<br>comments<br>about the<br>article CC256x<br>eHCILL Low<br>Power<br>Protocol here. | MSP430<br>please post<br>your<br>questions on<br>The MSP430<br>Forum.<br>Please post<br>only<br>comments<br>about the<br>article<br>CC256x<br>eHCILL Low | OMAP35x=For<br>technical<br>support on<br>OMAP please<br>post your<br>questions on<br>The OMAP<br>Forum. Please<br>post only<br>comments<br>about the<br>article CC256x<br>eHCILL Low | OMAPL1=For<br>technical<br>support on<br>OMAP please<br>post your<br>questions on<br>The OMAP<br>Forum.<br>Please post<br>only<br>comments<br>about the<br>article<br>CC256x<br>eHCILL Low<br>Power<br>Protocol<br>here. | MAVRK=For<br>technical<br>support on<br>MAVRK<br>please post<br>your<br>questions<br>on The<br>MAVRK<br>Toolbox<br>Forum.<br>Please post<br>only<br>comments<br>about the<br>article<br>CC256x<br>eHCILL<br>Low Power<br>Protocol<br>here. | For technical support<br>please post your<br>questions at<br>http://e2e.ti.com.<br>Please post only<br>comments about the<br>article CC256x<br>eHCILL Low Power<br>Protocol here.<br>}} |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Links                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                              |                                                                                                                                                                  |                                                                                                                                                                                                                       |                                                                                                                                                          |                                                                                                                                                                                       |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                            |                                                                                                                                                                                         |  |

| Amplifiers & Lin<br>Audio<br>Broadband RF/I<br>Clocks & Timers<br>Data Converters                                                                                                                                                                                                                                                                                                                                         | High-Re<br>F & Digital Radio Interface                                                                                                                                                                                                       | liability                                                                                                                                                        | <ul> <li>Microco</li> </ul>                                                                                                                                                                                           | rocessors<br>Signal Process<br>ontrollers (MCL<br>Applications P                                                                                         | Sors (DSP)                                                                                                                                                                            | ches & Multiplexe<br>perature Sensors<br>less Connectivity                                                                                                                                                               | & Control ICs                                                                                                                                                                                                                              |                                                                                                                                                                                         |  |

Retrieved from "https://processors.wiki.ti.com/index.php?title=CC256x\_eHCILL\_Low\_Power\_Protocol&oldid=165952"

This page was last edited on 10 December 2013, at 02:30.

Content is available under Creative Commons Attribution-ShareAlike unless otherwise noted.