## (1) Current at the time of reset (typ)

8.5 Power Consumption - Power Modes When measured on the CC26x2REM-7ID-Q1 reference design with  $T_c$  = 25 °C,  $V_{DDS}$  = 3.0 V with DC/DC enabled unless otherwise noted.

| PARAMETER         |                                    | TEST CONDITIONS                                                       | TYP  | UNIT |  |

|-------------------|------------------------------------|-----------------------------------------------------------------------|------|------|--|

| Core Currer       | nt Consumption                     |                                                                       | •    |      |  |

|                   | Reset and Shutdown                 | Reset. RESET_N pin asserted or VDDS below power-on-reset threshold    | 150  | nA   |  |

| I <sub>core</sub> | Reset and Shutdown                 | Shutdown. No clocks running, no retention                             | 150  |      |  |

|                   | Standby<br>without cache retention | RTC running, CPU, 80KB RAM and (partial) register retention. RCOSC_LF | 0.94 | μA   |  |

|                   |                                    | RTC running, CPU, 80KB RAM and (partial) register retention XOSC_LF   | 1.09 | μA   |  |

|                   | Standby<br>with cache retention    | RTC running, CPU, 80KB RAM and (partial) register retention. RCOSC_LF | 3.2  | μA   |  |

|                   |                                    | RTC running, CPU, 80KB RAM and (partial) register retention. XOSC_LF  | 3.3  | μA   |  |

|                   | Idle                               | Supply Systems and RAM powered RCOSC_HF                               | 675  | μA   |  |

|                   | Active                             | MCU running CoreMark at 48 MHz<br>RCOSC HF                            | 3.39 | mA   |  |

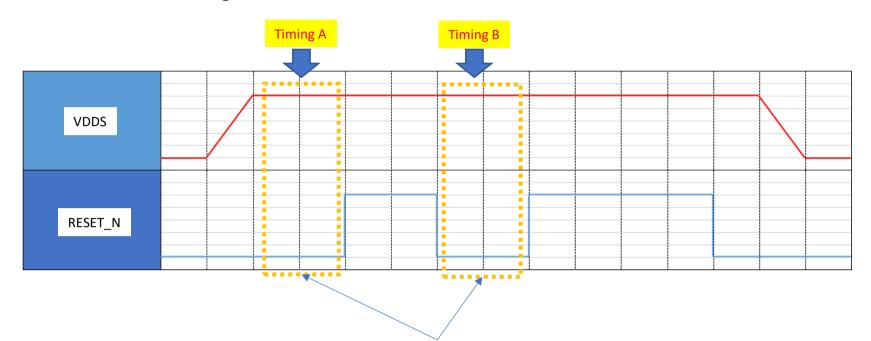

## (2) Difference in current at RESET timing

In some samples, Timing A has 0.1 mA more current at low RESET\_N than Timing B. However, in most samples, there is no difference in timing. What's the difference?

## Leakage Current when RESET\_N is Low

|          | Most Samples  | Some samples |  |  |

|----------|---------------|--------------|--|--|

|          | (518/520 pcs) | (2/520 pcs)  |  |  |

| Timing A | 330nA         | 0.103mA      |  |  |

| Timing B | 330nA         | 330nA        |  |  |

|          |               |              |  |  |