## **DRV632 SPICE Model**

Paul C. Chen

Nov 2011

Audio Application

Dallas TX USA

#### **TINA SPICE Model**

- The following parameters are being modeled: Ao, f-3dB, Slew Rate, Max/Min voltage/Current, noise, input voltage offset, current consumption, Under voltage protection with hysteresis, Mute.

- The following parameters are not being modeled: PSRR and CMRR

- Charge pump is being modeled using ideal Voltage controlled voltage source

# **TINA SPICE Simulation (typical)**

## **TINA SPICE Simulation (typical)**

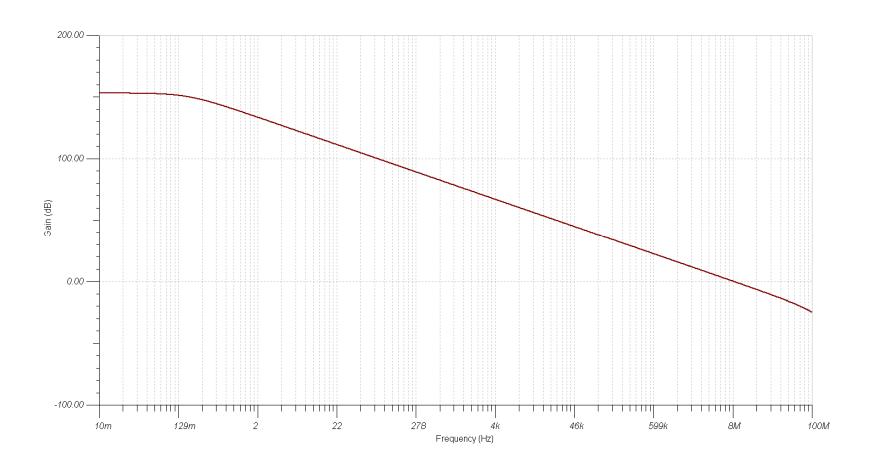

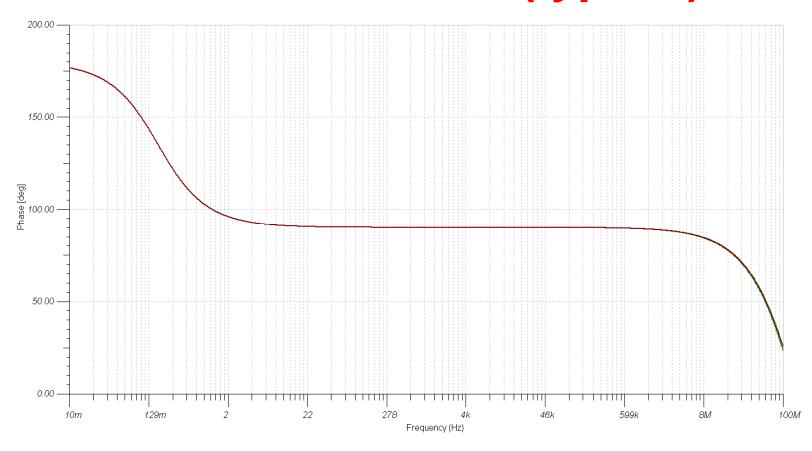

DC gain is 155 dB, bandwidth is 8MHz and Phase margin is 80 degree .

## **Design Database Simulation (typical)**

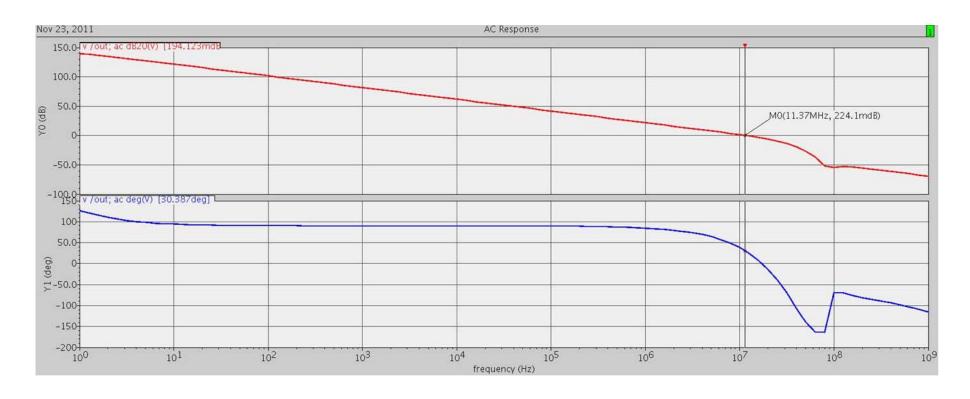

DC gain is 140 dB, Bandwidth is 11MHz and Phase margin is about 30 degree.