# How to Dump CFG / Header File

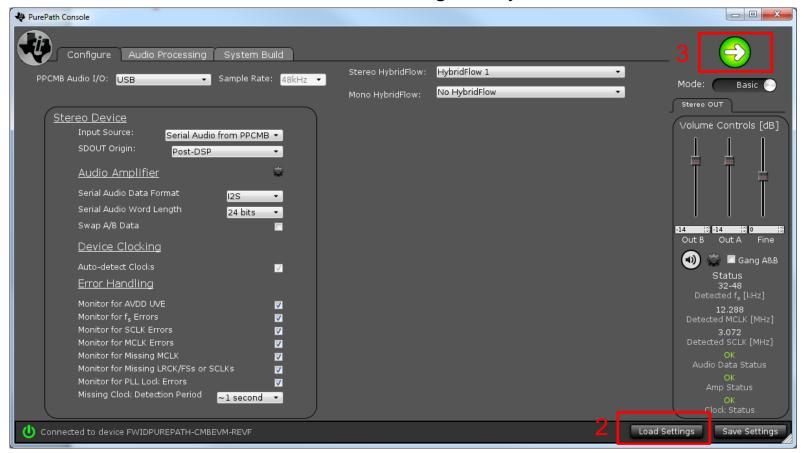

- 1. Make sure PPCMB is connected to PC.

- 2. Load your xml file into PPC2.

- 3. Click download button to start running the hybrid flow.

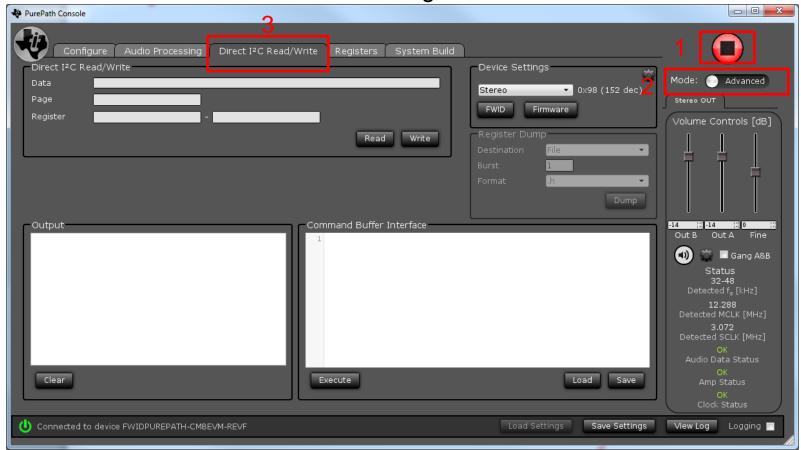

- 1. Stop the hybrid flow from running.

- 2. Switch to Advanced mode.

- 3. Choose "Direct I2C Read / Wrte" Page.

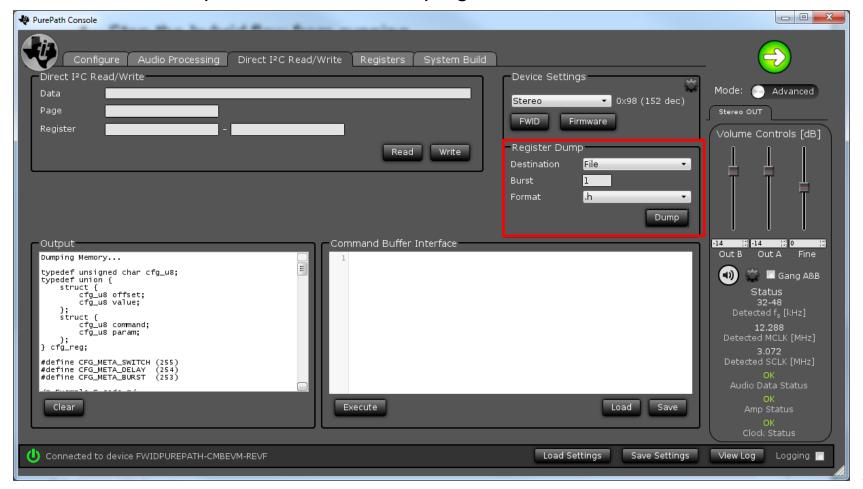

- 1. Select the right destination, burst length and format in the Register Dump.

- 2. Click the dump button to start dumping.

1. Fix the P0-R42 value if it is set to 0x00.

```

🔚 hf1-burst1_fix.h 🔣

64 w 98 19 00

100

65 w 98 1a 80

66 w 98 1b 00

102

w 98 1c 00

103

w 98 1d 00

104

0xf3

w 98 1e 00

105

0x04

w 98 1f

04

106

107

w 98 20

0.0

Ananlog Mute */

w 98 21

0x2a, 0x00 \},

00

109

w 98 22 00

0x2a, 0x11 },

w 98 23

110

01

0x2b, 0x1f

w 98 24

00

111

0x2c, 0x00

112

w 98 25

0.0

0x2d, 0x00 \},

w 98 26 f3

113

0x2e, 0x00

w 98 27 04

114

0x00

w 98 28 02

115

80 w 98 29 00

116

#w 98 2a 00

#Anglog Mute

117

w 98 2a 11

118

w 98 2b 1f

119

w 98 2c 00

120

98 2d 00

121

98 2e 00

122

w 98 2f 00

123

0x00

```

## P0-R3 and P0-R42(0x2a)

#### 8.4.2.3 PO-R3

| Mute Channel B [4] (R/W)                                                                                                  | 00000000 |

|---------------------------------------------------------------------------------------------------------------------------|----------|

| This bit issues soft mute request for the Channel B. The volume will be smoothly ramped down/up to avoid pop/click noise. |          |

| Normal volume                                                                                                             | 0        |

| Mute                                                                                                                      | 1        |

| Mute Channel A [0] (R/W)                                                                                                  | 0000000  |

| This bit issues soft mute request for the Channel A. The volume will be smoothly ramped down/up to avoid pop/click noise. |          |

| Normal volume                                                                                                             | 0        |

| Mute                                                                                                                      | 1        |

#### 8.4.2.29 P0-R42

| Channel B DAC Data Path [5:4] (R/W)                          | 0000001  |

|--------------------------------------------------------------|----------|

| These bits control the Channel B audio data path connection. |          |

| Zero data (mute)                                             | 00       |

| Channel B data                                               | 01       |

| Channel A data                                               | 10       |

| Reserved (do not set)                                        | 11       |

| Channel A DAC Data Path [1:0] (R/W)                          | 00000001 |

| These bits control the Channel A audio data path connection. |          |

| Zero data (mute)                                             | 00       |

| Channel A data                                               | 01       |

| Channel B data                                               | 10       |

| Reserved (do not set)                                        | 11       |