# **TAS5805M Trouble Shooting (Draft)**

Alix Wan Jan, 2019

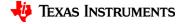

## Hardware checking

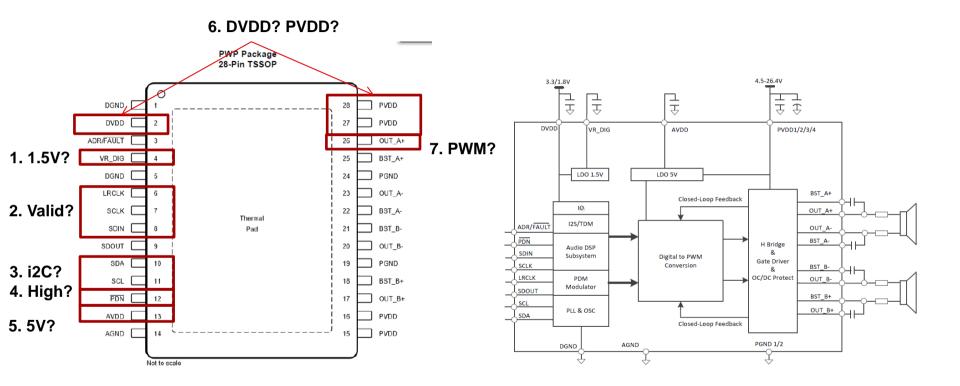

### Software debug

### **Global fault and status of TAS5805**

#### 9.6.1.36 CHAN FAULT Register (Offset = 70h) [reset = 0x00]

CHAN\_FAULT is shown in Figure 134 and described in Table 42.

Return to Summary Table.

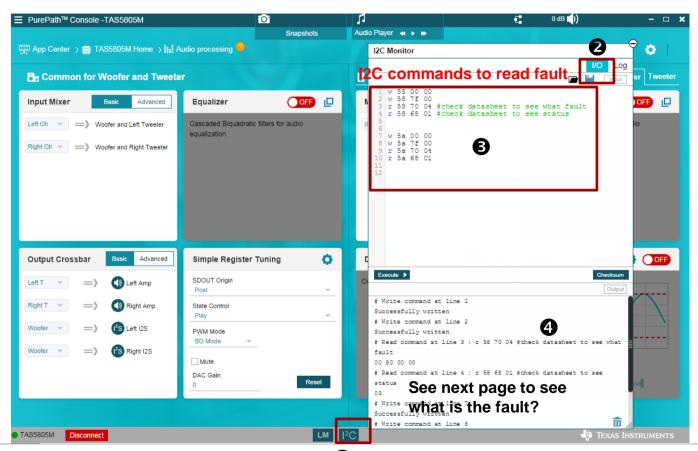

#### Figure 134. CHAN\_FAULT Register

#### Table 42. CHAN\_FAULT Register Field Descriptions

| Bit | Bit Field Type Reset |                                  | Reset | Description                      |

|-----|----------------------|----------------------------------|-------|----------------------------------|

| 7-4 | RESERVED             | R                                | 0000  | This bit is reserved             |

| 3   | CH1_DC_1             | R                                | 0     | Left channel DC fault            |

| 2   | CH2_DC_1             | _DC_1 R 0 Right channel DC fault |       | Right channel DC fault           |

| 1   | CH1_OC_I             | R                                | 0     | Left channel over current fault  |

| 0   | CH2_OC_I             | R                                | 0     | Right channel over current fault |

#### 9.6.1.38 GLOBAL FAULT2 Register (Offset = 72h) [reset = 0h]

GLOBAL\_FAULT2 is shown in Figure 136 and described in Table 44.

Return to Summary Table.

#### Figure 136. GLOBAL FAULT2 Register

| 7        | 6 | 5 | 4 | 3 | 2    | 1    | 0      |

|----------|---|---|---|---|------|------|--------|

| RESERVED |   |   |   |   | RESE | RVED | OTSD_I |

|          | R |   |   |   | F    | 1    | R      |

#### Table 44. GLOBAL FAULT2 Register Field Descriptions

| Bit | Bit Field |   | Reset   | Description                      |

|-----|-----------|---|---------|----------------------------------|

| 7-1 | RESERVED  | R | 0000000 | This bit is reserved             |

| 0   | OTSD_I    | R | 0       | Over temperature shut down fault |

#### 9.6.1.37 GLOBAL FAULT1 Register (Offset = 71h) [reset = 0h]

GLOBAL\_FAULT1 is shown in Figure 135 and described in Table 43.

Return to Summary Table.

#### Figure 135. GLOBAL\_FAULT1 Register

| 7                 | 6               | 5 | 4 | 3 | 2           | 1         | 0         |

|-------------------|-----------------|---|---|---|-------------|-----------|-----------|

| OTP_CRC_ER<br>ROR | BQ_WR_ERRO<br>R |   |   |   | CLK_FAULT_I | PVDD_OV_I | PVDD_UV_I |

| R                 | R               |   |   |   | R           | R         | R         |

#### Table 43. GLOBAL\_FAULT1 Register Field Descriptions

| Bit | Bit Field Type Rese |                  | Reset | Description                     |

|-----|---------------------|------------------|-------|---------------------------------|

| 7   | OTP_CRC_ERROR       | P_CRC_ERROR R 0h |       | Indicate OTP CRC check error.   |

| 6   | BQ_WR_ERROR         | R                | 0h    | The recent BQ is written failed |

| 5-3 | RESERVED            | R                | 0h    | This bit is reserved            |

| 2   | CLK_FAULT_I         | R                | 0h    | Clock fault                     |

| 1   | PVDD_OV_I           | R                | 0h    | PVDD OV fault                   |

| 0   | PVDD_UV_I           | R                | 0h    | PVDD UV fault                   |

#### 9.6.1.39 OT WARNING Register (Offset = 73h) [reset = 0x00]

OT\_WARNING is shown in Figure 137 and described in Table 45.

Return to Summary Table.

#### Figure 137. OT\_WARNING Register

| 7 6      |   | 5        | 4 | 3 | 2   | 1        | 0 |  |

|----------|---|----------|---|---|-----|----------|---|--|

| RESERVED |   | RESERVED |   |   | OTW | RESERVED |   |  |

| F        | 3 |          | R | R | R   | R        | R |  |

#### Table 45. OT\_WARNING Register Field Descriptions

| ı | Bit Field |          | Type | Reset | Description                    |

|---|-----------|----------|------|-------|--------------------------------|

| 1 | 7-6       | RESERVED | R    | 00    | This bit is reserved           |

| ı | 5-3       | RESERVED | R    | 000   | This bit is reserved           |

| İ | 2         | OTW      | R    | 0     | Over temperature warning ,135C |

| ı | 1-0       | RESERVED | R    | 00    | This bit is reserved           |

#### 9.6.1.28 POWER\_STATE Register (Offset = 68h) [reset = 0x00]

POWER STATE is shown in Figure 126 and described in Table 34.

Return to Summary Table.

#### Figure 126. POWER STATE Register

#### Table 34. POWER\_STATE Register Field Descriptions

|   | Bit | Field     | Туре | Reset    | Description      | 1 |  |

|---|-----|-----------|------|----------|------------------|---|--|

| _ | 7-0 | STATE_RPT | R    | 00000000 | 0: Deep sleep    | 1 |  |

|   |     |           |      |          | 1: Sleep         |   |  |

|   |     |           |      |          | 2: HIZ           | ı |  |

|   |     |           |      |          | 3: Play          | ı |  |

|   |     |           |      |          | Others: reserved | П |  |

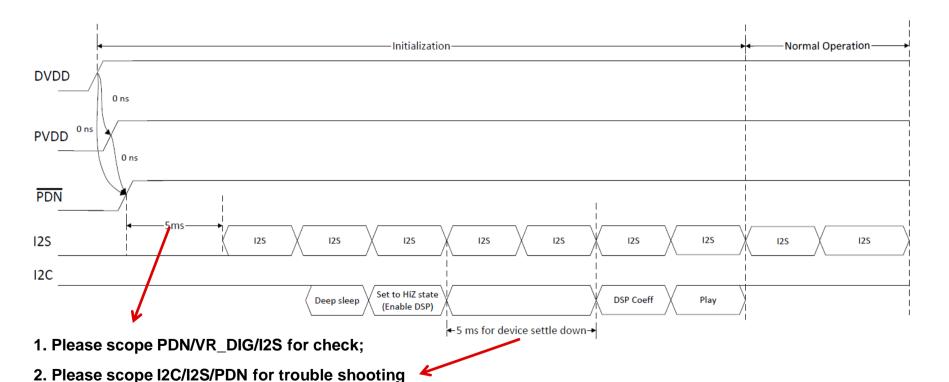

# Power on sequence check

# Further trouble shooting

- After you finish steps above, if anything is wrong, please debug;

- If everything above is ok, please email to me.