|                      |                     |    |     |     |         |       |        | F   | REVISI | ONS      |         |          |       |         |                |      |       |         |           |            |

|----------------------|---------------------|----|-----|-----|---------|-------|--------|-----|--------|----------|---------|----------|-------|---------|----------------|------|-------|---------|-----------|------------|

| LTR                  |                     |    |     |     | [       | DESCR |        | N   |        |          |         |          | DA    | ATE (YI | R-MO-I         | DA)  |       | APPF    | ROVED     |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       | lan - J | 2276      |            |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       | 분장      | <u>58</u> | ₩<br>¥¥    |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       | 迸       | ŚĘ)       | Σ.         |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       | 四       | 2Ý        | <u>s</u> , |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         | -0-0      | Ret.       |

|                      |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

| REV                  |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

| SHEET                |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

| REV                  |                     |    |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

| SHEET                | 15                  | 16 | 17  | 18  | 19      | 20    | 21     | 22  | 23     | 24       | 25      | 26       | 27    | 28      | 29             | 30   | 31    | 32      |           |            |

| REV STATUS           |                     | 1  |     | RE\ | /       | 1     |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

| OF SHEETS            |                     |    |     | SHE | ET      |       | 1      | 2   | 3      | 4        | 5       | 6        | 7     | 8       | 9              | 10   | 11    | 12      | 13        | 14         |

| PMIC N/A             |                     |    |     |     | PARED   |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     | RIC | K OFF   | ICER  |        |     |        |          |         |          | DLA   |         |                |      |       |         |           |            |

| STA                  | NDAF                | RD |     | CHF | CKED    | BY    |        |     |        | 1        |         |          | OLUN  |         |                |      |       |         |           |            |

| MICRO                |                     |    |     |     | JESH F  |       | AIG    |     |        |          |         | nttps    | ://ww | w.dia   | <u>a.mii/i</u> | anda | nama  | iritim  | <u>ə</u>  |            |

| DR                   | AWIN                | G  |     |     |         |       |        |     |        |          |         |          |       |         |                |      |       |         |           |            |

|                      |                     |    |     |     |         |       |        | _   |        |          |         |          |       |         |                |      |       |         |           |            |

| THIS DRAWII<br>FOR U | NG IS A<br>ISE BY . |    | BLE | JAN | /IES R. | ESCH  | MEYE   | K   |        |          |         |          |       |         |                |      |       |         | , 12 I    | BIT,       |

| DEPA<br>AND AGEI     |                     |    | =   | DRA | WING    | APPRO | OVAL D | ATE |        |          |         | G TO     |       |         |                | VER  | IER,  |         |           |            |

| DEPARTMEI            |                     |    |     |     |         |       | 8-12   |     |        |          | INUL    | ITHIC    | , SIL |         | 1              |      |       |         |           |            |

|                      |                     |    |     | PEV | ISION   |       |        |     |        | C1       | ZE      | <u> </u> | GE CC |         |                |      |       |         |           |            |

| AM                   | ISC N/A             |    |     | REV | 131011  |       |        |     |        |          | 2E<br>A |          | 67268 |         |                | ŧ    | 5962· | -1220   | 5         |            |

|                      |                     |    |     |     |         |       |        |     |        | <u> </u> |         | SHEET    |       |         | OF :           | 32   |       |         |           |            |

| DSCC FORM            |                     |    |     |     |         |       |        |     |        | l        |         |          |       |         | 2. \           |      |       |         |           |            |

### 1. SCOPE

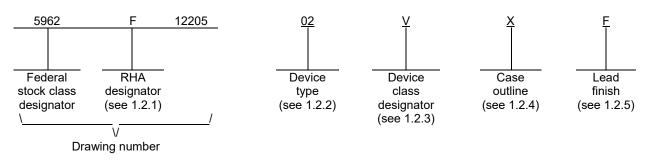

1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device class Q) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels is reflected in the PIN.

1.2 <u>PIN</u>. The PIN is as shown in the following example:

1.2.1 <u>RHA designator</u>. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | <u>Generic number</u> | Circuit function                        |

|-------------|-----------------------|-----------------------------------------|

| 01          | ADC12D1600            | CMOS 12 bit analog to digital converter |

| 02          | ADC12D1620            | CMOS 12 bit analog to digital converter |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class     |                                | Device ree                      | quirements documentation         |

|------------------|--------------------------------|---------------------------------|----------------------------------|

| Q or V           |                                | Certification and               | qualification to MIL-PRF-38535   |

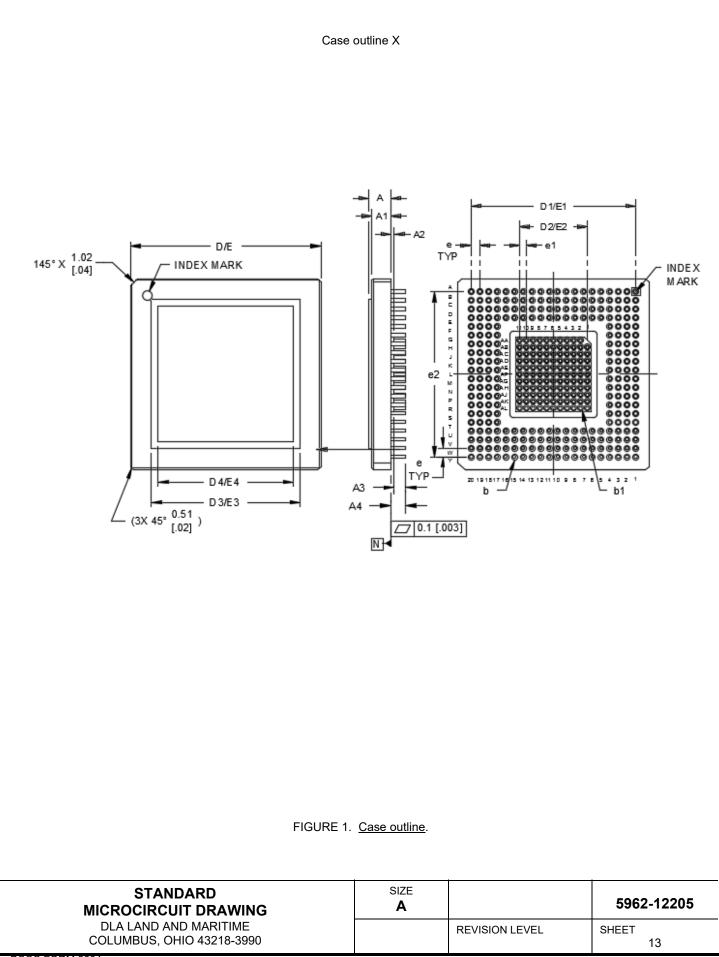

| Case outline(s). | The case outline(s) are as de  | esignated in MIL-S <sup>-</sup> | TD-1835 and as follows:          |

| Outline letter   | Descriptive designator         | <u>Terminals</u>                | Package style                    |

| Х                | See figure 1                   | 376                             | Ceramic column grid array (CCGA) |

| Lead finish. The | lead finish is as specified in | MIL-PRF-38535 for               | device classes Q and V.          |

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                | 5962-12205 |

|----------------------------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL | SHEET 2    |

1.2.4

1.2.5

### 1.3 Absolute maximum ratings. 1/2/

| Supply voltage (VA, VTC, VDR, VE)                                                                                | 2.2 V                       |

|------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Supply difference maximum (VA/TC/DR/E) – minimum (VA/TC/DR/E)                                                    | 0 V to 100 mV               |

| Voltage on any input pin (device 01)<br>Voltage on any input pin (except +Vinl, -Vinl, +VinQ, -VinQ) (device 02) |                             |

| Voltage on +VIN, -VIN (maintaining common mode)                                                                  |                             |

| Ground difference maximum (GNDTC/DR/E) – minimum (GNDTC/DR/E)                                                    |                             |

| Input current at any pin                                                                                         |                             |

| Power dissipation at $T_{C} \le 125^{\circ}C$ :                                                                  | <u>100 m/( <u>0</u>/</u>    |

| Device 01                                                                                                        | 24W 4/                      |

| Device 02                                                                                                        | _                           |

| Storage temperature                                                                                              | -65°C to +150°C             |

| Maximum junction temperature (TJ)                                                                                | +150°C                      |

| Electrostatic discharge (ESD):                                                                                   |                             |

| Human body model (HBM)                                                                                           |                             |

| Charged device model (CDM)                                                                                       | 1500 V                      |

| 1.4 Recommended operating conditions. 6/                                                                         |                             |

| <u>riocommendou operang contaneno</u> . <u>o</u> ,                                                               |                             |

| Supply voltage (VA, VTC, VE)                                                                                     | +1.8 V to +2.0 V            |

| Driver supply voltage (VDR)                                                                                      | +1.8 V to VA                |

| +VIN, -VIN voltage rang                                                                                          | -0.4 V to +2.4 V <u>7</u> / |

| +VIN, -VIN current range (ac coupled)                                                                            | ±50 mA <u>7</u> /           |

| +VIN, -VIN power:                                                                                                |                             |

| Maintaining common mode voltage (ac coupled)                                                                     | 15.3 dBm                    |

| Not maintaining common mode voltage (ac coupled)                                                                 | 17.1 dBm                    |

| CLK pins voltage range                                                                                           | 0 V to VA                   |

| Differential CLK amplitude                                                                                       | 0.4 VPP to 2.0 VPP          |

| Case operating temperature range (Tc)                                                                            | -55°C to +125°C             |

|                                                                                                                  |                             |

<sup>1/</sup> Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

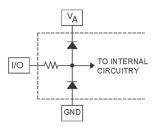

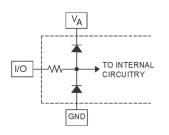

- 2/ The analog inputs are protected as shown above. Input voltage magnitudes beyond the absolute maximum ratings may damage this device.

- 3/ When the input voltage at any pin exceed the power supply limit; (for example, less than GND or greater than VA), the current at that pin should be limited to 50 mA. In addition, over voltage at a pin must adhere to maximum voltage limits. Simultaneously over voltage at multiple pins require adherence to the maximum package power dissipation limits.

- <u>4</u>/ Dissipation limit is calculated using JEDEC JESD51-7 thermal model. Higher dissipation may be possible based on specific application thermal situation and specified thermal resistances.

- 5/ Human body model is 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor.

- 6/ Unless otherwise specified, all voltages are measured with respect to GND = GND<sub>DR</sub> = GND<sub>E</sub> = GND<sub>TC</sub> = 0 V.

- 7/ Proper common mode voltage must be maintained to ensure proper output code, especially during input overdrive.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                | 5962-12205 |

|----------------------------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL | SHEET<br>3 |

## 1.5 Thermal characteristics.

| Thermal metric for case X                     | Symbol   | Device 01 | Device 02 | Unit |

|-----------------------------------------------|----------|-----------|-----------|------|

| Thermal resistance, junction-to-ambient       | θJA      | 10.4      | 13.1      | °C/W |

| Thermal resistance, junction-to-case (top)    | θJC(TOP) |           | 5.0       | °C/W |

| Thermal resistance, junction-to-board         | θЈΒ      | 3.2       | 5.1       | °C/W |

| Characterization parameter, junction-to-top   | ΨJT      | 0.5       | 2.6       | °C/W |

| Characterization parameter, junction-to-board | ψJB      |           | 4.7       | °C/W |

## 1.6 Radiation features.

Maximum total dose available (dose rate = 50 – 300 rads(Si)/s)..... 300 krads(Si) <u>8</u>/ Single event phenomena (SEP):

No single event latchup (SEL) occurs at effective LET (see 4.4.4.2) .....  $\leq$  120 MeV/(mg/cm<sup>2</sup>) <u>9</u>/

No single event functional interrupt (SEFI) occurs at effective LET (see 4.4.4.2) ..  $\leq$  120 MeV/(mg/cm<sup>2</sup>) <u>9</u>/

8/ Radiation end point limits for the noted parameters are guaranteed only for the conditions specified in MIL-STD-883, method 1019, condition A.

9/ Heavy ion testing facility was 88" Cyclotron Facility at Lawrence Berkeley National Laboratory (LBNL) located in Berkeley, California and ion beam energy was 4.5 MeV/nucleon exposed inside a vacuum chamber. No single event latch-up (SEL) or single-event functional interrupt (SEFI) was observed when irradiated with Bismuth(Bi) ions at fluence 1 x 10<sup>7</sup> ions/cm<sup>2</sup> at an angle 35° with bias voltage 1.8 V and 2.0 V corresponding to an effective LET of 120 MeV/(mg/cm<sup>2</sup>). For more information on SEP test results, customers are requested to contact the manufacturer.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                | 5962-12205 |

|----------------------------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL | SHEET<br>4 |

### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits. MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings. MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at https://quicksearch.dla.mil.)

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents are the issues of the documents cited in the solicitation or contract.

ASTM INTERNATIONAL (ASTM)

ASTM F1192 - Standard Guide for the Measurement of Single Event Phenomena (SEP) Induced by Heavy Ion Irradiation of semiconductor Devices.

(Copies of these documents are available online at https://www.astm.org.)

JEDEC Solid State Technology Association

| JEDEC 51-7 | _ | High Effective | Thermal | Conductivity | Test Board for | Leaded Su | Irface Mount | Packages |

|------------|---|----------------|---------|--------------|----------------|-----------|--------------|----------|

|            |   |                |         |              |                |           |              |          |

(Copies of these documents are available online at https://www.jedec.org.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                | 5962-12205 |

|----------------------------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL | SHEET<br>5 |

### 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 as specified herein, or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V.

3.2.1 <u>Case outline</u>. The case outline shall be in accordance with 1.2.4 herein and figure 1.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

3.2.3 Timing diagrams. The timing diagrams shall be as specified on figure 3.

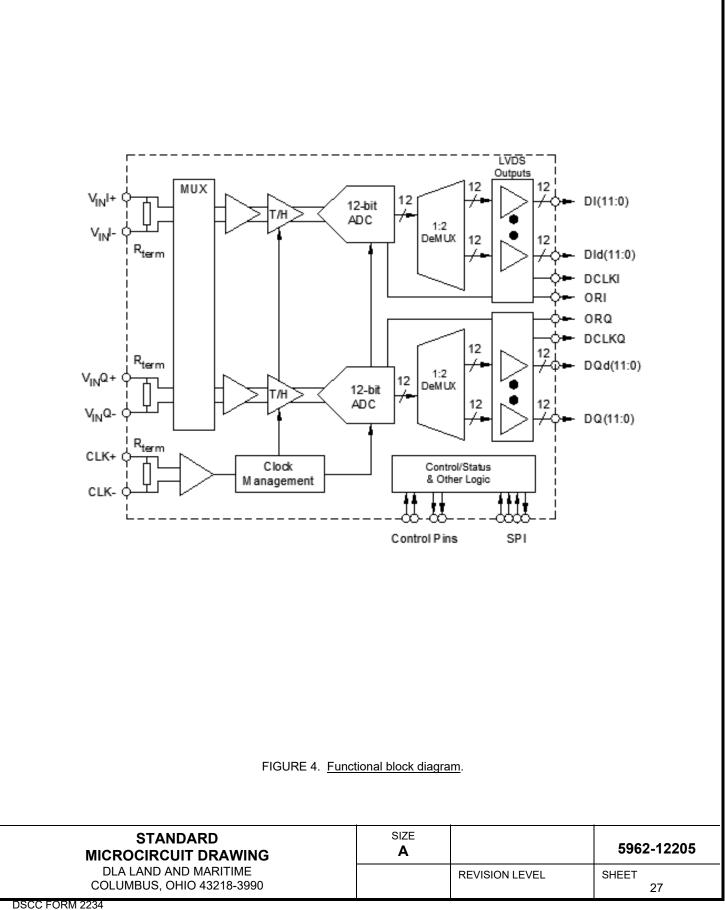

3.2.4 Functional block diagram. The functional block diagrams shall be as specified on figure 4.

3.2.4 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing and acquiring activity upon request.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table IA and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table IA.

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535.

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). The certificate of compliance submitted to DLA Land and Maritime-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                | 5962-12205 |

|----------------------------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL | SHEET<br>6 |

|                                                    | TAE         | BLE IA. <u>Electrical pe</u>             | erformance ch                                                                  | aracteristics. |          |       |       |       |

|----------------------------------------------------|-------------|------------------------------------------|--------------------------------------------------------------------------------|----------------|----------|-------|-------|-------|

| Test                                               | Test Symbol |                                          | ymbol Conditions $1/2/3/4/$ G<br>$-55^{\circ}C \le T_{C} \le +125^{\circ}C$ su |                |          | Li    | mits  | Unit  |

|                                                    |             | unless otherwise                         | e specified                                                                    |                |          | Min   | Max   |       |

| Static converter characteristics                   |             |                                          |                                                                                |                |          |       | -     | -     |

| Integral non-linearity (best fit)                  | INL         | Direct current (dc)<br>1 MHz sine wave c | -                                                                              | 1,2,3          | 01, 02   | -7.5  | +7.5  | LSB   |

| Differential non-linearity                         | DNL         | DC coupled, 1 MH:<br>over ranged         | z sine wave                                                                    | 1,2,3          | 01, 02   | -1.35 | 1.35  | LSB   |

| Resolution with no missing codes                   |             |                                          |                                                                                | 1,2,3          | 01, 02   |       | 12    | Bits  |

| Positive full scale error                          | PFSE        | <u>5</u> /                               |                                                                                | 1,2,3          | 01, 02   | -30   | 30    | mV    |

| Negative full scale error                          | NFSE        | <u>5</u> /                               |                                                                                | 1,2,3          | 01, 02   | -30   | 30    | mV    |

| Out of range output code                           |             | +VINVIN > + full                         | scale                                                                          | 1,2,3          | 01, 02   |       | 4095  | -     |

|                                                    |             | +VINVIN < - full :                       | scale                                                                          |                |          | 0     |       |       |

| Dynamic converter characteristics.                 |             |                                          |                                                                                |                |          |       |       |       |

| 1:2 Demux, non-DES mode, non-E                     | CM, non-    | LSPSM, fCLK = 1.6                        | GHz, fin = 24                                                                  | 8 MHz, Vin =   | -0.5 dBF | S.    |       |       |

| Effective number of bits                           | ENOB        |                                          |                                                                                | 4,5            | 01       | 8.5   |       | Bits  |

|                                                    |             |                                          |                                                                                | 6              |          | 8.1   |       |       |

|                                                    |             |                                          |                                                                                | 4              | 02       | 8.8   |       |       |

|                                                    |             |                                          |                                                                                | 5              | -        | 8.7   |       |       |

|                                                    |             |                                          |                                                                                | 6              | -        | 8.4   |       | -     |

| Signal to noise plus distortion                    | SINAD       |                                          |                                                                                | 4,5            | 01       | 53.0  |       | dBFS  |

| ratio                                              |             |                                          |                                                                                | 6              |          | 50.6  |       |       |

|                                                    |             |                                          |                                                                                | 4              | 02       | 54.7  |       |       |

|                                                    |             |                                          |                                                                                | 5              |          | 54.1  |       |       |

|                                                    |             |                                          |                                                                                | 6              | -        | 52.3  |       |       |

| Signal to noise ratio                              | SNR         |                                          |                                                                                | 4,5            | 01       | 54.6  |       | dBFS  |

| 0                                                  |             |                                          |                                                                                | 6              | -        | 52.5  |       | -     |

|                                                    |             |                                          |                                                                                | 4              | 02       | 56    |       |       |

|                                                    |             |                                          |                                                                                | 5              | -        | 54.6  |       |       |

|                                                    |             |                                          |                                                                                | 6              |          | 53.5  |       |       |

| Total harmonic distortion                          | THD         |                                          |                                                                                | 4,5            | 01       |       | -58.6 | dBFS  |

|                                                    |             |                                          |                                                                                | 6              |          |       | -55.1 |       |

|                                                    |             |                                          |                                                                                | 4,5            | 02       |       | -59.2 |       |

|                                                    |             |                                          |                                                                                | 6              |          |       | -55.5 |       |

| See footnotes at end of table.                     |             | ·                                        |                                                                                |                | ·        |       |       | ·     |

| STANDA<br>MICROCIRCUIT                             | DRAWI       |                                          | SIZE<br><b>A</b>                                                               |                |          |       | 5962- | 12205 |

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |             |                                          |                                                                                | REVISIO        | ON LEVEL |       | SHEET | 7     |

| Test                             | Symbol        | Conditions <u>1/ 2/ 3/ 4</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C | Group A<br>subgroups | Device<br>type                                | Limits      |       | Unit |

|----------------------------------|---------------|-------------------------------------------------------------------|----------------------|-----------------------------------------------|-------------|-------|------|

|                                  |               | unless otherwise specified                                        |                      |                                               | Min         | Max   |      |

| Dynamic converter characteristic | cs – continue | d.                                                                |                      |                                               |             |       |      |

| 1:2 Demux, non-DES mode, nor     | n-ECM, non-L  | _SPSM, fCLK = 1.6 GHz, fIN = 24                                   | 18 MHz, VIN =        | -0.5 dBF                                      | S - continu | ued.  |      |

| Spurious free dynamic range      | SFDR          |                                                                   | 4,5                  | 01                                            | 58.0        |       | dBFS |

|                                  |               |                                                                   | 6                    |                                               | 55.0        |       |      |

|                                  |               |                                                                   | 4                    | 02                                            | 58.9        |       |      |

|                                  |               |                                                                   | 5                    |                                               | 58.1        |       |      |

|                                  |               |                                                                   | 6                    |                                               | 56          |       |      |

| 1:2 Demux, non-DES mode, nor     | n-ECM, LSPS   | SM, fclk = 800 MHz, fin = 248 N                                   | 1Hz, VIN = -0.       | 5 dBFS.                                       |             |       |      |

| Effective number of bits         | ENOB          |                                                                   | 4,5                  | 01                                            | 8.9         |       | Bits |

|                                  |               |                                                                   | 6                    |                                               | 8.5         |       |      |

|                                  |               |                                                                   | 4,5                  | 02                                            | 9.1         |       |      |

|                                  |               |                                                                   | 6                    |                                               | 8.6         |       |      |

| Signal to noise plus distortion  | SINAD         |                                                                   | 4,5                  | 01                                            | 55.4        | dBFS  |      |

| ratio                            |               |                                                                   | 6                    | 53.0                                          | 53.0        |       | -    |

|                                  |               |                                                                   | 4,5                  | 02                                            | 56.5        |       |      |

|                                  |               |                                                                   | 6                    |                                               | 53.5        |       |      |

| Signal to noise ratio            | SNR           |                                                                   | 4,5                  | 01                                            | 56.4        |       | dBFS |

| 0                                |               |                                                                   | 6                    |                                               | 55.8        |       |      |

|                                  |               |                                                                   | 4,5                  | 02                                            | 57.6        |       |      |

|                                  |               |                                                                   | 6                    |                                               | 56.8        |       | _    |

| Total harmonic distortion        | THD           |                                                                   | 4,5                  | 01, 02                                        |             | -62.3 | dBFS |

|                                  |               |                                                                   | 6                    |                                               |             | -57.0 |      |

| Spurious free dynamic range      | SFDR          |                                                                   | 4,5                  | 01                                            | 62.5        |       | dBFS |

| 1 , 3                            |               |                                                                   | 6                    |                                               | 57.7        |       |      |

|                                  |               |                                                                   | 4,5                  | 02                                            | 62.5        |       | 1    |

|                                  |               |                                                                   | 6                    |                                               | 57.5        |       |      |

| See footnotes at end of table.   |               |                                                                   |                      | <u>                                      </u> | 01.0        |       |      |

| STANDARD                  |  |

|---------------------------|--|

| MICROCIRCUIT DRAWING      |  |

| DLA LAND AND MARITIME     |  |

| COLUMBUS, OHIO 43218-3990 |  |

| SIZE<br>A |                | 5962-12205 |

|-----------|----------------|------------|

|           | REVISION LEVEL | SHEET<br>8 |

|                                             | TABLE IA    | . Electrical performance characte                                           | <u>ristics</u> - Conti | nued.          |             |          |      |

|---------------------------------------------|-------------|-----------------------------------------------------------------------------|------------------------|----------------|-------------|----------|------|

| Test                                        | Symbol      | Conditions <u>1/ 2/ 3/ 4</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C           | Group A<br>subgroups   | Device<br>type | Lii         | mits     | Unit |

|                                             |             | unless otherwise specified                                                  |                        |                | Min         | Max      |      |

| Analog input/output and reference           | character   | istics.                                                                     |                        |                |             | 1        | 1    |

| Analog difference input full<br>scale range | VIN_<br>FSR | FSR pin Y3 high                                                             | 4,5,6                  | 01, 02         | 750         | 890      | mVPP |

| Differential input resistance               | RIN         |                                                                             | 1,2,3                  | 01, 02         | 99          | 107      | Ω    |

| Common mode output voltage                  | Vсмо        | ICMO = ±100 μA                                                              | 1,2,3                  | 01, 02         | 1.15        | 1.35     | V    |

| Bandgap reference output<br>voltage         | Vbg         | IBG = ±100 μA                                                               | 1,2,3                  | 01, 02         | 1.15        | 1.35     | V    |

| Digital control and output pin chara        | acteristics | -                                                                           |                        |                |             |          |      |

| Digital control pins (DES, LSPSM,           | CAL, PDI    | , PDQ, TPM, NDM, FSR, DDRPh                                                 |                        | k, SDI, S      | CS ).       |          |      |

| Logic high input voltage                    | Viн         | DES, LSPSM, CAL, PDI, PDQ,<br>TPM, NDM, FSR, DDRPh,<br>ECE , SCLK, SDI, SCS | 1,2,3                  | 01, 02         | 0.7 X<br>VA |          | V    |

| Logic low input voltage                     | VIL         | DES, LSPSM, CAL, PDI, PDQ,<br>TPM, NDM, FSR, DDRPh,<br>ECE , SCLK, SDI, SCS | 1,2,3                  | 01, 02         |             | 0.3 X VA | V    |

| Input current high,<br>VIN = VA             | Ιн          | DES, LSPSM, CAL, PDI, PDQ,<br>TPM, NDM, FSR, DDRPh,<br>ECE , SCLK, SDI, SCS | 1,2,3                  | 01, 02         | -1          | 1        | μΑ   |

| Input current low,<br>VIN = GND             | lı∟         | DES, LSPSM, CAL, TPM,<br>NDM, FSR, DDRPh,                                   | 1,2,3                  | 01, 02         | -1          | 1        | μΑ   |

|                                             |             | SCLK, SDI, SCS                                                              |                        |                | -30         |          |      |

|                                             |             | PDI, PDQ, ECE                                                               |                        |                | -55         |          |      |

| Input leakage current                       | Іін         | VIN = VA                                                                    | 1,2,3                  | 02             | -1          | 1        | μA   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                | 5962-12205 |

|----------------------------------------------------|------------------|----------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL | SHEET<br>9 |

| Test                                                | Symbol      | Conditions <u>1/ 2/ 3</u> / <u>4</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C | Group A<br>subgroups | Device<br>type | Limits |      | Unit |

|-----------------------------------------------------|-------------|---------------------------------------------------------------------------|----------------------|----------------|--------|------|------|

|                                                     |             | unless otherwise specified                                                |                      |                | Min    | Max  |      |

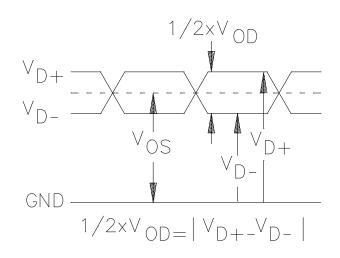

| Digital outputs pin (data, DCLKI, I                 | DCLKQ, O    | RI, ORQ). See figure 3.                                                   |                      |                |        |      | T    |

| LVDS differential output voltage                    | VOD         | VBG = floating, OVS = VA                                                  | 1,2,3                | 01             | 380    | 840  | mVPP |

|                                                     |             | VBG = floating, OVS = GND                                                 |                      |                | 240    | 650  |      |

|                                                     |             | VBG = floating, OVS = High                                                |                      | 02             | 380    | 840  |      |

|                                                     |             | VBG = floating, OVS = Low                                                 |                      |                | 240    | 650  |      |

| Change in LVDS output swing<br>between logic levels | ∆Vo<br>DIFF |                                                                           | 1,2,3                | 01, 02         | -20    | 20   | mV   |

| Logic high output level                             | Vон         | CalRun, SDO I <sub>OH</sub> = -400 μA                                     | 1,2,3                | 01, 02         | 1.5    |      | V    |

| Logic low output level                              | Vol         | CalRun, SDO IOL = 400 μA                                                  | 1,2,3                | 01             |        | 0.3  | V    |

|                                                     |             |                                                                           |                      | 02             | 0.3    |      |      |

| Power supply characteristics.                       |             |                                                                           |                      |                |        |      |      |

| fCLK = 1.6 GHz, 1:2 Demux mode                      | e, non-LSP  | SM.                                                                       |                      |                |        |      |      |

| Analog supply current                               | IA          | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 1290 | mA   |

| Track and hold and clock supply current             | Ітс         | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 520  | mA   |

| Output driver supply current                        | IDR         | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 380  | mA   |

| Digital encoder supply current                      | IE          | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 163  | mA   |

| Total current                                       | IT          | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 2280 | mA   |

|                                                     |             | PDI = low, PDQ = high                                                     |                      |                |        | 1300 |      |

|                                                     |             | PDI = high, PDQ = low                                                     |                      |                |        | 1300 |      |

| Power consumption                                   | PC          | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 4.4  | W    |

| See footnotes at end of table.                      |             |                                                                           |                      |                |        |      |      |

| TABLE IA. | Electrical | performance | characteristics | - Continued. |

|-----------|------------|-------------|-----------------|--------------|

|-----------|------------|-------------|-----------------|--------------|

| STANDARD                    |  |  |  |  |

|-----------------------------|--|--|--|--|

| <b>MICROCIRCUIT DRAWING</b> |  |  |  |  |

| DLA LAND AND MARITIME       |  |  |  |  |

| COLUMBUS, OHIO 43218-3990   |  |  |  |  |

5962-12205

|                                            |            |                                                                           | <u></u>              |                |        |      |      |

|--------------------------------------------|------------|---------------------------------------------------------------------------|----------------------|----------------|--------|------|------|

| Test                                       | Symbol     | Conditions <u>1/ 2/ 3</u> / <u>4</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C | Group A<br>subgroups | Device<br>type | Limits |      | Unit |

|                                            |            | unless otherwise specified                                                |                      |                | Min    | Max  |      |

| fCLK = 800 MHz, 1:2 Demux mod              | le, LSPSM. |                                                                           |                      |                |        |      |      |

| Analog supply current                      | IA         | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 860  | mA   |

| Track and hold and clock<br>supply current | Ітс        | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 380  | mA   |

| Output driver supply current               | IDR        | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 350  | mA   |

| Digital encoder supply current             | IE         | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 79   | mA   |

| Total current                              | IT         | PDI = PDQ = low                                                           | 1,2,3                | 01, 02         |        | 1620 | mA   |

|                                            |            | PDI = low, PDQ = high                                                     |                      |                |        | 940  |      |

|                                            |            | PDI = high, PDQ = low                                                     |                      |                |        | 940  |      |

| Power consumption                          | PC         | PDI = PDQ = low                                                           | 1,2,3                | 02             |        | 3.1  | W    |

| Input clock (CLK).                         |            |                                                                           | <u>.</u>             |                |        |      |      |

| Maximum input clock                        | fCLK       | Non-LSPSM                                                                 | 4,5,6                | 01, 02         | 1.6    |      | GHz  |

| frequency                                  | (max)      | LSPSM                                                                     |                      |                | 800    |      | MHz  |

| Minimum input clock                        | fCLK       | Non-DES mode                                                              | 4,5,6                | 01             |        | 200  | MHz  |

| frequency                                  | (min)      | DES mode                                                                  |                      |                |        | 250  |      |

|                                            |            | Non-LSPSM, non-DES mode;<br>LFS = 1B                                      |                      | 02             |        | 200  |      |

|                                            |            | Non-LSPSM, DES mode                                                       |                      |                |        | 250  |      |

|                                            |            | LSPSM, non-DES mode                                                       |                      |                |        | 200  |      |

<u>1</u>/ Devices supplied to this drawing have been characterized to levels M, D, P, L, R, F of irradiation, but devices supplied are tested at levels R and F. Pre and Post irradiation values are identical unless otherwise specified in Table IA.

When performing post irradiation electrical measurements for any RHA level, T<sub>A</sub> = +25°C.

$\underline{2}$ / Unless otherwise specified, the following specifications apply after calibration for VA = VDR = VTC = VE = +1.9 V; I- and Q- channels ac coupled, FSR pin = high; CL = 10 pF; differential ac coupled sine wave input clock, fCLK = 1.6 GHZ at 0.5 VPP with 50% duty cycle; VBG = floating; non-extended control mode; Rext = Rtrim = 3300  $\Omega \pm 0.1$  %; analog signal source impedance = 100  $\Omega$  differential; 1:2 demultiplex non DES mode; I- and Q- channels; duty cycle stabilizer on. The maximum clock frequency for non-demux mode is 1 GHZ.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                | 5962-12205  |

|----------------------------------------------------|------------------|----------------|-------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL | SHEET<br>11 |

3/ The analog inputs are protected as shown below. Input voltage magnitudes beyond the absolute maximum ratings may damage this device.

- 4/ To guarantee accuracy, it is required that VA, VTC, VE and VDR be well bypassed. Each supply pin must be decoupled with separate bypass capacitors.

- <u>5</u>/ Calculation of full scale error for this device assumes that the actual reference voltage is exactly its nominal value.

Full scale error for this device, therefore, is a combination of full scale error and reference voltage error.

See manufacturer's datasheet for information transfer characteristic for relationship between gain error and full scale error, see specification definitions for gain error.

| Device type | SEP     | Supply voltages | Effective linear energy transfer<br>(LET)     |

|-------------|---------|-----------------|-----------------------------------------------|

| 02          | No SEL  | 1.8 V and 2.0 V | $\text{LET} \leq 120 \; \text{MeV/(mg/cm}^2)$ |

|             | No SEFI | 1.8 V and 2.0 V | $\text{LET} \leq 120 \; \text{MeV/(mg/cm}^2)$ |

TABLE IB. SEP test limits. 1/2/3/4/

- 1/ For single event phenomena (SEP) test conditions, see 4.4.4.2 herein.

- <u>2</u>/ Technology characterization and model verification supplemented by in-line data may be used in lieu of end-of-line testing. Test plan must be approved by technical review board and qualifying activity.

- <u>3</u>/ Tested for single event latch up at worse case temperature, TC = +125°C  $\pm$  10°C.

4/ Heavy ion testing facility was 88" Cyclotron Facility at Lawrence Berkeley National Laboratory (LBNL) located in Berkeley, California and ion beam energy was 4.5 MeV/nucleon exposed inside a vacuum chamber. No single event latch-up (SEL) or single-event functional interrupt (SEFI) was observed when irradiated with Bismuth (Bi) ions at fluence 1 x 10<sup>7</sup> ions/cm<sup>2</sup> at an angle 35° with bias voltage 1.8 V and 2.0 V corresponding to an effective LET of 120 MeV/(mg/cm<sup>2</sup>). For more information on SEP test results, customers are requested to contact the manufacturer.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                | 5962-12205  |

|----------------------------------------------------|-----------|----------------|-------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL | SHEET<br>12 |

| Case | Х |

|------|---|

|      |   |

|        |                   |          | Dimer  | nsions      |           |        |  |

|--------|-------------------|----------|--------|-------------|-----------|--------|--|

| Symbol |                   | Inches   |        | Millimeters |           |        |  |

|        | Min               | Nominal  | Max    | Min         | Nominal   | Max    |  |

| А      | .116              | .127     | .138   | 2.94        | 3.22      | 3.5    |  |

| A1     | .101              | .110     | .119   | 2.54        | 2.79      | 3.04   |  |

| A2     | .015              | .020     | .025   | 0.37        | 0.5       | 0.63   |  |

| A3     | .062              | .0673    | .0726  | 1.575       | 1.71      | 1.845  |  |

| A4     | .0817             | .0870    | .0923  | 2.075       | 2.21      | 2.345  |  |

| b      | .0181             | .0201    | .0221  | 0.459       | 0.51      | 0.561  |  |

| b1     | .0181             | .0201    | .0221  | 0.459       | 0.51      | 0.561  |  |

| D/E    | 1.0914            | 1.100    | 1.1086 | 27.72       | 27.94     | 28.16  |  |

| D1/E1  |                   | .950 BSC |        | 24.13 BSC   |           |        |  |

| D2/E2  | .394 BSC 10.0 BSC |          |        |             |           |        |  |

| D3/E3  | .8501             | .8587    | .8673  | 21.59       | 21.81     | 22.03  |  |

| D4/E4  | .777              | .7799    | .7828  | 19.734      | 19.19     | 19.886 |  |

| е      | .050 BSC          |          |        | 1.27 BSC    |           |        |  |

| e1     |                   | .039 BSC |        | 1.00 BSC    |           |        |  |

| e2     |                   | .950 BSC |        |             | 24.13 BSC |        |  |

NOTE:

1. Controlling dimensions are millimeter, inch dimensions are given for reference only.

FIGURE 1. Case outline - continued.

| Device<br>types    |                    | 01, 02             |                    |                    |                    |                    |                    |  |  |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|

| Case<br>outline    |                    | X                  |                    |                    |                    |                    |                    |  |  |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |  |  |

| A1                 | GND                | B1                 | Vbg                | C1                 | Rtrim+             | D1                 | V_A                |  |  |

| A2                 | V_A                | B2                 | GND                | C2                 | GND                | D2                 | Rtrim-             |  |  |

| A3                 | SDO                | B3                 | ECEb               | C3                 | Rext+              | D3                 | Rext-              |  |  |

| A4                 | TPM                | B4                 | SDI                | C4                 | SCSb               | D4                 | GND                |  |  |

| A5                 | NDM                | B5                 | CalRun             | C5                 | SCLK               | D5                 | GND                |  |  |

| A6                 | V_A                | B6                 | V_A                | C6                 | GND                | D6                 | CAL                |  |  |

| A7                 | GND                | B7                 | GND                | C7                 | V_A                | D7                 | Vbiasl             |  |  |

| A8                 | V_E                | B8                 | GND_E              | C8                 | V_E                | D8                 | V_A                |  |  |

| A9                 | GND_E              | B9                 | V_E                | C9                 | GND_E              | D9                 | V_A                |  |  |

| A10                | DId0+              | B10                | DId0-              | C10                | Dld1+              | D10                | Dld1-              |  |  |

| A11                | V_DR               | B11                | Dld2+              | C11                | Dld2-              | D11                | V_DR               |  |  |

| A12                | Dld3+              | B12                | Dld3-              | C12                | DId4+              | D12                | Dld4-              |  |  |

| A13                | GND_DR             | B13                | DId5+              | C13                | Dld5-              | D13                | GND_DR             |  |  |

| A14                | Dld6+              | B14                | DId6-              | C14                | DId7+              | D14                | Dld7-              |  |  |

| A15                | V_DR               | B15                | DId8+              | C15                | Dld8-              | D15                | V_DR               |  |  |

| A16                | Dld9+              | B16                | DId9-              | C16                | Dld10-             | D16                | GND_DR             |  |  |

| A17                | GND_DR             | B17                | Dld10+             | C17                | DI0-               | D17                | V_DR               |  |  |

| A18                | Dld11+             | B18                | DI0+               | C18                | V_DR               | D18                | DI3+               |  |  |

| A19                | Dld11-             | B19                | DI1+               | C19                | DI2+               | D19                | DI4+               |  |  |

| A20                | GND_DR             | B20                | DI1-               | C20                | DI2-               | D20                | DI4-               |  |  |

FIGURE 2. Terminal connections.

| types<br>Case      |                    |                    |                    | /                  |                    |                    |                    |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| outline            | X                  |                    |                    |                    |                    |                    |                    |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |

| E1                 | V_A                | H17                | DI9+               | M1                 | VinQ-              | R1                 | V_A                |

| E2                 | Tdiode+            | H18                | DI9-               | M2                 | GND_TC             | R2                 | GND_TC             |

| E3                 | Vbiasl             | H19                | DI10+              | M3                 | V_TC               | R3                 | V_TC               |

| E4                 | GND                | H20                | DI10-              | M4                 | VbiasQ             | R4                 | V_TC               |

| E17                | GND_DR             | J1                 | Vinl-              | M17                | GND_DR             | R17                | V_DR               |

| E18                | DI3-               | J2                 | GND_TC             | M18                | DQ11+              | R18                | DQ6+               |

| E19                | DI5+               | J3                 | V_TC               | M19                | DQ11-              | R19                | DQ6-               |

| E20                | DI5-               | J4                 | VbiasI             | M20                | GND_DR             | R20                | V_DR               |

| F1                 | V_A                | J17                | V_DR               | N1                 | VinQ+              | T1                 | V_A                |

| F2                 | GND_TC             | J18                | DI11+              | N2                 | V_TC               | T2                 | GND_C              |

| F3                 | Tdiode-            | J19                | DI11-              | N3                 | GND_TC             | Т3                 | GND_C              |

| F4                 | VbiasQ             | J20                | V_DR               | N4                 | V_A                | T4                 | GND                |

| F17                | GND_DR             | K1                 | GND                | N17                | DQ9+               | T17                | V_DR               |

| F18                | DI6+               | K2                 | Vbiasl             | N18                | DQ9-               | T18                | DQ3-               |

| F19                | DI6-               | K3                 | V_TC               | N19                | DQ10+              | T19                | DQ5+               |

| F20                | GND_DR             | K4                 | GND_TC             | N20                | DQ10-              | T20                | DQ5-               |

| G1                 | V_TC               | K17                | ORI+               | P1                 | V_TC               |                    |                    |

| G2                 | GND_TC             | K18                | ORI-               | P2                 | GND_TC             |                    |                    |

| G3                 | V_TC               | K19                | DCLKI+             | P3                 | V_TC               |                    |                    |

| G4                 | V_TC               | K20                | DCLKI-             | P4                 | V_TC               |                    |                    |

| G17                | DI7+               | L1                 | GND                | P17                | DQ7+               |                    |                    |

| G18                | DI7-               | L2                 | VbiasQ             | P18                | DQ7-               |                    |                    |

| G19                | DI8+               | L3                 | V_TC               | P19                | DQ8+               |                    |                    |

| G20                | DI8-               | L4                 | GND_TC             | P20                | DQ8-               |                    |                    |

| H1                 | Vinl+              | L17                | ORQ+               |                    |                    |                    |                    |

| H2                 | V_TC               | L18                | ORQ-               |                    |                    |                    |                    |

| H3                 | <br>GND_TC         | L19                | DCLKQ+             |                    |                    |                    |                    |

| H4                 | <br>V_A            | L20                | DCLKQ-             |                    |                    |                    |                    |

|                    |                    | l                  | <u> </u>           |                    | <u>I</u>           |                    | <u> </u>           |

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                | 5962-12205  |

|----------------------------------------------------|-----------|----------------|-------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL | SHEET<br>16 |

| Device<br>types    | 01, 02             |                    |                    |                    |                    |                    |                    |  |  |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|

| Case<br>outline    | X                  |                    |                    |                    |                    |                    |                    |  |  |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |  |  |

| U1                 | GND_C              | V1                 | CLK-               | W1                 | DCLK_<br>RST-      | Y1                 | GND                |  |  |

| U2                 | CLK+               | V2                 | DCLK_<br>RST+      | W2                 | GND                | Y2                 | V_A                |  |  |

| U3                 | PDI                | V3                 | PDQ                | W3                 | RSV                | Y3                 | FSR                |  |  |

| U4                 | GND                | V4                 | LSPSM              | W4                 | DDRPh              | Y4                 | RCLK+              |  |  |

| U5                 | GND                | V5                 | DES                | W5                 | RCLK-              | Y5                 | RCOut1+            |  |  |

| U6                 | RCOut1-            | V6                 | RCOut2+            | W6                 | V_A                | Y6                 | V_A                |  |  |

| U7                 | VbiasQ             | V7                 | RCOut2-            | W7                 | GND                | Y7                 | GND                |  |  |

| U8                 | V_A                | V8                 | V_E                | W8                 | GND_E              | Y8                 | V_E                |  |  |

| U9                 | V_A                | V9                 | GND_E              | W9                 | V_E                | Y9                 | GND_E              |  |  |

| U10                | DQd1-              | V10                | DQd1+              | W10                | DQd0-              | Y10                | DQd0+              |  |  |

| U11                | V_DR               | V11                | DQd2-              | W11                | DQd2+              | Y11                | V_DR               |  |  |

| U12                | DQd4-              | V12                | DQd4+              | W12                | DQd3-              | Y12                | DQd3+              |  |  |

| U13                | GND_DR             | V13                | DQd5-              | W13                | DQd5+              | Y13                | GND_DR             |  |  |

| U14                | DQd7-              | V14                | DQd7+              | W14                | DQd6-              | Y14                | DQd6+              |  |  |

| U15                | V_DR               | V15                | DQd8-              | W15                | DQd8+              | Y15                | V_DR               |  |  |

| U16                | V_DR               | V16                | DQd10-             | W16                | DQd9-              | Y16                | DQd9+              |  |  |

| U17                | GND_DR             | V17                | DQ0-               | W17                | DQd10+             | Y17                | GND_DR             |  |  |

| U18                | DQ3+               | V18                | GND_DR             | W18                | DQ0+               | Y18                | DQd11+             |  |  |

| U19                | DQ4+               | V19                | DQ2+               | W19                | DQ1+               | Y19                | DQd11-             |  |  |

| U20                | DQ4-               | V20                | DQ2-               | W20                | DQ1-               | Y20                | GND_DR             |  |  |

| STANDARD                  |  |  |  |  |

|---------------------------|--|--|--|--|

| MICROCIRCUIT DRAWING      |  |  |  |  |

| DLA LAND AND MARITIME     |  |  |  |  |

| COLUMBUS, OHIO 43218-3990 |  |  |  |  |

| SIZE<br>A |                | 5962-12205  |

|-----------|----------------|-------------|

|           | REVISION LEVEL | SHEET<br>17 |

| Device<br>types    | 01, 02             |                    |                    |                    |                    |  |  |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|

| Case<br>outline    |                    | ;                  | x                  |                    |                    |  |  |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |  |  |

| AA1                |                    | AC1                | GND                | AE1                | GND                |  |  |

| AA2                | GND                | AC2                | GND                | AE2                | GND                |  |  |

| AA3                | GND                | AC3                | GND                | AE3                | GND                |  |  |

| AA4                | GND                | AC4                | GND                | AE4                | GND                |  |  |

| AA5                | GND                | AC5                | GND                | AE5                | GND                |  |  |

| AA6                | GND                | AC6                | GND                | AE6                | GND                |  |  |

| AA7                | GND                | AC7                | GND                | AE7                | GND                |  |  |

| AA8                | GND                | AC8                | GND                | AE8                | GND                |  |  |

| AA9                | GND                | AC9                | GND                | AE9                | GND                |  |  |

| AA10               | GND                | AC10               | GND                | AE10               | GND                |  |  |

| AA11               | GND                | AC11               | GND                | AE11               | GND                |  |  |

| AB1                | GND                | AD1                | GND                | AF1                | GND                |  |  |

| AB2                | GND                | AD2                | GND                | AF2                | GND                |  |  |

| AB3                | GND                | AD3                | GND                | AF3                | GND                |  |  |