# **Contents**

| PREFACE                       | 2  |

|-------------------------------|----|

| IESD204B TI REFERENCE DESIGN  | 3  |

| REFERENCES                    | 3  |

| OVERVIEW                      | 4  |

| HOW TO BUILD                  | 5  |

| DESIGN                        | 6  |

| Interfaces                    | 6  |

| Programmable Parameters       | 6  |

| MICROBLAZE BLOCK              | 7  |

| Data Block                    | 9  |

| DIRECTORY STRUCTURE           | 10 |

| SCRIPTS                       | 11 |

| SOFTWARE                      | 12 |

| APPENDIX 1 REGISTER MAP       | 13 |

| READ ONLY STATUS REGISTER     | 14 |

| WRITEABLE BANK ADDRESSING     | 15 |

| Bank O Registers              | 16 |

| Bank 1 Registers              | 25 |

| Bank 2 Registers              | 25 |

| APPENDIX 2 GTX DRP ATTRIBUTES | 26 |

### **Preface**

This document details The JESD204B TI reference design for the TI TSW14J01 or Xilinx VC707 / KC705 / ZC706 evaluation kit's using TI's TSW14J10 interposer.

# **Important**

This reference design should not be used as an example for how to connect a specific ADC or DAC to a Xilinx FPGA. This reference design is capable of interfacing with all TI the FMC based ADC and DAC EVM's. To do this the design complexity is much greater than is required to simply interface to an ADC or DAC running with a specific configuration and much of the design has been abstracted and placed under HSDC Pro software control.

For a quick start to get your own design up and running. Refer to [1] Xilinx JESD204B LogiCORE IP Product Guide and start with the example design and demo testbench that is delivered when you generate a customized JESD204B core.

## JESD204B TI Reference design

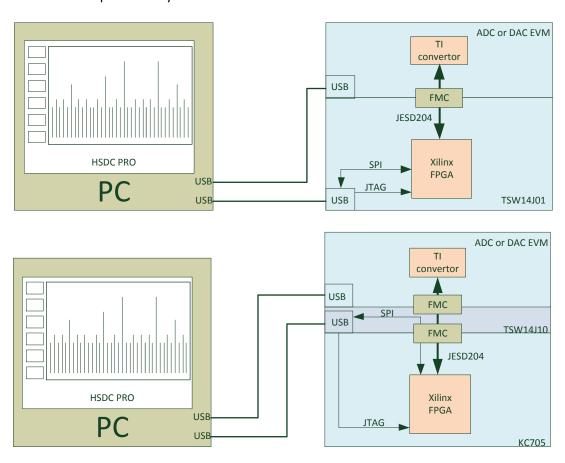

The TSW14J01 or VC707 / KC705 / ZC706 plus TSW14J10 interposer are used as evaluation platforms for TI ADC and DAC products interfacing to Xilinx FPGA's and Xilinx JESD204B Intellectual property (IP). All platforms work in conjunction with TI ADC and DAC EVM's and TI's PC based convertor evaluation software High Speed Data Convertor (HSDC) Pro. Figure's 1 shows an example of the system.

Figure 1 TSW14J01 and VC707/KC705/ZC706 plus TSW14J10 convertor evaluation system using HSDC Pro

This document assumes the user is familiar with the operation and functionality of HSDC Pro for convertor evaluation. Please see [1] for details. The HSDC Pro installer includes pre built bitstreams generated using this reference design. You do not need to build this project to use HSDC Pro.

## References

- [1] SLWU087A.pdf HSDC Pro GUI User Guide available from www.ti.com.

- [2] LogiCORE IP JESD204B v7.0 "pg066-jesd204.pdf".

- [3] 7 Series FPGAs GTX/GTH Transceivers user guide "ug476\_7Series\_Transceivers.pdf".

- [4] Kintex®-7 FPGAs Data Sheet: DC and Switching Characteristics "ds182\_Kintex\_7\_Data\_Sheet.pdf"

## **Overview**

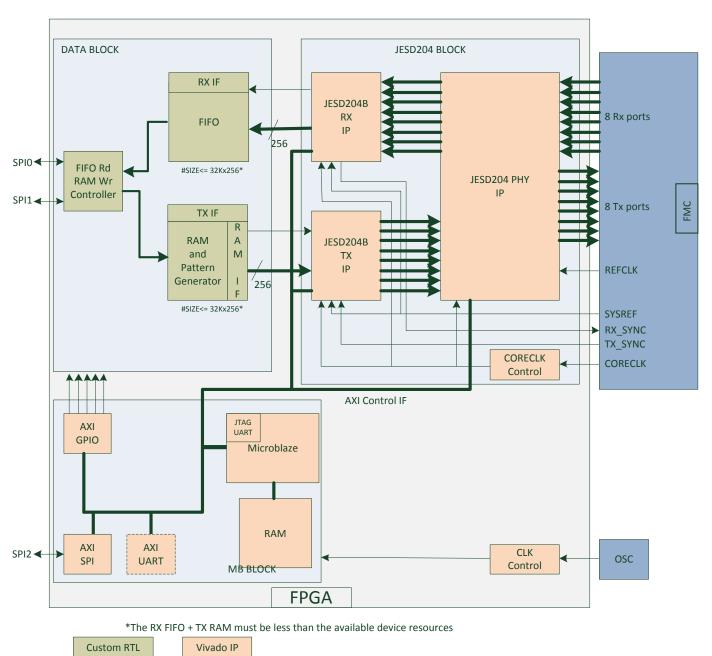

Figure 2 shows a high level block diagram of this design.

Figure 2 FPGA Block Diagram

This reference design shows the following:

- Transceiver sharing between TX and RX JESD204B cores using the JESD204B PHY core.

- Line rate switching through the full supported frequency range of the transceivers under software control.

- Interfacing to TX and RX JESD204B cores for data ingress and egress.

- Interfacing to TX and RX JESD204B cores for configuration of JESD204B link parameters using a MicroBlaze processor.

- Packaging hdl and IP blocks for use in IP integrator using TCL.

- Creating a JESD204B block diagram based design in IP integrator using TCL.

## How to build

The reference design is built by running a single script as follows:

- 1. Ensure you have Vivado 2016.1 installed.

- 2. Unzip the reference design into a folder of your choice.

- 3. Open the 2016.1 Vivado GUI and change directory into the unzipped reference design folder. You can change directory at the tcl prompt by simply typing *cd <path/dir>*. Also the command *pwd* will return the current working directory.

- 4. Type *source ./script/build\_it.tcl* at the Vivado TCL console.

- 5. Wait for the build to complete.

The reference design is configured by default to build for the VC707 platform. If you wish to build for the KC705 / ZC706 or TSW14J01. Simply edit the BOARD variable at the start of the build\_it.tcl script.

Please see the scripts section of this document for a detailed overview of the operations performed by this script and the sub-scripts called by it.

The build it script will create a project **proj\_VC707** and build it. Upon completion the implemented design will be opened.

After building the FPGA project you may rebuild the MicroBlaze software ELF file as follows:

- 1. Ensure you have built the project using the steps outlined above.

- 2. Export the hardware from Vivado and launch the SDK.

- 3. Using the SDK. Create a new project of type **Xilinx Application Project.** Name this project *tsw* and create it based on the Empty Application Template.

- 4. Copy .c and .h files from folder ./sw\_src/tsw/src to ./proj\_VC707/proj\_VC707.sdk/tsw/src

- 5. Refresh the project view (press F5 or choose refresh from the file menu). The copied project files should then be visible and compile cleanly.

## **Design**

#### **Interfaces**

The following physical ports are included in the design.

- **JESD204B:** There are 16 JESD204B lanes. One 8 lane receive link and one 8 lane transmit link. These ports are connected to the FMC HPC connector along with REFCLK and GLBLCLK to allow the connection of an ADC or DAC EVM.

- **SPI Control Port:** SPI port 2 is used as the control interface for the FPGA. Commands are written from the host PC to configure and control the programmable parameters of JESD204B sub-system. This SPI port uses the Xilinx SPI slave IP and is configured for 32 bit data transfers.

- **SPI DATA Ports**: SPI ports 0 and 1 are dedicated to transferring sample data to and from the host PC. These ports are only used to read from the data\_block RX FIFO's and write to the data\_block TX RAM's. The ports are configured for 32 bit data words.

- **UART**: There is a UART in the MicroBlaze sub-system. This UART is used to output system debug information. This port is connected to the USB UART on the VC707 and KC705. On the ZC706 this port is connected to a JTAG UART in the MicroBlaze Debug Module.

- **LED's**: There is a bank of LED's on each board used to show status. Note the polarity of the LED's on the TSW14J01 is reversed.

- **RESET Push button:** A soft reset of the system can be performed from a push button. This is connected to the **NORTH SW3** button on the VC707 and **NORTH SW2** on the KC705.

## **Programmable Parameters**

These parameters are changeable under software control from HSDC Pro using the USB to SPI interface to the FPGA.

- JESD204B GTX REFCLK and line rate (see appendix 2 for an explanation of the parameters being reprogrammed).

- The JESD204B lanes in use (see [1] for a description on the lanes in use register).

- 1 to 8 active transmitter ports.

- 1 to 8 active receiver ports.

- JESD204B TX and RX link parameters.

- As specified in [1] page 99 Table 20 "Link configuration parameters".

See Appendix 1 for a full map and description of the registers accessible via the SPI control interface.

### MicroBlaze Block

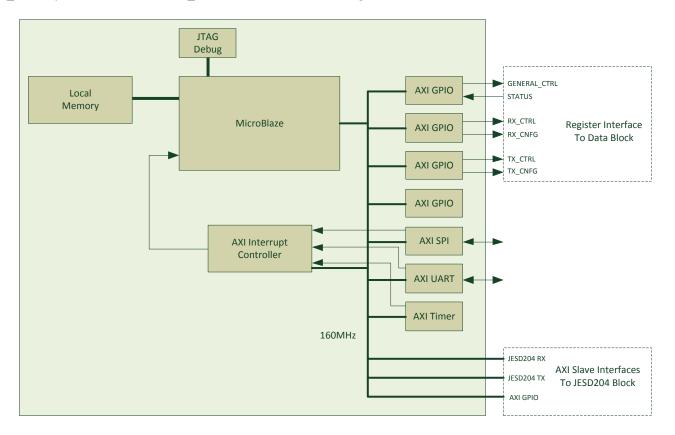

The **mb\_block** block implements the MicroBlaze processor susbsystem. Figure 3 shows an overview the internals of the **mb\_block** (please refer to the mb\_block created within IP Integrator for a more detailed view).

Figure 3 mb\_block

The MicroBlaze processor block is configured as follows:

- A MicroBlaze Debug Monitor provides JTAG access for debug and software development.

- Internal FPGA Block RAM's are used for program and data memory. The MicroBlaze does not use any off chip memory.

- An AXI SPI slave interface provides the control interface to the system. This SPI interface is both an SPI slave and an AXI slave. This interface is configured to generate an interrupt when its receive buffer is full.

- An AXI UART interface. This interface is provided purely for debug.

- Multiple AXI GPIO interfaces are setup to provide the register interface to the data\_block

- An AXI GPIO to drive the on board LED's (Note the LED's must be connected to the mb\_block for this to function.

By default the LED's are connected to the jesd204\_block)

- Three AXI interface ports for connection to the jesd204\_block.

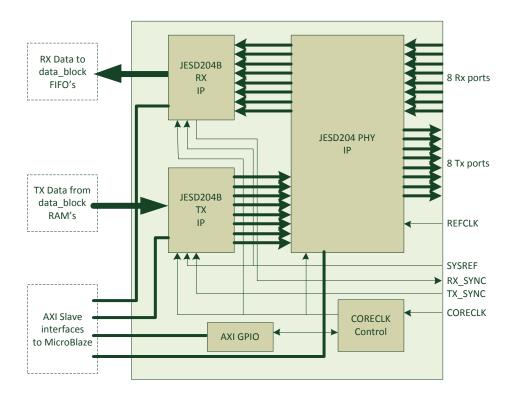

#### JESD204 Block

The **jesd204\_block** implements the JESD204B TX, RX and PHY IP and subsystem. Figure 4 shows an overview the internals of the **jesd204\_block** (please refer to the jesd204\_block created within IP Integrator for a more detailed view).

#### The JESD204 block contains:

- Xilinx JESD204B v6.1 TX and RX IP configured with 8-lanes per link and shared logic in example design. The JESD204B TX and RX cores are configured and monitored via corresponding AXI4-Lite management interfaces [2].

- An AXI GPIO interface providing block-level control & status.

- A JESD204B PHY v2.0 configured with both CPLL's and QPLL supported. This IP implements the Xilinx GTX

transceiver logic and control interfaces. The JESD204B PHY core has an AXI register interface to allow the GTX

transceiver and PLL parameters to be reprogrammed to dynamically change the supported line rate.

The GTX clocking attributes corresponding to the supported frequency bands (see register CNFG\_JESD\_RATE) are listed in Appendix 2.

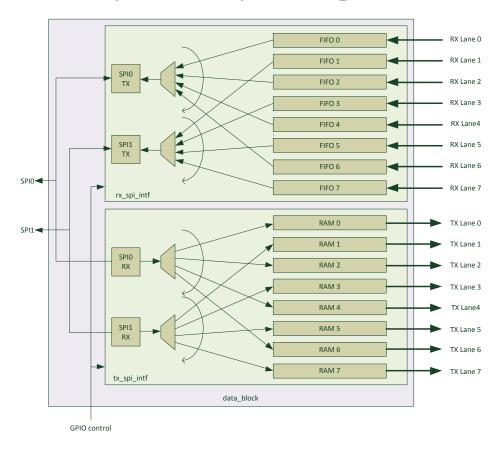

#### **Data Block**

The **data\_block** implements the data interface to the system. A FIFO is in included for each JESD204B RX lane and a RAM block for each JESD204B TX lane see figure 5 for a block diagram of the **data\_block** internals.

Figure 5 RX sample FIFO logic

Figure 6 shows how the JESD204B RX and TX lanes are connected to capture FIFO's and RAM's Figure 6 also shows how the FIFO's and RAMs are connected to the SPI ports. This split multiplexed arrangement allows the required sample data bandwidth to be shared between the two SPI ports. Each 32-bit SPI read or write causes the read or write multiplexor logic to advance to the next FIFO or RAM in the sequence. Individual enable bits are provided to control how many lanes are active and therefore the sequencing of the two read or write multiplexor's (See register RX\_CNFG and TX\_CNFG in appendix 1).

Capture and playback control of the data\_block is controlled from HSDC Pro by writing to registers RX\_CTRL and TX\_CTRL whilst monitoring the Sample Block Status bits in the Status Register.

## **Directory Structure**

#### ./hdl

Contains all the project hdl sources in individual directories.

### ./hdl/data\_block/

Contains the source hdl for the data\_block section of the design.

#### ./hdl/jesd204\_extras/

Contains the source hdl for the control & status GPIO interface and core clock divider logic.

### ./hdl/plat\_id/

Contains the source hdl for the platform identification module used in the design.

### ./script

Contains all the scripts and sub-scripts used to generate IP, package sub-blocks and build the design hierarchy in IPI see the script section of this document for an overview.

### ./sw\_src

Contains the source code for the Microblaze software running in this reference design. See the software section in this document for an overview.

#### ./constraints

Contains the constraints files used to build this design for the supported boards.

After running the build\_it.tcl script you will find the following directories have been created.

#### ./local\_IP\_<BOARD>/projects/

This directory contains local projects generated to create packaged IP for use in the main project. The directory name contains the name of the board that was selected to build for (default VC707).

### ./local\_IP\_<BOARD>/repository/

This directory contains packaged IP for use in the main project. This packaged IP can be reused in other projects. The directory name contains the name of the board that was selected to build for (default VC707).

### ./proj\_<BOARD>/

This directory contains the actual reference design project. The directory name contains the name of the board that was selected to build for (default VC707).

## **Scripts**

The scripts directory contains all the script used to build the design from the sources provided.

#### build\_it.tcl:

This script is the main build script for the whole project. This script contains parameters that control the build configuration and does the following.

- Creates the main Vivado project.

- Creates directory ./local\_IP\_<BOARD>/projects/ to hold local projects created to package IP for use in the main project.

- Creates directory ./local\_IP\_<BOARD>/repository/ to hold locally created packaged IP.

- Calls script gen\_and\_pkg\_data\_block\_IP.tcl (see description that follows).

- Calls script **gen\_and\_pkg\_single\_file\_module\_IP.tcl** to package rtl block **jesd\_extras**.

- Calls script gen\_and\_pkg\_single\_file\_module\_IP.tcl to package rtl block plat\_id.

- Adds the local packaged IP repository ./local\_IP\_<BOARD>/repository/ to the main project.

- Calls script create\_block\_diag.tcl which creates the IPI block diagram.

- Synthesizes the design.

- Implements the design and produces a bitstream.

- Exports the implemented design to the Xilinx SDK.

#### gen\_and\_pkg\_data\_block\_IP.tcl:

This sub-script creates and packages a project for the data block hdl to use as a block in IP integrator as follows:

- Creates a Vivado project ./local\_IP/projects/data\_block/data\_block.xpr.

- Imports hdl files from the ./hdl/data\_block/ directory.

- Packages the project using IP packager.

- Copies the packaged project to the local repository directory./local\_IP/repository/.

Page 12 of 26

## **Software**

The source code for the software running on the MicroBlaze processor is included for reference. The following gives a brief overview of the functionality.

tsw.c This is the main source file that initializes the system and then runs in a loop processing received commands.

The commands are received over the SPI control port. An SPI Interrupt service routine places the commands into a software queue for the main loop to process.

version.h This files contains the software version number.

**global.h** This file contains the register address definitions for the SPI control interface.

tsw spi.c and tsw\_spi.h These files are the source files for the SPI interface functions.

queue.c and queue.h These files are the source files for the command queue.

data\_block.c and data\_block.h These files are the source files for the control of the data\_block.

jesd204.c and jesd204.h These files are the source files for the control of the jesd204 blocks.

*clocks.c* and *clocks.h* These files are the source files used for programming the line rate of the transceivers used by the JESD204B cores.

# **Appendix 1 Register Map**

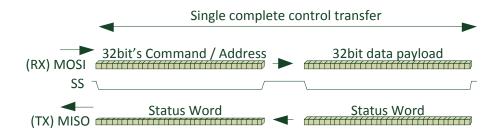

This section details the map of the register interface that is accessed via the SPI control port SPI2 from the host PC. The register map is split into two sections. A single 32-bit read only status register and an addressable write only register space. The address range of the writeable register space is 30-bits. The 30-bit address space is further broken down into banks 1MByte in size. For simplicity all addressing is performed using bytes, but only 32-bit word writes are possible. The following simple protocol is used for communication.

- SPI configured for 32bit word transfers

- Two 32-bit word transfers are required per control write

- The first word constitutes a 2-bit command and a 30-bit address, in the register map, to be written to

- The second word constitutes the data payload to be written

- A single 32 bit status word is returned with each transfer. This status word communicates the basic state of the system back to the host PC.

Figure A1.1 shows pictorially how this SPI interface operates.

Figure A1.1 SPI control interface transfer

The 2-bit command has been included to accommodate possible future expansion of this interface beyond the basic write functionality define herein. The default command is "00" which corresponds to a write command.

# **Read Only Status Register**

This section details the bit definitions for the single read back word on the SPI2 port. This is a single 32bit register to provide feedback on the state of the system. This word is returned to the master during every 32-bit SPI write (It is therefore returned twice during a complete 64bit write access).

| Off       | fset | :: N/ | /A                 |                                                                                                                                                                                                                                                                                                                                                                              | N                 | ame            | e: ST  | ATU          | S           |             |              |             |            |             |         |       |      |          |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

|-----------|------|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------|--------------|-------------|-------------|--------------|-------------|------------|-------------|---------|-------|------|----------|-----------|------|--------------------------------------------------------------------------------------------------------|----------|----------|---|------|------|------|------------|-----------|-----|

| 31        | 30   | 29    | 82<br>OTHEI        | C<br>R ST                                                                                                                                                                                                                                                                                                                                                                    | Y<br>ATU          |                | 24     | 1 X T        | NK 22       | 51<br>TAT8  | S 20         | 19<br>RX    | LINK<br>18 | TATS        | S 16    | 15    | 14   | ATAC     | BLO<br>21 |      | OT<br>2<br>2<br>3<br>3<br>4<br>3<br>4<br>3<br>4<br>3<br>4<br>3<br>4<br>3<br>4<br>3<br>4<br>3<br>4<br>3 | 6        | 8        | 7 | 9    |      |      | m<br>REGIS | ~<br>STER | 1 0 |

| PHASE     | (    | Comr  | mand (             | Queu                                                                                                                                                                                                                                                                                                                                                                         | ue fi             | ll leve        | el     | TX_RST_DONE  | TX_RST_GT   | TX_RST_CORE | TX_SYNC      | RX_RST_DONE | RX_RST_GT  | RX_RST_CORE | RX_SYNC |       |      | TX_EMPTY | TX_ERROR  |      | RX_FULL                                                                                                | RX_EMPTY | RX_ERROR | Р | LATF | ORM  | ID   |            | VERSI     | ON  |

| Bit<br>31 | S    |       | This 0 =           | ASE<br>s bit<br>s en<br>Ado                                                                                                                                                                                                                                                                                                                                                  | t ca<br>ab<br>dre | les t<br>ss pl | nase   | aste<br>curr | r to<br>ent | con<br>(Dat | firm<br>a pł | the<br>nase | con<br>nex | nmu<br>t)   |         |       |      |          |           |      |                                                                                                        | -        |          |   |      | e ac | cess | •          |           |     |

| 30:       | 24   |       | Cor<br>The         | Command Queue Fill level. These bits indicate how many commands are in the queue waiting to be processed. To ensure the last command written has been processed. Poll address 0 until these bits return 0. TX_RST_DONE                                                                                                                                                       |                   |                |        |              |             |             |              |             |            |             |         |       |      |          |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

| 23        |      |       | TX_<br>This<br>1 = | 1 = Data phase current (Address phase next)  Command Queue Fill level.  These bits indicate how many commands are in the queue waiting to be processed.  To ensure the last command written has been processed. Poll address 0 until these bits return 0.  TX_RST_DONE  This bit indicates that the reset TX sequence is complete  1 = Complete  0 = Not Complete  TX_RST_GT |                   |                |        |              |             |             |              |             |            |             |         |       |      |          |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

| 22        |      |       | TX_<br>This<br>1 = | RST<br>s bit<br>In r                                                                                                                                                                                                                                                                                                                                                         | in<br>ese         | iT<br>dica     | tes tl | he st        | ate         | of tl       | ne T         | X tra       | ansc       | eive        | r res   | set b | oit. |          |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

| 21        |      |       | This               | s bit<br>In r                                                                                                                                                                                                                                                                                                                                                                | in<br>ese         |                | tes tl | he st        | ate         | of tl       | ne T         | X JES       | SD2(       | 04B         | core    | res   | et b | it.      |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

| 20        |      |       | TX_<br>This        | _                                                                                                                                                                                                                                                                                                                                                                            |                   | dica           | tes tl | he st        | ate         | of tl       | ne Jl        | ESD2        | 204B       | SYN         | IC ir   | nput  | to t | he t     | tran      | smit | ter                                                                                                    |          |          |   |      |      |      |            |           |     |

| 19        |      |       | This               | s bit<br>Cor                                                                                                                                                                                                                                                                                                                                                                 | in<br>np          |                | tes tl | hat t        | he r        | eset        | RX           | sequ        | uenc       | e is        | con     | nple  | te   |          |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

| 18        |      |       | RX_<br>This        | RST<br>s bit<br>In r                                                                                                                                                                                                                                                                                                                                                         | Γ_C<br>t in       | iT<br>dica     | tes tl | he st        | ate         | of tl       | ne R         | X tra       | ansc       | eive        | r re:   | set l | oit. |          |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

| 17        |      |       | RX_                | _RST<br>s bit                                                                                                                                                                                                                                                                                                                                                                | Γ_C<br>: in       | ORE<br>dica    |        | he st        | ate         | of tl       | ne R         | X JE:       | SD2(       | )4B         | core    | e res | et b | it.      |           |      |                                                                                                        |          |          |   |      |      |      |            |           |     |

Page 15 of 26

|       | 0 = Not in reset                                                           |

|-------|----------------------------------------------------------------------------|

| 16    | RX_SYNC                                                                    |

|       | This bit indicates the state of the JESD204B SYNC output from the Receiver |

| 15-14 | Unused                                                                     |

| 13    | TX_EMPTY                                                                   |

| 12    | TX_ERROR                                                                   |

| 11    | Unused                                                                     |

| 10    | RX_FULL                                                                    |

| 9     | RX_EMPTY                                                                   |

| 8     | RX_ERROR                                                                   |

| 7-4   | PLATFORM ID:                                                               |

|       | A 4 bit identifier unique per platform.                                    |

| 3:0   | VERSION                                                                    |

|       | A 4 bit version number.                                                    |

# Writeable bank addressing

The following table shows 1Mbyte bank allocations

| Bank<br>Number | Base Address | Purpose                                                                     |

|----------------|--------------|-----------------------------------------------------------------------------|

| - Number       |              |                                                                             |

| 0              | 0x00000000   | Sub-system control. This register bank is used for overall control the sub- |

|                |              | system.                                                                     |

|                |              |                                                                             |

| 1              | 0x00100000   | JESD204B receiver IP core. This register bank is used to write to the       |

|                |              | JESD204B receiver IP register interface.                                    |

|                |              |                                                                             |

| 2              | 0x00200000   | JESD204B transmitter IP core. This register bank is used to write to the    |

|                |              | JESD204B transmitter IP register interface.                                 |

|                |              |                                                                             |

# **Bank 0 Registers**

This section details the registers used to configure and control the JESD204B IP sub-system. All addresses are specified as offsets to bank 0 base address.

|                | Control Registers                                                                 |

|----------------|-----------------------------------------------------------------------------------|

| Address Offset | Description                                                                       |

| 0x0            | Poll Status:                                                                      |

|                | A write to this address updates the Status Register and does not queue a command. |

| 0x4            | RESET                                                                             |

| 0x8            | CTRL_GENERAL                                                                      |

|                | This register is for general control of the data sample block                     |

| 0x10           | CTRL_RX                                                                           |

|                | This register is for control of the RX path of the data sample block              |

| 0x14           | CNFG_RX                                                                           |

|                | This register is for configuration of the RX path of the data sample block        |

| 0x20           | CTRL_TX                                                                           |

|                | This register is for control of the TX path of the data sample block              |

| 0x24           | CNFG_TX                                                                           |

|                | This register is for configuration of the TX path of the data sample block        |

| 0x40           | CTRL_JESD                                                                         |

|                | Reset and reprogram PLL controls                                                  |

| 0x44           | CNFG_JESD_RATE                                                                    |

|                | Frequency band and clock multiplexor control register.                            |

| 0x48           | CNFG_JESD_REG1                                                                    |

|                | Mode configuration register.                                                      |

| 0x4C           | CNFG_JESD_REG2                                                                    |

|                | Transceiver parameter configuration register.                                     |

# [JESD204B TI Reference design]

April 2016 v2.8 (Vivado 2016.1)

Page 17 of 26

| Off | fset | : 0x | 4  |     | Na          | me | : RE  | SET  |     |      |       |     |       |      |       |      |      |       |          |    |    |   |   |   |   |   |   |          |   |   |            |

|-----|------|------|----|-----|-------------|----|-------|------|-----|------|-------|-----|-------|------|-------|------|------|-------|----------|----|----|---|---|---|---|---|---|----------|---|---|------------|

| 31  | 30   | 29   | 28 | 27  | 56          | 25 | 24    | 23   | 22  | 21   | 20    | 19  | 18    | 17   | 16    | 15   | 14   | 13    | 12       | 11 | 10 | 6 | 8 | 7 | 9 | 5 | 4 | 3        | 2 | 1 | 0          |

|     |      |      |    |     |             |    |       |      |     |      |       |     |       |      |       |      |      |       |          |    |    |   |   |   |   |   |   |          |   |   | ET         |

|     |      |      |    |     |             |    |       |      |     |      |       |     |       |      |       |      |      |       |          |    |    |   |   |   |   |   |   |          |   |   | SOFT RESET |

| Bit | :S   |      | Pu | rpo | se          |    |       |      |     |      |       |     |       |      |       |      |      |       |          |    |    |   |   |   |   |   |   |          |   |   |            |

| 31- | -1   | ·    | Un | use | d           |    | ·     |      |     | ·    |       |     |       | ·    |       | ·    |      |       | <u> </u> | ·  | ·  | · |   |   | · |   | · | <u> </u> |   |   |            |

| 0   |      |      |    |     | ESE<br>1 to |    | bit 1 | o fo | rce | a so | ft re | set | of th | ne M | licro | Blaz | e su | ıb-sy | /ste     | m. |    |   |   |   |   |   |   |          |   |   |            |

| set | t: 0> | κ8 |     |               | Na       | me           | : CT        | RL_                   | GEN | NER  | AL |       |       |       |      |      |       |      |     |     |       |       |      |      |      |    |   |   |   |   |             |

|-----|-------|----|-----|---------------|----------|--------------|-------------|-----------------------|-----|------|----|-------|-------|-------|------|------|-------|------|-----|-----|-------|-------|------|------|------|----|---|---|---|---|-------------|

| 31  | 30    | 29 | 28  | 27            | 26       | 25           | 24          | 23                    | 22  | 21   | 20 | 19    | 18    | 17    | 16   | 15   | 14    | 13   | 12  | 11  | 10    | 6     | 8    | 7    | 9    | 5  | 4 | 3 | 2 | 1 | 0           |

| Bit | ý     |    | Pu  | rpo           | <b>6</b> |              |             |                       |     |      |    |       |       |       |      |      |       |      |     |     |       |       |      |      |      |    |   |   |   |   | ADC_NOT_DAC |

| 31  |       |    |     | use           |          |              |             |                       |     |      |    |       |       |       |      |      |       |      |     |     |       |       |      |      |      |    |   |   |   |   |             |

| 0   |       |    | Thi | is re<br>Writ | e to     | er bi<br>JES | t co<br>D20 | ntro<br>14B T<br>2041 | X R | AM's | 5  | ion ( | of th | ie sa | ımpl | e da | ata b | lock | SPI | por | ts (S | SPI p | orts | 0 aı | nd 1 | ). |   |   |   |   |             |

# [JESD204B TI Reference design]

April 2016 v2.8 (Vivado 2016.1)

Page 18 of 26

| Of  | fset   | : 0x | 10  |        | Na    | me    | : CT  | RL_   | RX    |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

|-----|--------|------|-----|--------|-------|-------|-------|-------|-------|-------|-------|------|------|------|-------|--------|------|-------|------|-----|-------|--------|-------|------|-----|-----|------|-------|-------|----|---|

| 31  | 30     | 29   | 28  | 27     | 26    | 25    | 24    | 23    | 22    | 21    | 20    | 19   | 18   | 17   | 16    | 15     | 14   | 13    | 12   | 11  | 10    | 9      | 8     | 7    | 6   | 5   | 4    | 3     | 2     | 1  | 0 |

|     |        |      |     |        |       |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

|     |        |      |     | TORE   |       |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

|     |        |      |     | STORE  |       |       |       |       |       |       |       |      |      |      |       |        |      | FLUSH |      |     |       |        |       |      |     |     |      |       |       |    |   |

| Bit | <br>:S |      | Pu  | rpo    | se    |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

| 31  | -3     |      | Un  | use    | d     |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

| 2   |        |      | ST  | ORE    | (1)   |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

|     |        |      | 0 = | : Idle | 9     |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

|     |        |      | 1 = | Sta    | rt ca | ptu   | ring  | link  | dat   | a int | o FI  | FO's | . Da | ta w | ill b | e ca   | ptur | ed i  | nto  | the | FIFC  | o's fo | or th | e la | nes | ena | bles | in re | egist | er |   |

|     |        |      | bit | s SP   | 10 _l | LANI  | E_E1  | NA a  | nd S  | PI1   | _LA   | NE_  | ENA  |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

| 1   |        |      | FLU | JSH    | (1)   |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

|     |        |      | 0 = | No     | rmal  | l оре | erati | ion   |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

|     |        |      | 1 = | Flu    | sh th | าe R  | X pi  | pelir | ne. T | his l | bit n | nust | be l | held | unt   | il sta | atus | bit I | EX_E | EMP | TY is | s ass  | erte  | d.   |     |     |      |       |       |    |   |

| 0   |        |      | Un  | use    | d     |       |       |       |       |       |       |      |      |      |       |        |      |       |      |     |       |        |       |      |     |     |      |       |       |    |   |

### Notes:

1. You may only set one bit at any point in time and you must clear any set bits before setting another bit. (eg you cannot clear FLUSH and set STORE at the same time. You must write zero to this register to clear FLUSH before writing again to set STORE

Page 19 of 26

|     |      |       |                                         |                                               |                                                      |                                                 |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |    | -     |      |       | - (   |                  |      |       | ,      |      |       |      |       |       |               |      |      |       |               | , -  |       | _ |

|-----|------|-------|-----------------------------------------|-----------------------------------------------|------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|-------|------|-------|-------|------------------|------|-------|--------|------|-------|------|-------|-------|---------------|------|------|-------|---------------|------|-------|---|

| Of  | fset | :: 0x | 14                                      |                                               | Na                                                   | me                                              | : CN                                            | NFG <sub>.</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _RX   |    |       |      |       |       |                  |      |       |        |      |       |      |       |       |               |      |      |       |               |      |       |   |

| 31  | 30   | 29    | 28                                      | 27                                            | 26                                                   | 25                                              | 24                                              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22    | 21 | 20    | 19   | 18    | 17    | 16               | 15   | 14    | 13     | 12   | 11    | 10   | 6     | 8     | 2             | 9    | 5    | 4     | 3             | 2    | 1     | 0 |

|     |      |       |                                         |                                               |                                                      |                                                 |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |    |       |      |       |       |                  |      |       |        |      |       |      |       |       | SPI1_LANE_ENA |      |      |       | SPIO_LANE_ENA |      |       |   |

| Bit | :S   |       | Pu                                      | urpose                                        |                                                      |                                                 |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |    |       |      |       |       |                  |      |       |        |      |       |      |       |       |               |      |      |       |               |      |       |   |

| 31  | -5   |       | Un                                      | Purpose<br>Unused                             |                                                      |                                                 |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |    |       |      |       |       |                  |      |       |        |      |       |      |       |       |               |      |      |       |               |      |       |   |

| 7-4 |      |       | Ind<br>an<br>00<br>00<br>00<br>01<br>10 | divid<br>d re<br>00 =<br>01 =<br>10 =<br>00 = | ad o<br>: No<br>: land<br>: land<br>: land<br>: land | enal<br>ut v<br>lane<br>e 1 e<br>e 3 e<br>e 5 e | ole k<br>ia SI<br>es er<br>enak<br>enak<br>enak | pits for points for po | ort 1 |    |       |      | ssib  | le la | nes.             | The  | ese b | oits o | cont | rol v | vhic | h FII | FO's  | get           | ena  | bled | l for | bot           | h ca | oture | è |

| 3-0 | )    |       | Ind<br>an<br>00<br>00<br>00             | _<br>d re<br>00 =<br>01 =<br>10 =             | LANE<br>lual o<br>ad o<br>: No<br>: land<br>: land   | enal<br>ut v<br>lane<br>e 0 e<br>e 2 e          | ole k<br>ia SI<br>es er<br>enak<br>enak         | oit for<br>Pl por<br>nable<br>pled<br>pled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ort 0 |    | IO ad | cces | sible | e lan | es. <sup>-</sup> | Γhes | e bi  | ts co  | ontr | ol w  | hich | FIF   | O's { | get e         | enab | oled | for I | ooth          | cap  | ture  |   |

## Notes:

1000 = lane 6 enabled

1. After configuring the lanes to be enabled for writing to over SPI. The FIFO interface must be cleared by performing a flush using register CTRL\_RX.

Page 20 of 26

|     |      |      |    |                       |                |       |          |      |       |       | , tpiii |      | 10 V | 2.0 ( | VIVE  | ido z  | _0 10 | ,,    |      |      |       |      |       |     |     |     |      | ıαç  | JC 2 | <i>J</i> 01 |   |

|-----|------|------|----|-----------------------|----------------|-------|----------|------|-------|-------|---------|------|------|-------|-------|--------|-------|-------|------|------|-------|------|-------|-----|-----|-----|------|------|------|-------------|---|

| Of  | fset | : 0x | 20 |                       | Na             | me    | : CT     | RL_  | TX    |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

| 31  | 30   | 29   | 28 | 27                    | 26             | 25    | 24       | 23   | 22    | 21    | 20      | 19   | 18   | 17    | 16    | 15     | 14    | 13    | 12   | 11   | 10    | 6    | 8     | 7   | 9   | 5   | 4    | 3    | 2    | 1           | 0 |

|     |      |      |    | Purpose Store Purpose |                |       |          |      |       |       |         |      |      |       |       |        |       | FLUSH |      |      |       |      |       |     |     |     |      |      |      |             |   |

| Bit | is   |      | Pu | rpo                   | se             |       |          |      |       |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

| 31  | -4   |      | Un | use                   | d              |       |          |      |       |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

| 3   |      |      | PL | <b>AY (</b> :         | 1)             |       |          |      |       |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

|     |      |      | -  | : IDL                 | _              |       |          |      |       |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

|     |      |      |    |                       | able           | out   | put 1    | from | n dat | a sa  | mpl     | es b | lock | into  | ) JES | D20    | )4B   | TX c  | ore. |      |       |      |       |     |     |     |      |      |      |             |   |

| 2   |      |      |    | ORE                   |                |       |          |      |       |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

|     |      |      | -  |                       | e and          |       |          |      |       |       |         |      |      | , ,   |       |        | ı     |       |      |      |       |      |       |     |     | ı   |      |      |      |             |   |

|     |      |      |    |                       | rt st<br>r bit |       | _        |      | -     |       |         |      |      |       |       |        | be c  | aptı  | ırea | into | o tne | e KA | IVI'S | tor | tne | ane | s en | abie | s in |             |   |

| 1   |      |      |    | JSH                   |                | .S 3P | 10_      | LAIN | C_EI  | NA d  | iiiu S  | OFIL | LA   | INC_  | LINA  | 1      |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

| 1   |      |      |    |                       | (±)<br>rmal    | One   | erati    | on   |       |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

|     |      |      |    |                       | sh th          | -     |          |      | ne. T | his l | oit m   | nust | be l | neld  | unt   | il sta | itus  | bit 1 | TX E | MP   | TY is | ass  | erte  | d.  |     |     |      |      |      |             |   |

|     |      |      |    |                       |                |       | <u> </u> |      |       |       |         |      |      |       |       |        |       |       |      |      |       |      |       |     |     |     |      |      |      |             |   |

### Notes:

Unused

1. You may only set one bit at any point in time and you must clear any set bits before setting another bit. (eg you cannot clear FLUSH and set STORE at the same time. You must write zero to this register to clear FLUSH before writing again to set STORE

Page 21 of 26

| Of  | fset | :: 0x | 24                               |                                                | Na                                                  | ıme                                      | : CN                                   | IFG <sub>.</sub>                              | _TX   |      |      |       |       |     |      |       |       |       |      |      |       |       |      |     |               |      |       |        |               |      |   |

|-----|------|-------|----------------------------------|------------------------------------------------|-----------------------------------------------------|------------------------------------------|----------------------------------------|-----------------------------------------------|-------|------|------|-------|-------|-----|------|-------|-------|-------|------|------|-------|-------|------|-----|---------------|------|-------|--------|---------------|------|---|

| 31  | 30   | 29    | 28                               | 27                                             | 26                                                  | 25                                       | 24                                     | 23                                            | 22    | 21   | 20   | 19    | 18    | 17  | 16   | 15    | 14    | 13    | 12   | 11   | 10    | 6     | 8    | 7   | 9             | 5    | 4     | 3      | 2             | 1    | 0 |

|     |      |       |                                  |                                                |                                                     |                                          |                                        |                                               |       |      |      |       |       |     |      |       |       |       |      |      |       |       |      |     | SPI1_LANE_ENA | l    |       |        | SPIO_LANE_ENA |      |   |

| Bi  | ts   |       | Pu                               | Purpose                                        |                                                     |                                          |                                        |                                               |       |      |      |       |       |     |      |       |       |       |      |      |       |       |      |     |               |      |       |        |               |      |   |

| 31  | -8   |       | Un                               | Purpose Unused                                 |                                                     |                                          |                                        |                                               |       |      |      |       |       |     |      |       |       |       |      |      |       |       |      |     |               |      |       |        |               |      |   |

| 7-4 |      |       | po<br>00<br>00<br>00<br>01<br>10 | livid<br>rt 1.<br>00 =<br>01 =<br>10 =<br>00 = | No<br>lane<br>lane<br>lane                          | lane<br>e 1 e<br>e 3 e<br>e 5 e<br>e 7 e | ole b<br>es er<br>enab<br>enab<br>enab | nable<br>oled<br>oled<br>oled<br>oled<br>oled | or SP |      |      |       |       | es. | Thes | se bi | ts co | ontro | ol w | hich | ı ran | n blo | ocks | get | enal          | bled | l for | writ   | e vi          | a SP | I |

| 3-( | )    |       | po<br>00<br>00<br>00<br>01       | livid<br>rt 0<br>00 =<br>01 =<br>10 =          | LANE<br>ual e<br>: No<br>: lane<br>: lane<br>: lane | lane<br>e 0 e<br>e 2 e<br>e 4 e          | ole b<br>es er<br>enab<br>enab         | nable<br>oled<br>oled<br>oled                 |       | 10 a | cces | sible | e lan | es  | Thes | se bi | ts co | ontro | ol w | hich | ı ran | n blo | ocks | get | ena           | bled | I for | · writ | e vi          | a SP | I |

## Notes:

- 1. After selecting Pattern or Data output the PLAY bit must be set in register CTRL\_TX to enable the output.

- 2. After configuring the lanes to be enabled for writing to over SPI. The RAM interface must be cleared by performing a flush using register CTRL\_RX.

Page 22 of 26

| Of  | fset | : 0x | 40  |      | Na   | me   | : CT  | RL_   | JESI  | )    |      |      |       |       |       |      |      |       |       |       |        |      |   |   |   |   |   |   |   |       |            |

|-----|------|------|-----|------|------|------|-------|-------|-------|------|------|------|-------|-------|-------|------|------|-------|-------|-------|--------|------|---|---|---|---|---|---|---|-------|------------|

| 31  | 30   | 29   | 28  | 27   | 26   | 25   | 24    | 23    | 22    | 21   | 20   | 19   | 18    | 17    | 16    | 15   | 14   | 13    | 12    | 11    | 10     | 6    | 8 | 7 | 9 | 5 | 4 | 3 | 2 | 1     | 0          |

|     |      |      |     |      |      |      |       |       |       |      |      |      |       |       |       |      |      |       |       |       |        |      |   |   |   |   |   |   |   |       |            |

|     |      |      |     |      |      |      |       |       |       |      |      |      |       |       |       |      |      |       |       | ESET  |        |      |   |   |   |   |   |   |   |       |            |

|     |      |      |     |      |      |      |       |       |       |      |      |      |       |       |       |      |      |       |       |       |        |      |   |   |   |   |   |   |   | DRPGO | JESD_RESET |

| Bit | :S   |      | Pu  | rpo  | se   |      |       |       |       |      |      |      |       |       |       |      |      |       |       |       |        |      |   |   |   |   |   |   |   |       |            |

| 31  | -2   |      |     | use  |      |      |       |       |       |      |      |      |       |       |       |      |      |       |       |       |        |      |   |   |   |   |   |   |   |       |            |

| 1   |      |      | DR  | PGC  | ):   |      |       |       |       |      |      |      |       |       |       |      |      |       |       |       |        |      |   |   |   |   |   |   |   |       |            |

|     |      |      | Wr  | ite  | 1 to | this | bit t | to in | itiat | e re | prog | gram | nmir  | ig of | the   | line | rat  | e se  | tting | gs (1 | .)(2)  | (3). |   |   |   |   |   |   |   |       |            |

| 0   |      |      | JES | SD_F | RESE | T:   |       |       |       |      |      |      |       |       |       |      |      |       |       |       |        |      |   |   |   |   |   |   |   |       |            |

|     |      |      | Wr  | ite  | 1 to | this | bit p | put t | the J | ESD  | 204  | cor  | es ai | าd tl | he tr | ans  | ceiv | ers i | nto   | rese  | et sta | ate. |   |   |   |   |   |   |   |       |            |

#### Notes:

- 1. Registers CNFG\_JESD\_RATE, CNFG\_JESD\_REG1 and CNFG\_JESD2 must be set before setting this bit.

- 2. JESD\_RESET must be asserted before and while this bit is set.

- 3. Full setup process is as follows:

- Assert JESD\_RESET

- Program CNFG\_JESD\_RATE, CNFG\_JESD\_REG1 and CNFG\_JESD2.

- Program RX core via BANK 1 or TX core registers via BANK 2

- Assert DRPGO, with JESD\_RESET still asserted.

- Clear JESD\_RESET.

- Verify TX or RX \_RST\_DONE and \_SYNC.

Now the DATA\_BLOCK may be used.

Page 23 of 26

|        |      | April 2010 V2.0 (VIVado 2010.1) Fage 25 0                                                                     |                  |                                                                                                                                                          |      |      |       |      |       |        |        |       |       | 01 20 |          |      |    |      |     |      |       |      |     |      |      |     |          |       |  |  |

|--------|------|---------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|-------|--------|--------|-------|-------|-------|----------|------|----|------|-----|------|-------|------|-----|------|------|-----|----------|-------|--|--|

| Ot     | fset | et: 0x44 Name: CNFG_JESD_RATE                                                                                 |                  |                                                                                                                                                          |      |      |       |      |       |        |        |       |       |       |          |      |    |      |     |      |       |      |     |      |      |     |          |       |  |  |

| 31     | 30   | 29                                                                                                            | 28               | 28<br>26<br>27<br>28<br>28<br>28<br>28<br>28<br>28<br>29<br>20<br>20<br>20<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21 |      |      |       |      |       |        |        |       | 7 4   |       | 2        | 1 0  |    |      |     |      |       |      |     |      |      |     |          |       |  |  |

| BYPASS |      |                                                                                                               |                  |                                                                                                                                                          |      |      |       |      |       |        |        |       |       |       | DIV4_CLK |      |    |      |     |      |       |      |     |      | RAND |     | SUB BAND |       |  |  |

| Bi     | ts   |                                                                                                               | Purpose          |                                                                                                                                                          |      |      |       |      |       |        |        |       |       |       |          |      |    |      |     |      |       |      |     |      |      |     |          |       |  |  |

| 31     |      | BYPASS:                                                                                                       |                  |                                                                                                                                                          |      |      |       |      |       |        |        |       |       |       |          |      |    |      |     |      |       |      |     |      |      |     |          |       |  |  |

|        |      | Must be set to zero.                                                                                          |                  |                                                                                                                                                          |      |      |       |      |       |        |        |       |       |       |          |      |    |      |     |      |       |      |     |      |      |     |          |       |  |  |

|        | -17  |                                                                                                               | _                | iuse                                                                                                                                                     |      |      |       |      |       |        |        |       |       |       |          |      |    |      |     |      |       |      |     |      |      |     |          |       |  |  |

| 16     |      |                                                                                                               |                  | _                                                                                                                                                        | CLK: |      |       |      |       |        |        |       |       |       |          |      |    |      |     |      |       |      |     |      |      |     |          |       |  |  |