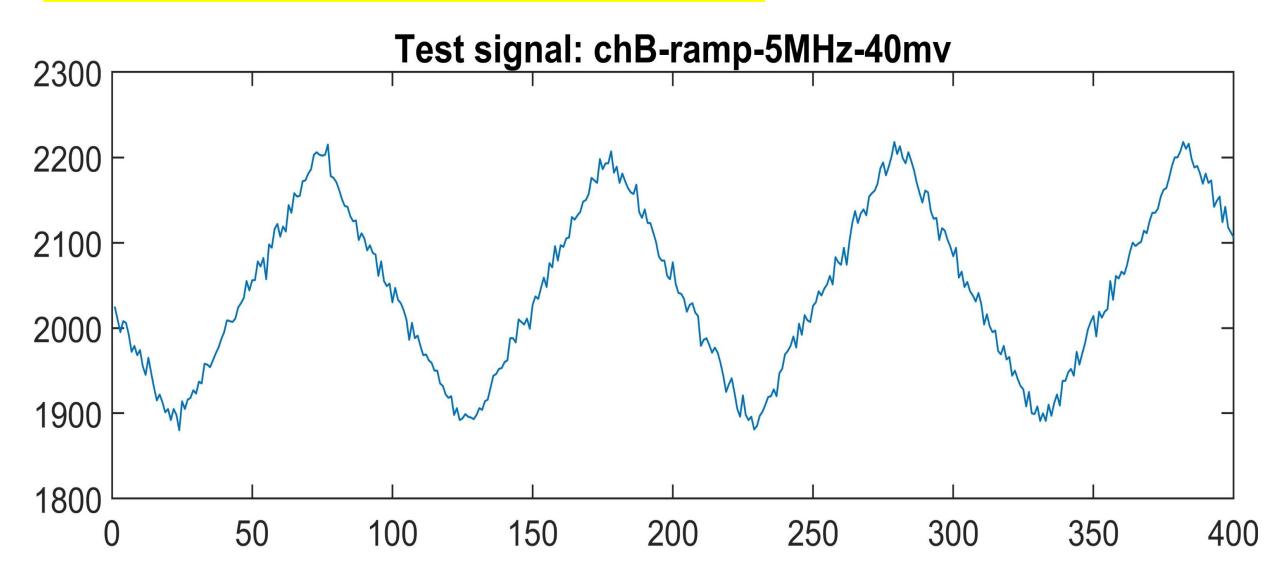

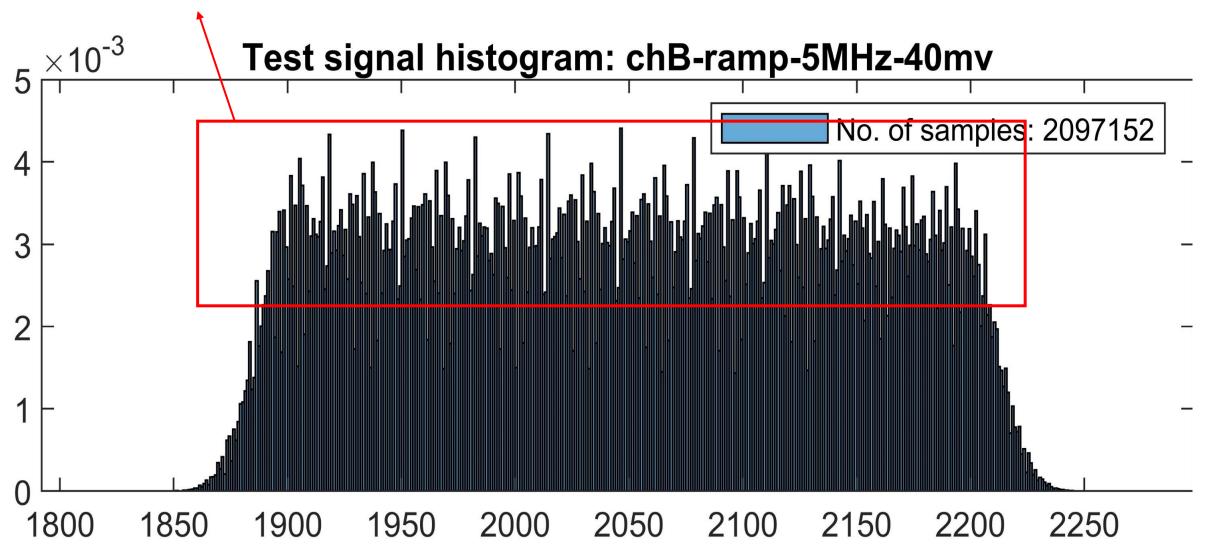

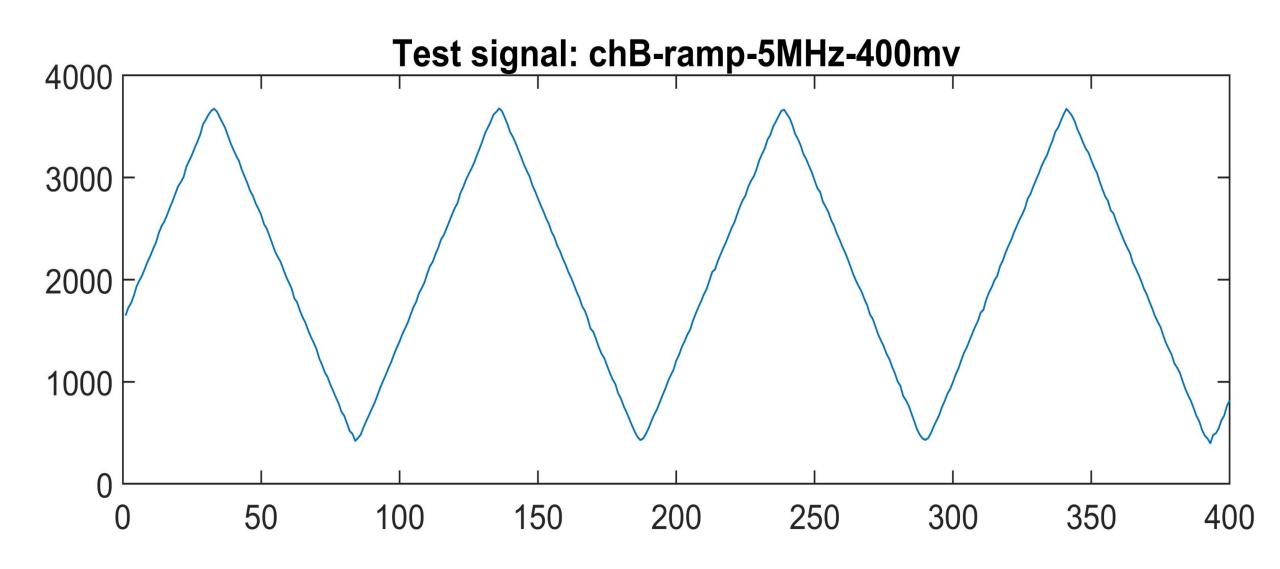

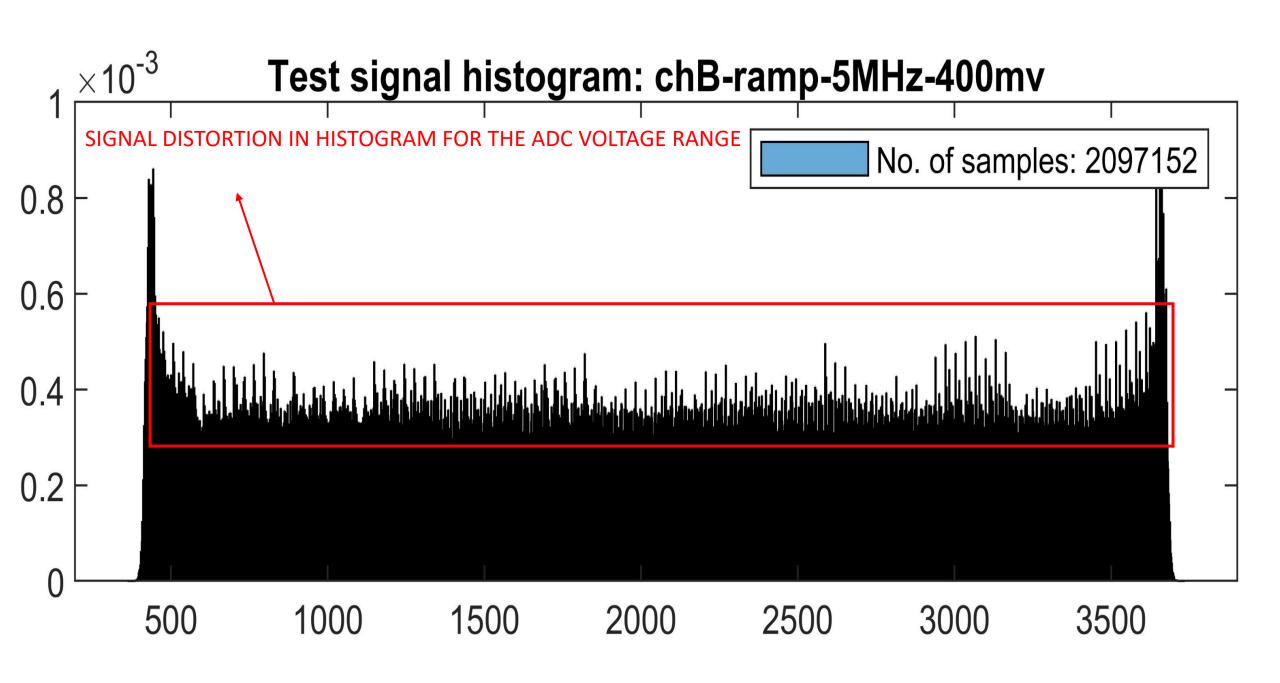

## **SECTION A: EXPERIMENTS DONE (1. RAMP SIGNAL AS INPUT with 40mV)**

#### SIGNAL DISTORTION IN HISTOGRAM FOR THE ADC VOLTAGE RANGE

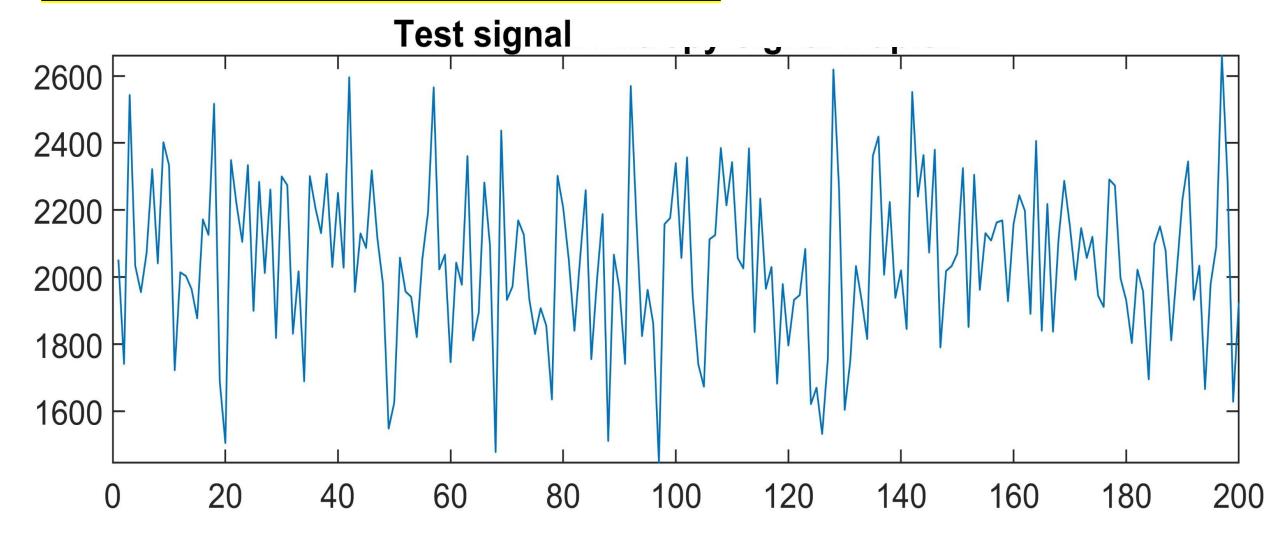

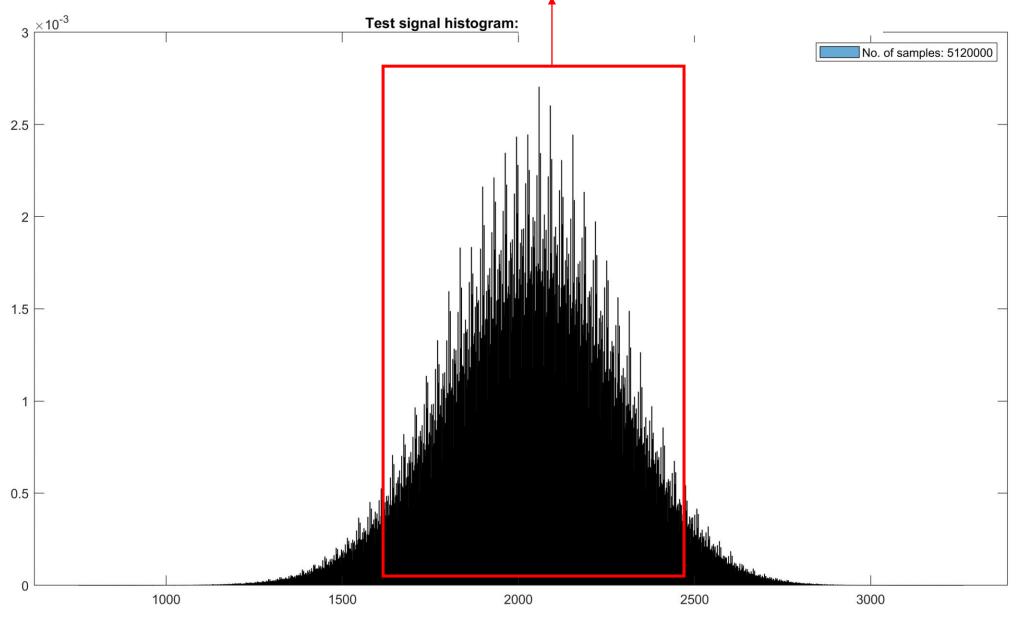

# **SECTION A: EXPERIMENTS DONE (3. WHITE NOISE SIGNAL AS INPUT)**

# SIGNAL DISTORTION IN HISTOGRAM FOR THE ADC VOLTAGE RANGE

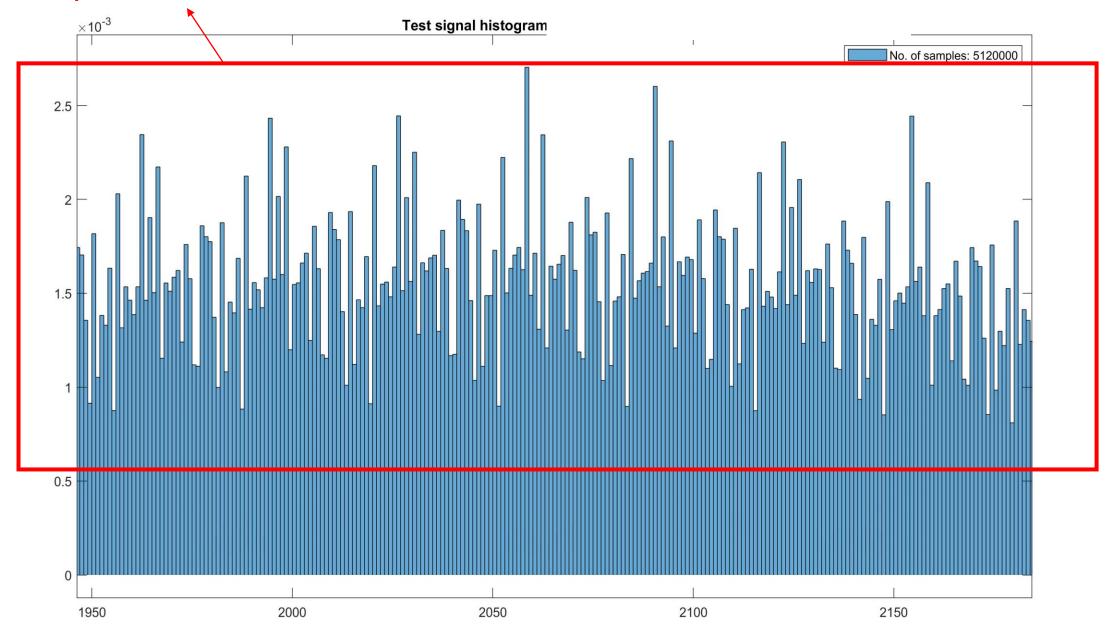

# **Zoomed-in picture of the distortion observed**

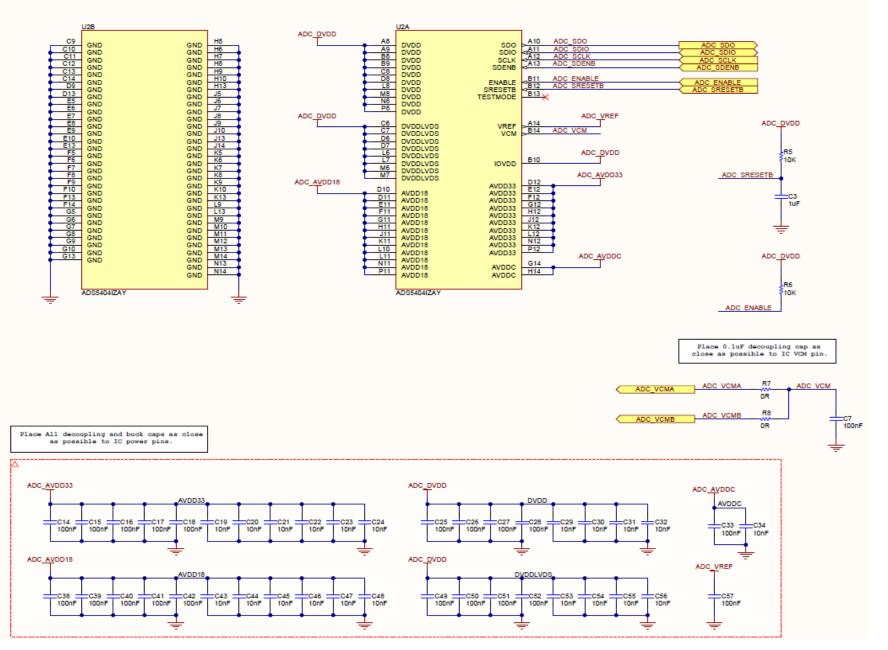

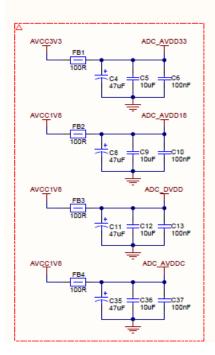

### ADS540x\_Part2

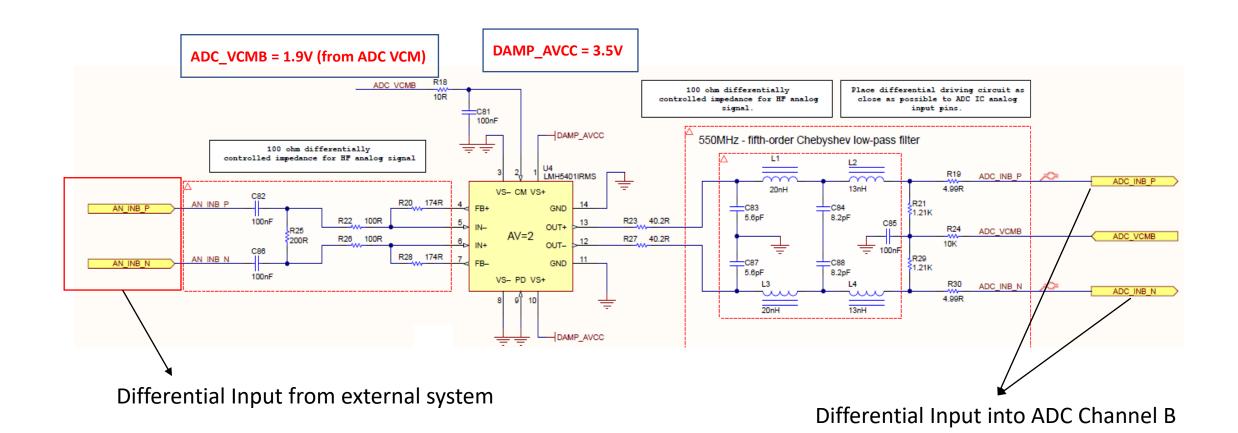

### **SECTION C: ADC INPUT DIFFERENTIAL DRIVER CIRCUIT**

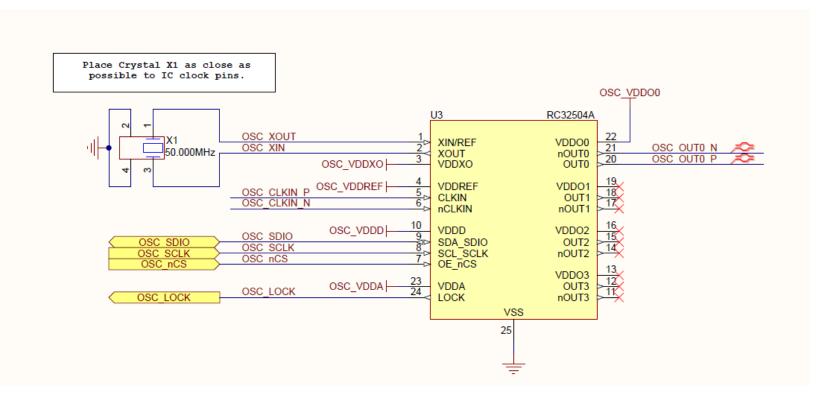

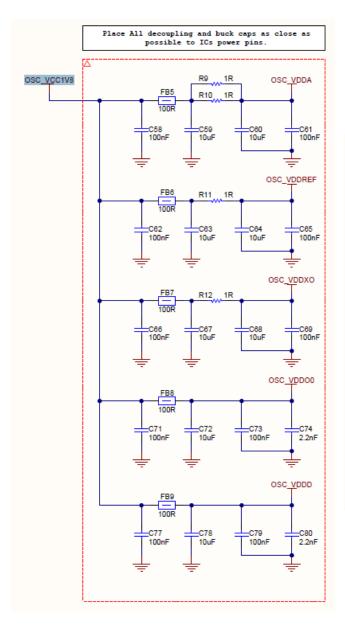

### **SECTION D: ADC CLOCK GENERATOR CIRCUIT**

OSC\_VCC1V8 is generated from a separate high PSRR LDO and not shared with ADC. However, shares a common ground with the ADC.