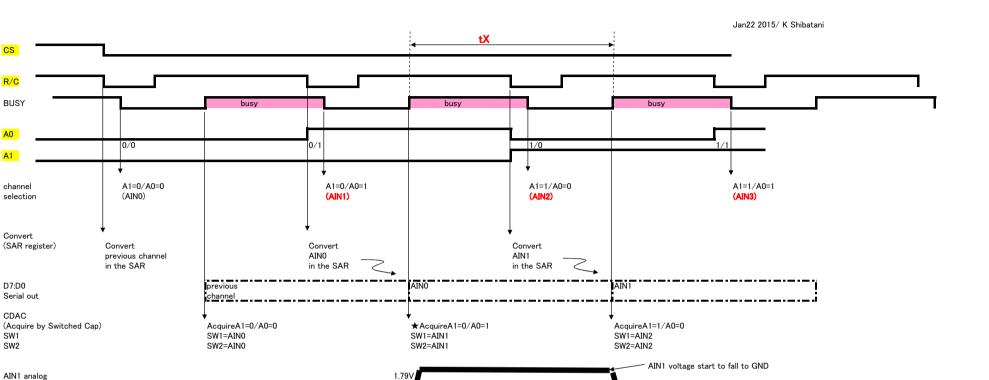

approx 30mV if 0.1uF are at

the AIN1 input

\*

edge of BUSY

## Question1

BUSY

A0

channel

selection

Convert

D7:D0 Serial out

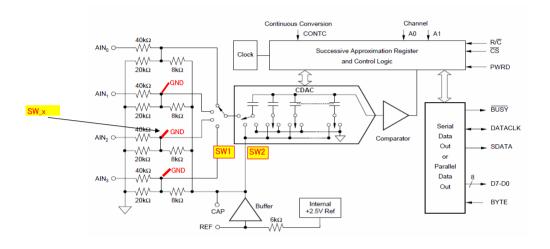

CDAC

SW1

SW2

voltage if input is Open (dashed line : with input cap)

Is the timing diagram above correct? ( Thank you for your answer to seishin)

## Question2

My understanding is CDAC acquire the analog voltage of AIN1 when SW1=SW2=AIN1.

In this time, customer's concern is voltage rise depend on input cap...

Does ADS7825 acquire the voltage just at the edge of BUSY goes UP? ( No concern about the A/D conversion result even though we can see the rise of analog voltage....Is it correct?)

## Qestion3

From Customer's test result, AIN1 analog voltage start to fall to 62mV ( seishin's thread) when they had selct AIN2. In this time, SW1/SW2 swtitches from AIN1 to AIN2..... Here is the question,,

Don't you have any additional switch ( SW x) who discharges the parastinc cap to ground in front of the SW1 ,, do you?

Question4 If the mechanism above were corret, analog voltage on AIN\_x pin goes up unless there are big (uF order ) cap, Or, Opeamp which has sink current ability and also the time Tx (above ) is short... how do you think ?