# **DAC56x2 EVM Test Procedure**

Test Plan # 56x2 Version 2.0

1 July, 2017

# **Revision History:**

| Version | Date            | Change                                 |

|---------|-----------------|----------------------------------------|

| 1.1     | Oct 10<br>2014  | Updated to use TSW1400+HSDC Pro vs HFS |

| 2.0     | June 25<br>2017 | Added harness interface                |

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied upon is current.

All test equipment used for production testing of the DAC56X2 EVM shall be current calibrated equipment.

Copyright ©2000 Texas Instruments Incorporated

#### **DAC56X2 EVM Test Procedure**

The DAC56X2 is an 12/14 bit digital-to-analog converter (DAC) which operates at a maximum sampling rate of 200MSPS. This procedure outlines the necessary tests and adjustments that must be performed by the manufacturer in order to confirm that the EVM is functioning properly.

#### NOTE:

This test procedure should be read in conjunction with the DAC56X2 EVM manual, which contains the user, notes for the EVM, as well as schematics, bill-of-material (BOM) information and PCB layout drawings. This information is not repeated in this document

### Recommended test equipment

In Table 1 is a list of the test equipment required to test the DAC56X2 EVM. Equipment other than the recommended model may be used if it satisfies the specification listed in Table 1.

**Table 1: Test equipment**

| Equipment required             | Signals/functionality required                                                         |

|--------------------------------|----------------------------------------------------------------------------------------|

| Spectrum Analyzer              | Rohde & Schwarz, 20Hz-3.5GHz<br>FSEA30                                                 |

| HPE3631A Power supply          | 0 – 5VDC, 7mV-30V dc, 0.1mV accuracy and resolution                                    |

| DMM                            | 4 ½ digit resolution                                                                   |

| Synthesized Signal Generator   | HP 8644B                                                                               |

| Jumper cables                  | 4 Banana jack to banana jack cables,<br>2 SMA cable assemblies<br>14 SMA to IDC cables |

| Pulse Generator                | Agilent 8133A                                                                          |

| Harness                        | Custom 28 pin harness                                                                  |

| Digital Test Pattern Generator | TSW1400+HSDC Pro                                                                       |

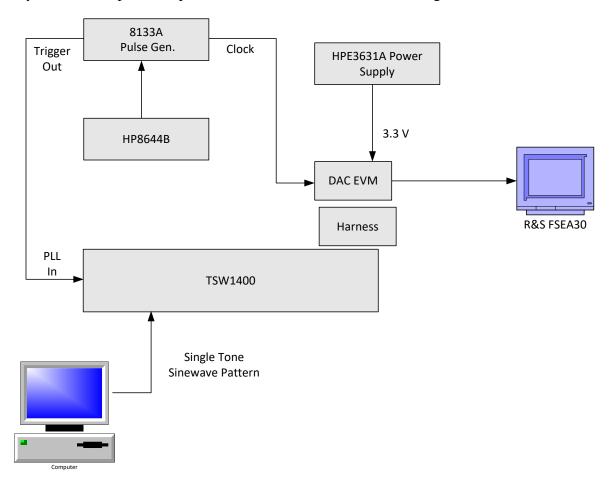

### **DAC56X2 EVM Test Set-up**

The operator shall perform the following steps:

- 1. With the DC power supply turned off, using a handheld DVM set to measure resistance, verify that there is no short between VA (J12) and GND (J14) and VB (J13) and GND (J15).

- 2. By using jumpers and 0 ohm resistors, the DAC56x2 EVM can be set up in a variety of configurations to accommodate a specific mode of operation. Verify that the following components are not installed:

R9-R12, R14-R16 R18 R19 R24-R26, R28 and R29 C7, C8, C18, C20 and C21 J4-J8

3. Verify all installed jumper settings against table 2 Jumper Positions.

| Jumper | Position       |

|--------|----------------|

| W1     | Installed      |

| W2     | Installed      |

| W9     | Removed        |

| J11    | Pins 2 and 3   |

| J11    | Pins 4 and 5   |

| J11    | Pins 10 and 11 |

**Table 2: Jumper Positions**

- 4. Set DC power supply to read +3.3V at the output terminals. Connect the positive output of the power supply to J12 and J13 and the minus output to J14 of the EVM.

- 5. Switch the power supply on.

- 6. Set the HP 8644B to output a 150mV, 100 MHz sinewave (or 100MHz around 6dBm). Connect this signal to the external input connector of the Agilent 8133A pulse generator.

- 7. Enable the trigger output of the 8133A and set the amplitude to **1.5 volts** and the divide factor to "1". Connect this signal to the J7 CMOS CLOCK input of the TSW1400- this will provide clock source to drive the TSW1400 pattern generator.

- 8. Enable the pulse output of the 8133A and set its amplitude to 3.0V and offset to 1.5V. Connect this signal to J3 on the EVM. This is the DAC56x2 input clock. Check 3.3V supply current should be about 100mA.

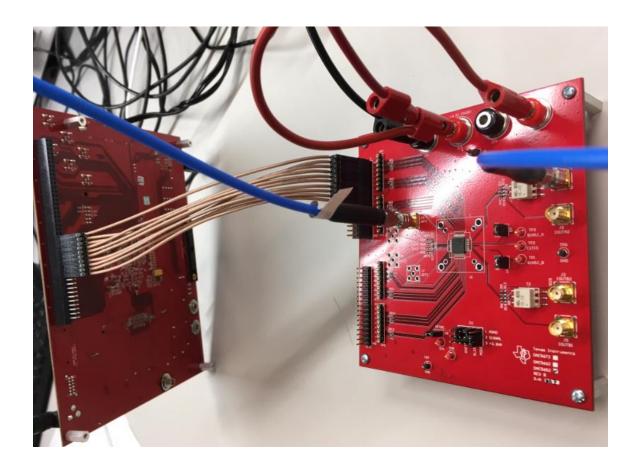

- 9. Connect the custom harness between the DAC EVM to the TSW1400 CMOS connector using the test harness as shown below. The harness should connect pin 47 and 48 on the TSW1400 to pins 1 and 2 of connector J9 on the DAC EVM. Pins 73 and 74 of the TSW1400 should connect to pins 27 and 28 of the DAC EVM.

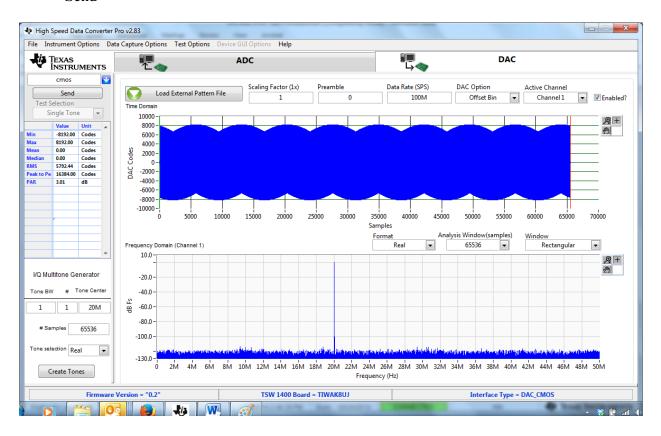

## 10. Start HSDC Pro and configure the DAC as follows

- cmos

- Data rate 100M

- DAC Option Offset Bin

- Pattern Generation

- o 1 tone BW, 1 tone, 20M center

- Create Tones

- Send

11. Connect an SMA cable from J1 (Channel A) of the EVM to the input of the Spectrum Analyzer. The complete setup should look as the one shown in the figure below:

- 12. Adjust the spectrum analyzer to measure SFDR:

- Adjust the start and stop frequencies so as to cover the first Nyquist zone (0-50 MHz)

- Go to the coupling menu and change the resolution bandwidth to 3 kHz

- Activate markers and search for peak

- Note peak value and adjust the reference level so that tone is maximum but not clipped

- Lower the noise floor by increasing the internal attenuation value and lowering the resolution bandwidth (make sure an overload warning is not shown) until a clear spur is seen on the FSEA30

- Activate a delta marker to this spur and note the measurement. The spectrum should look similar to the figure below:

7

Typical settings: Ref 0dBm, Atten 20dB, RBW 3kHz, VBW 3kHz

13. The value should read better than the values shown below. If the reading is below spec by 5 dB or more adjust the output pulse delay on the 8133A by steps of 1ns until the value improves.

DAC5652EVM 70dB DAC5662EVM 73dB DAC5672EVM 75dB

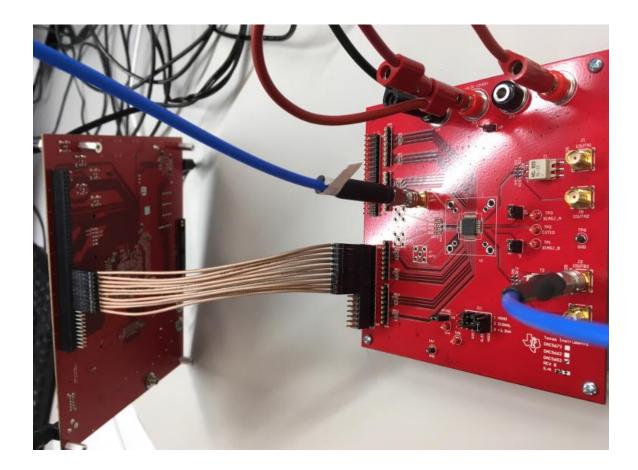

14. Repeat Channel B by connection the spectrum analyzer to J2 and moving the harness from J9 to J10 on the DAC EVM as shown below.

15. Switch the power supply off. All tests completed.

16. End of test.

# **ALL Tests Completed**