# High Speed Data Converter Pro GUI

## **ABSTRACT**

This document outlines the High-Speed Data Converter Pro Graphical User Interface (HSDC Pro GUI). Instructions for software start up and the user interface are included. Operating procedures for ADC data capture software and TSW14xxx pattern generation are also provided along with functional descriptions of the TSW1400, TSW1405, TSW1450, and TSW14J5x capture cards.

# **Table of Contents**

| 1 Introduction                                                                  |    |

|---------------------------------------------------------------------------------|----|

| 2 Software Start up                                                             |    |

| 2.1 Installation Instructions                                                   |    |

| 2.2 USB Interface and Drivers                                                   |    |

| 2.3 Device ini Files                                                            | 1  |

| 3 User Interface                                                                |    |

| 3.1 Toolbar                                                                     |    |

| 3.2 Status Windows                                                              | .7 |

| 3.3 Mode Selection                                                              |    |

| 3.4 Device Selection                                                            |    |

| 3.5 Capture Button (ADC Mode Only)                                              | 3  |

| 3.6 Test Selection (ADC Mode only)                                              | 3  |

| 3.7 DAC Display Panel (DAC Mode only)                                           |    |

| 3.8 I/Q Multi-Tone Generator                                                    |    |

| 4 ADC Data Capture Software Operation                                           | 4  |

| 4.1 Testing a TSW1400 EVM with an ADS5281 EVM                                   | 4  |

| 4.2 Testing a TSW1400EVM with an ADS62P49EVM (CMOS Interface)                   | 4  |

| 5 TSW1400 Pattern Generator Operation                                           | 4  |

| 5.1 Testing a TSW1400 EVM with a DAC3152 EVM                                    | 4  |

| 5.2 Loading DAC Firmware                                                        | 4  |

| 5.3 Configuring TSW1400 for Pattern Generation                                  | 4  |

| 5.4 Testing a TSW1400 EVM with a DAC5688EVM (CMOS Interface)                    | 5  |

| 6 TSW1405 Functional Description                                                | 54 |

| 6.1 Software Operation                                                          | 5  |

| 7 TSW1406 Functional Description                                                | 5  |

| 7.1 Software Operation                                                          | 5  |

| 8 TSW14J58 Functional Description                                               |    |

| 8.1 Testing the TSW14J58 EVM with an ADC12DJ3200 EVM                            | 60 |

| 9 TSW14J57 Functional Description                                               |    |

| 9.1 Testing the TSW14J57 EVM with an ADC34J45 EVM                               | 6  |

| 10 TSW14J56 Functional Description                                              |    |

| 10.1 Testing the TSW14J56 EVM with an ADC34J45 EVM                              | 6  |

| 11 TSW14J50 Functional Description                                              |    |

| 11.1 Device Selection                                                           | 7: |

| 12 TSW14J10 Functional Description                                              | 74 |

| 12.1 DAC and ADC GUI Configuration File Changes When Using a Xilinx Development |    |

| 12.2 DAC38J84EVM GUI Setup Example                                              | 79 |

| A Signal Processing in High Speed Data Converter Pro                            |    |

| A.1 Introduction                                                                |    |

| A.2 FFT Calculation from Time Domain Data                                       |    |

| A.3 FFT Filtering                                                               | 79 |

| A.4 Single Tone Parameters                                                      | 8  |

| A.5 Fundamental Power                                                           |    |

|                   | INSTRUM |

|-------------------|---------|

| Table of Contents | WW      |

| A.6 Two Tone Parameters                                                     |                 |

|-----------------------------------------------------------------------------|-----------------|

| A.7 Average FFT Calculation                                                 |                 |

| A.8 NSD Calculation                                                         | 82              |

| B Revision History                                                          | 83              |

| C Revision History                                                          | 86              |

| -                                                                           |                 |

| List of Figures                                                             |                 |

| Figure 2-1. TSW14xxx EVM Serial Number                                      | 7               |

| Figure 2-1. TSW 14XXX EVM Serial Number                                     |                 |

| Figure 2-2. Firmware Does Not Match the Device Selected                     |                 |

| Figure 2-3. TSW14xxx EVM GUI Top Level                                      |                 |

| Figure 2-4. Connecting GUI to EVM                                           |                 |

| Figure 2-5. Hardware Device Manager                                         |                 |

| Figure 2-6. Cypress FX3 USB Streamer Example Device in USB Controllers      |                 |

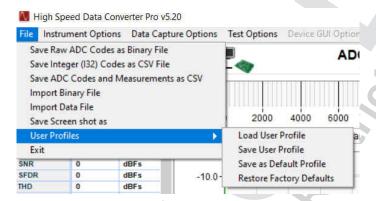

| Figure 3-1. File Tab Options                                                |                 |

| Figure 3-2. User Profiles                                                   |                 |

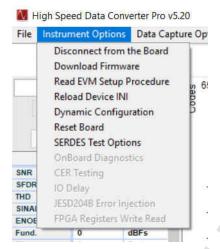

| Figure 3-3. Instrument Options                                              |                 |

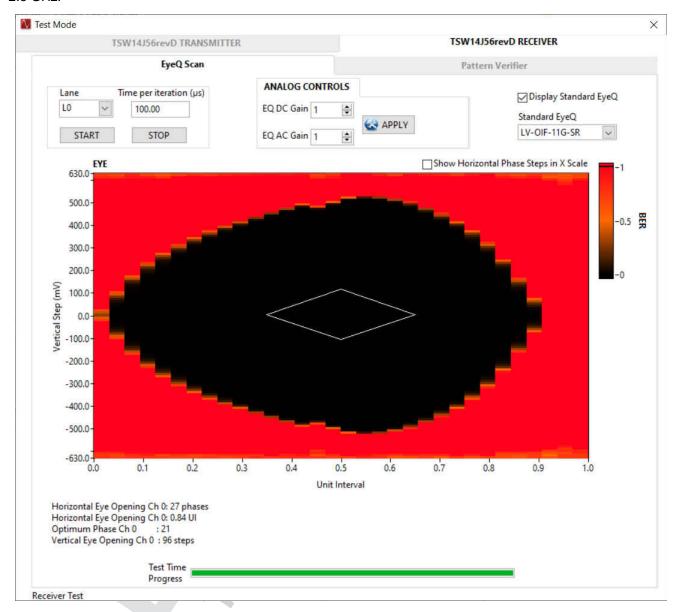

| Figure 3-4. Example Eye Diagram Plot                                        |                 |

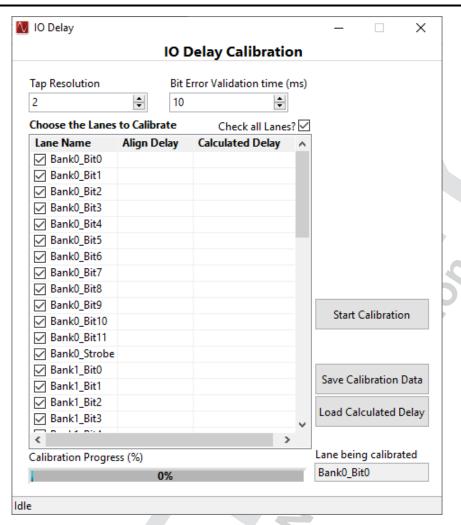

| Figure 3-5. IO Delay Calibration                                            |                 |

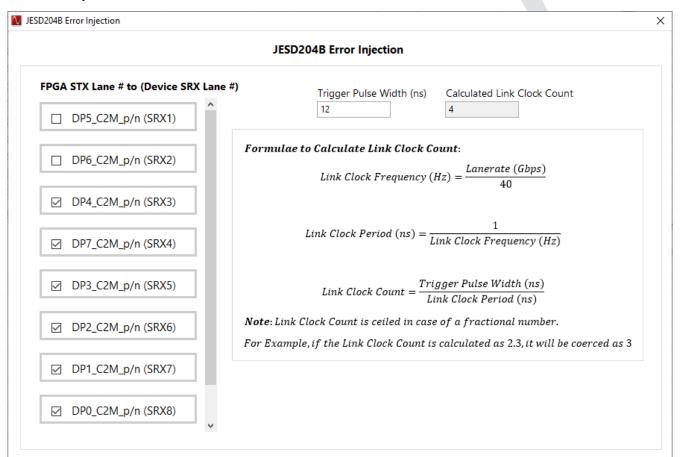

| Figure 3-6. JESD204B Error Injection Window                                 | 16              |

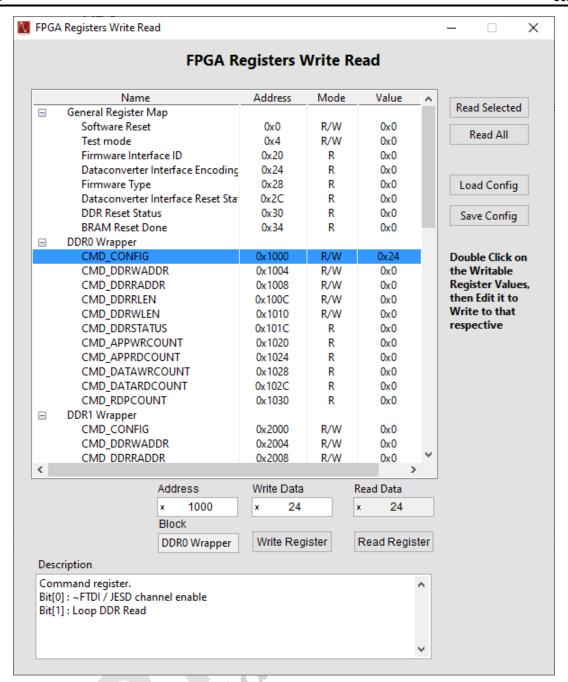

| Figure 3-7. FPGA Registers Write Read Window                                | 17              |

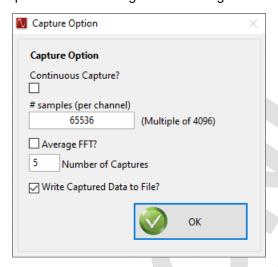

| Figure 3-8. Capture Option                                                  | 18              |

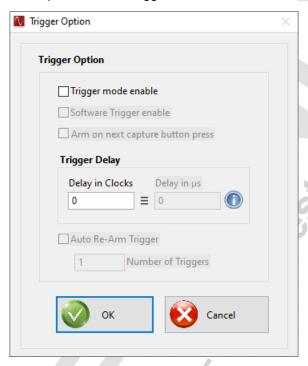

| Figure 3-9. Trigger Option                                                  | 19              |

| Figure 3-10. Auto Re-Arm Trigger Status Window                              | 20              |

| Figure 3-11. Two TSW14J56 EVM's Connected to one PC                         |                 |

| Figure 3-12. Slave Trigger Setup                                            | <mark>22</mark> |

| Figure 3-13. Master Trigger Setup                                           |                 |

| Figure 3-14. Trigger Confirmation Window                                    |                 |

| Figure 3-15. Sysref-Based Master Slave Triggering INI Setting               |                 |

| Figure 3-16. Test Options.                                                  |                 |

| Figure 3-17. Notch Frequency Bin Removal                                    |                 |

| Figure 3-18. Two Channel Display                                            |                 |

| Figure 3-19. Analysis Window Marker Example                                 |                 |

| Figure 3-20. Other Frequency Options Menu                                   |                 |

| Figure 3-21. Code Histogram                                                 |                 |

| Figure 3-22. Status Window                                                  |                 |

| Figure 3-23. Center Status Window                                           |                 |

| Figure 3-24. TSW1400 and TSW14J5x Modes                                     |                 |

| Figure 3-25. ADC Device Selection Window                                    | 31              |

| Figure 3-26. Test Selection Drop-Down Options                               |                 |

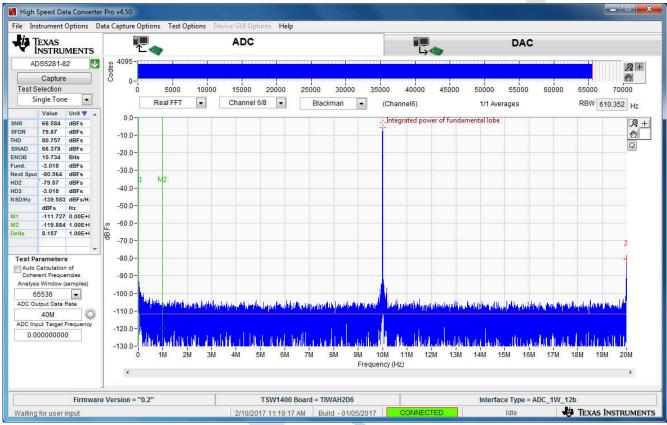

| Figure 3-27. Single Tone FFT Display                                        |                 |

| Figure 3-28. Test Parameters                                                |                 |

| Figure 3-29. Additional Device Parameters                                   |                 |

|                                                                             |                 |

| Figure 3-30. Data Display Options                                           |                 |

| Figure 3-31. Channel Selection Window                                       |                 |

| Figure 3-32. Data Windowing Options                                         |                 |

| Figure 3-33. Unit Selection.                                                | 30              |

| Figure 3-34. ADC 2nd Input Frequency Box                                    |                 |

| Figure 3-35. Three Channel Power Measurement Example                        |                 |

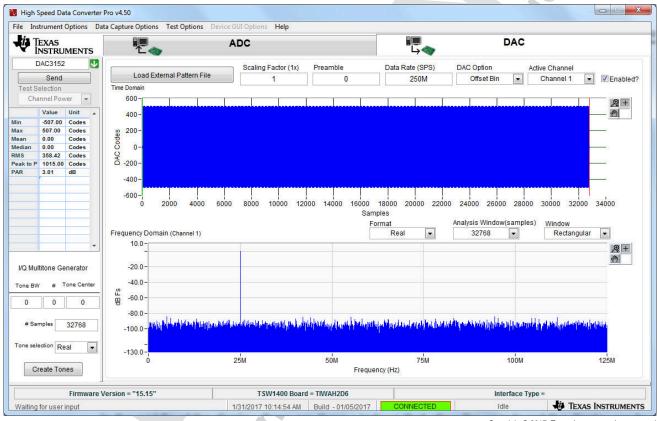

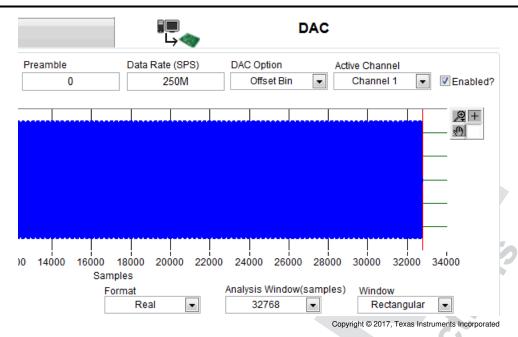

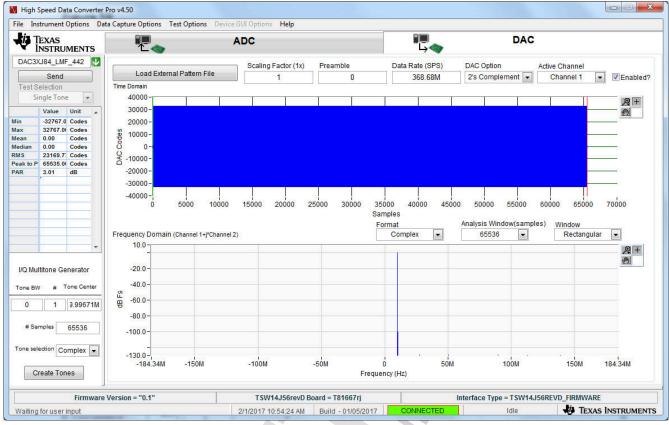

| Figure 3-36. DAC Display Mode                                               | 39              |

| Figure 3-37. DAC Test Pattern Display                                       |                 |

| Figure 3-38. Display Mode Options                                           |                 |

| Figure 4-1. TSW1400EVM interfacing to an ADS5281 EVM                        |                 |

| Figure 4-2. ADC5281 Single Tone FFT Capture Results                         |                 |

| Figure 4-3. Devices Supported with Current Firmware Loaded                  |                 |

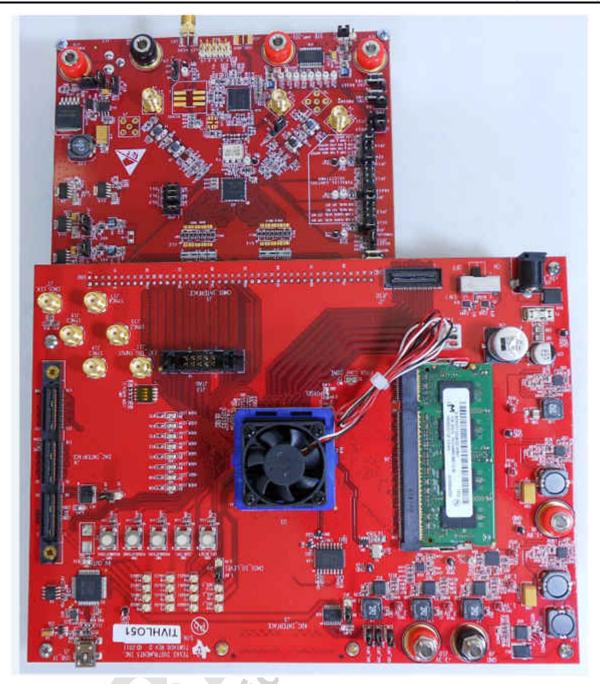

| Figure 4-4. TSW1400EVM interfacing to the CMOS connectors of an ADS62P49EVM |                 |

| Figure 4-5. TSW1400EVM Captured Results from ADS62P49EVM                    |                 |

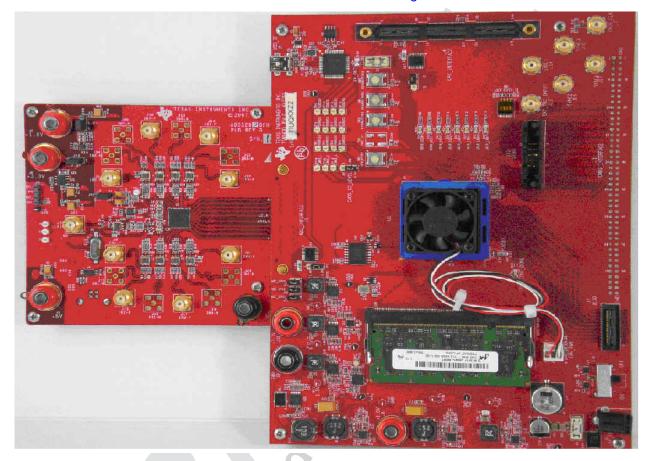

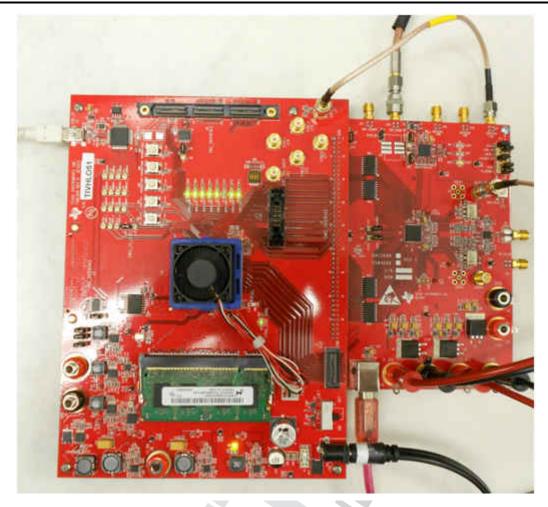

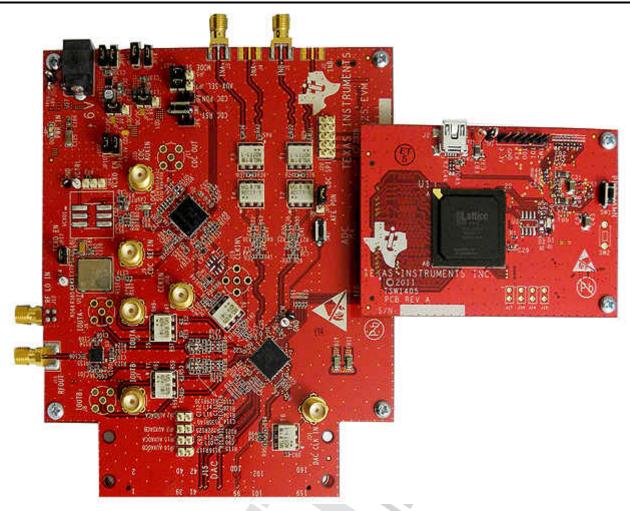

| Figure 5-1. TSW1400 EVM Interfacing to a DAC EVM                            |                 |

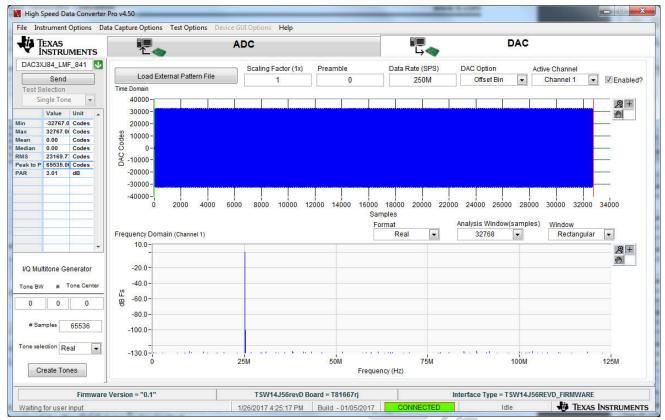

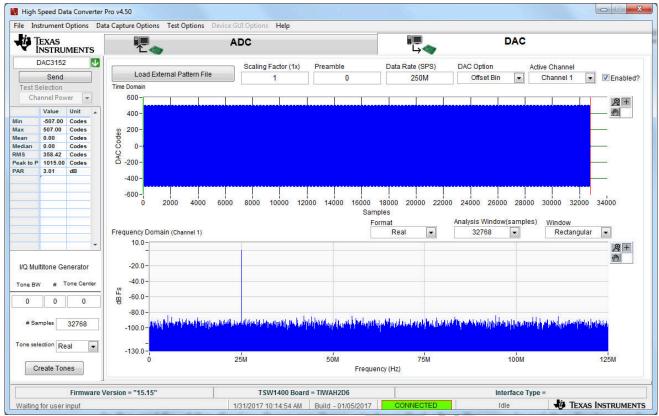

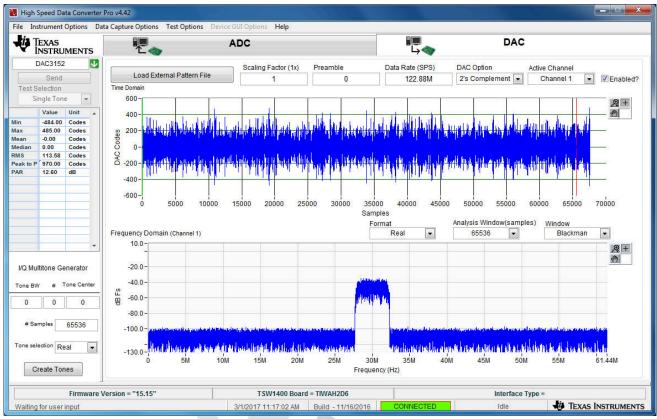

| Figure 5-2. TSW14xxxEVM GUI DAC Mode Top Level                              | 48              |

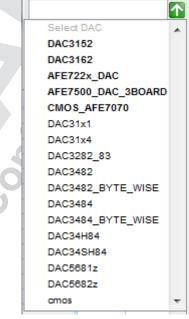

| Figure 5-3. DAC Selection                                                   |                 |

| Figure 5-4. TSW1400 Output Data to DAC EVM                                  |                 |

| Figure 5-5. TSW1400EVM Interfacing to the CMOS Connectors of a DAC5688EVM   |                 |

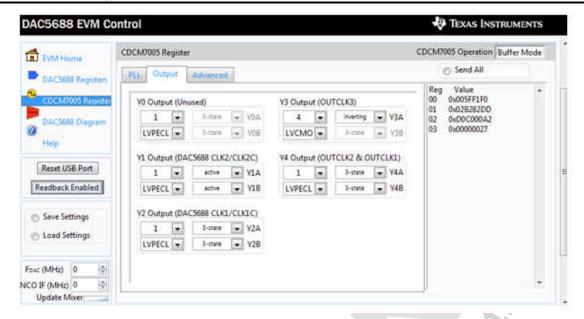

| Figure 5-6. CDCM7005 Tab on DAC5688 GUI                                     |                 |

| Figure 5-7. GUI After Test File Loaded                                      | 53              |

|                                                                             |                 |

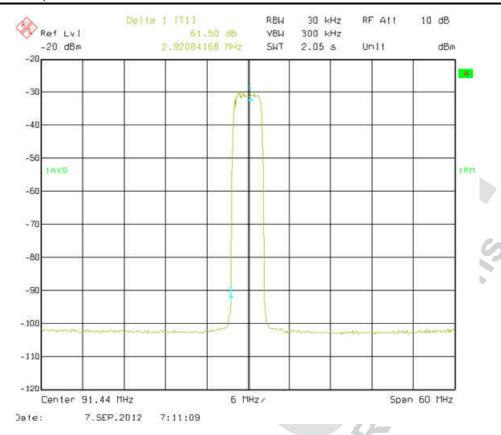

Trademarks

| Figure 5-8. DAC5688 IF Output                                                       | 54              |

|-------------------------------------------------------------------------------------|-----------------|

| Figure 6-1. TSW1405 EVM Connected to the ADC Output of the AFE7225 EVM              | <u>55</u>       |

| Figure 6-2. Number of Channels Selection                                            |                 |

| Figure 7-1. TSW1406 EVM Connected to the DAC input of the AFE7225 EVM               |                 |

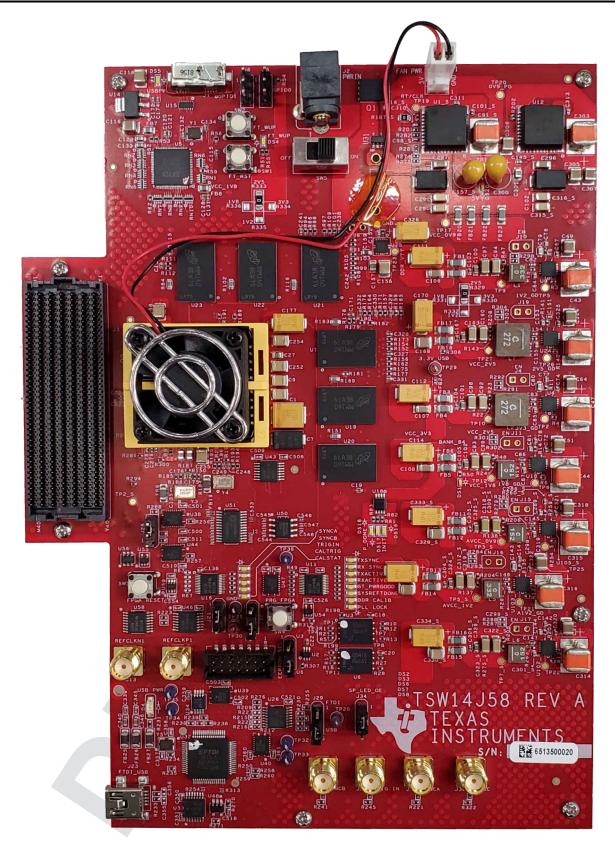

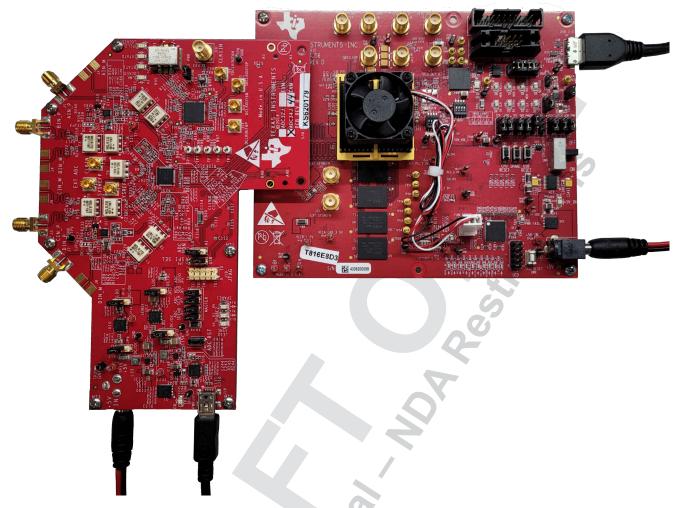

| Figure 8-1. TSW14J58 EVM                                                            |                 |

| Figure 8-2. TSW14J58 EVM connected to an ADC12DJ3200 EVM                            | 60              |

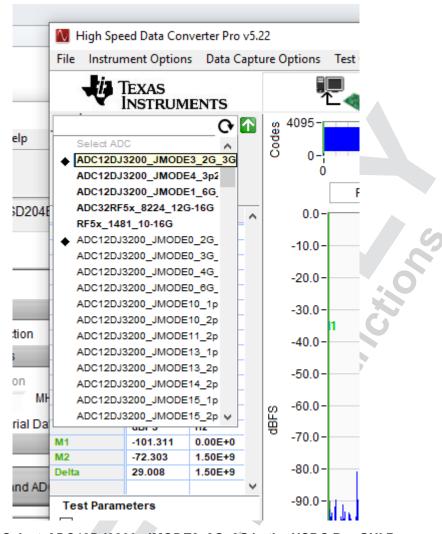

| Figure 8-3. Select ADC12DJ3200_JMODE3_2G_3G in the HSDC Pro GUI Program             |                 |

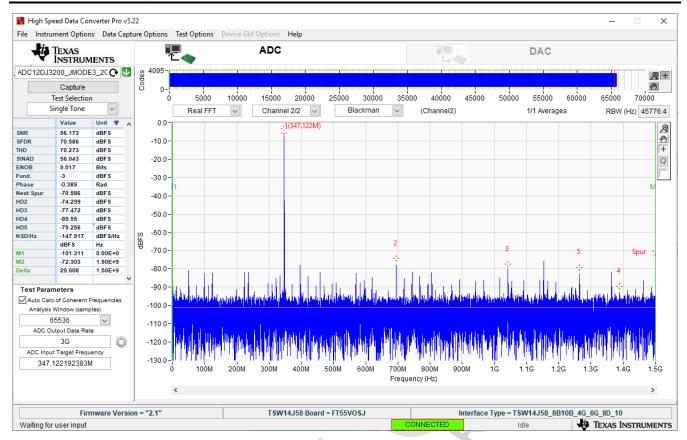

| Figure 8-4. ADC12DJ3200 Operating in JMODE3 at 3 Gsps with 347-MHz Input Signal     |                 |

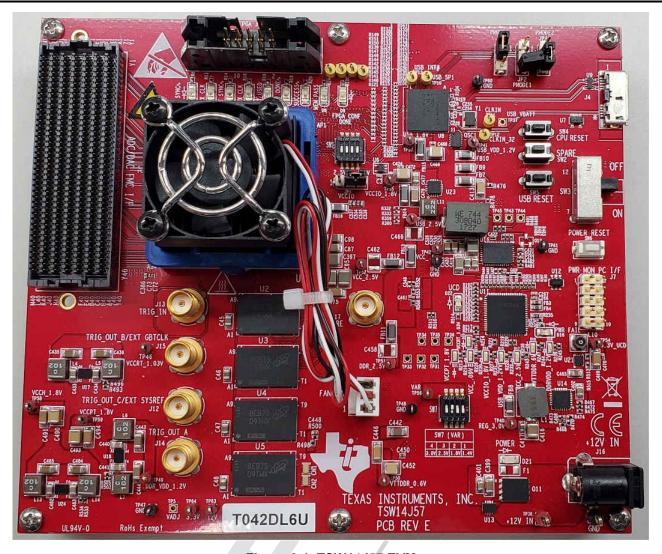

| Figure 9-1. TSW14J57 EVM                                                            |                 |

| Figure 9-2. TSW14J57 EVM connected to an ADC34J45 EVM                               | 65              |

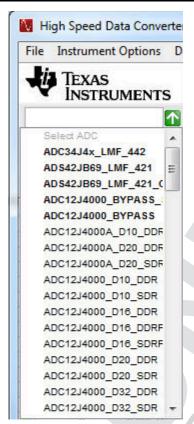

| Figure 9-3. Select ADC34Jxx in the HSDC Pro GUI Program                             |                 |

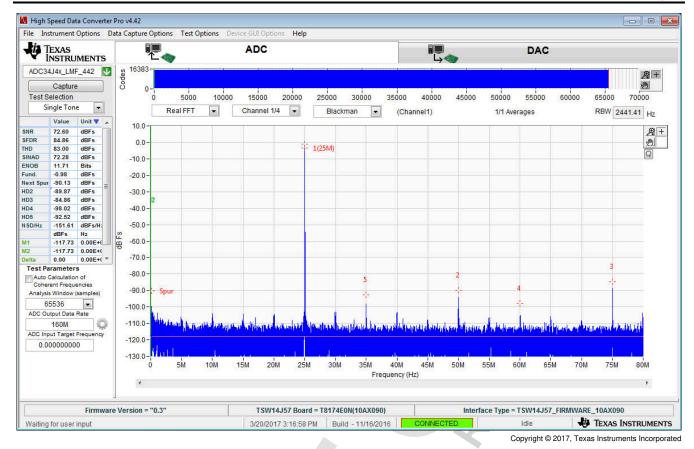

| Figure 9-4. ADC34J45 Operating in 14-Bit Mode at 160 Msps with 25-MHz Input Signal  | <u>67</u>       |

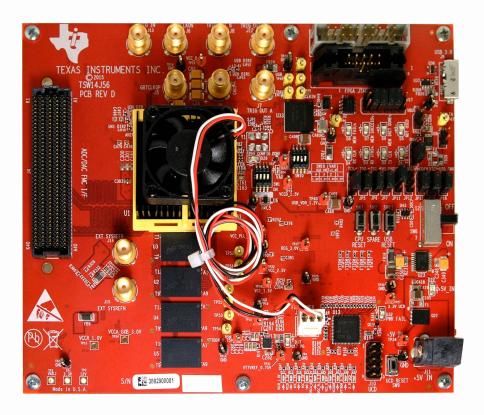

| Figure 10-1. TSW14J56 EVM                                                           |                 |

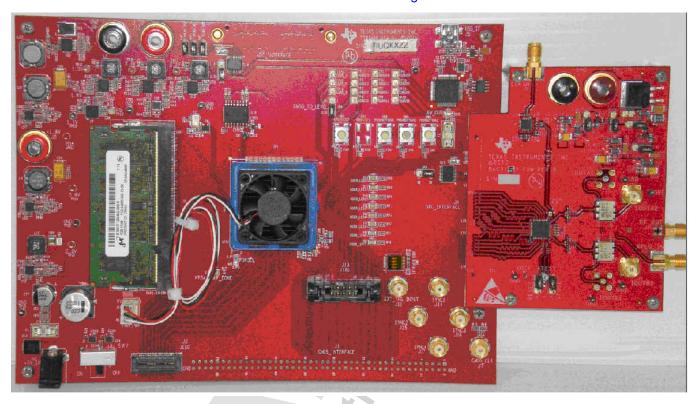

| Figure 10-2. TSW14J56 EVM connected to an ADC34J45 EVM                              | <mark>69</mark> |

| Figure 10-3. Select ADC34Jxx in the HSDC Pro GUI Program                            | 70              |

| Figure 10-4. ADC34J45 Operating in 14-Bit Mode at 160 Msps with 10-MHz Input Signal | 71              |

| Figure 11-1. TSW14J50 EVM Connected to an ADS42JB69 EVM                             |                 |

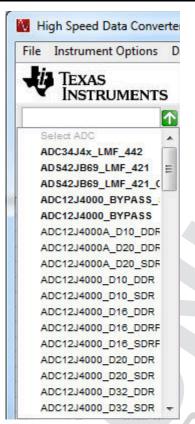

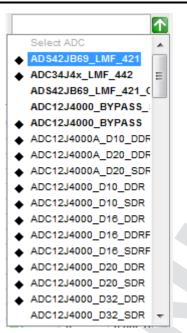

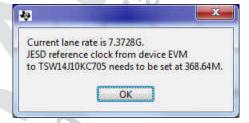

| Figure 11-2. ADS42JB69_LMF_421                                                      | 73              |

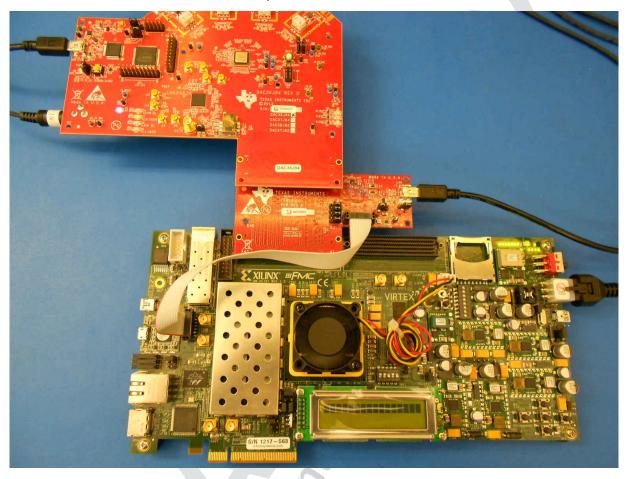

| Figure 12-1. TSW14J10EVM, DAC38J84EVM, and Virtex VC707 Development Card            | 74              |

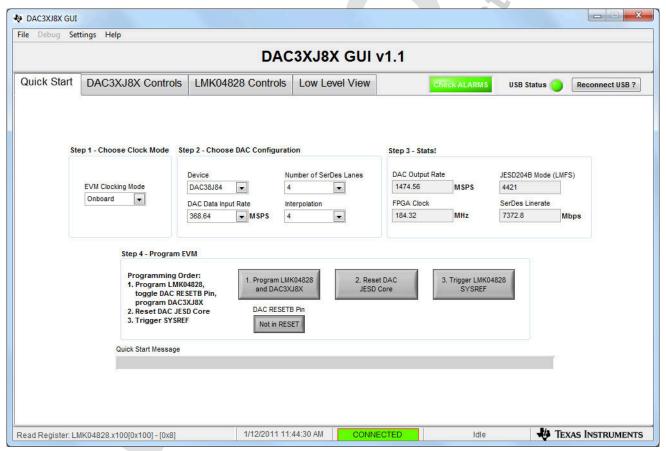

| Figure 12-2. Quick Start Menu                                                       | 75              |

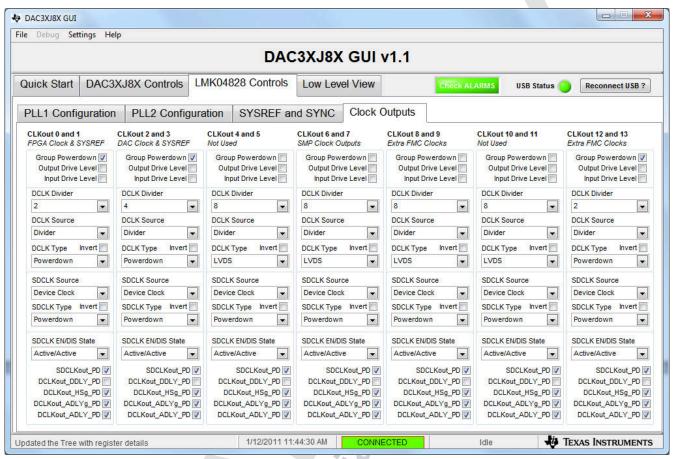

| Figure 12-3. LMK04828 Clock Outputs Menu                                            | <u>76</u>       |

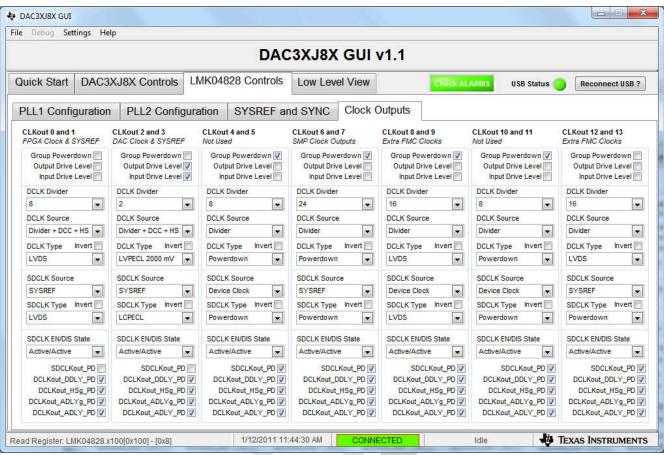

| Figure 12-4. LMK04828 Clock Outputs Menu                                            | 77              |

| Figure 12-5. HSDC Pro GUI                                                           | 78              |

| Figure 12-6. HSDC Pro GUI: Lane Rate and REFCLK Settings                            | 78              |

# **Trademarks**

Xilinx®, Kintex®, UltraScale®, Intel PSG®, Arria®, are registered trademarks of Altera Corporation. Virtex® are registered trademarks of Xilinx Corporation. Intel® is a registered trademark of Intel.

All trademarks are the property of their respective owners.

Introduction www.ti.com

# 1 Introduction

The HSDC Pro GUI supports testing of all TI high-speed data converter EVMs when used with a TSW14xxx EVM. When used with an ADC EVM, high-speed data (either CMOS, LVDS, JESD204B serial, or JESD204C serial) is captured and then stored into a memory bank or directly inside the FPGA, depending on which TSW14xxx platform is being used. To acquire data on a host PC, the FPGA reads the data from memory and transmits it on Serial Peripheral Interface (SPI). An onboard high-speed USB-to-SPI converter bridges the FPGA SPI interface to the host PC and GUI.

In Pattern Generator Mode, HSDC Pro can generate the desired test patterns or load existing patterns for DAC EVMs under test. These patterns are sent from the host PC over the USB interface to the TSW14xxx. The FPGA stores the data received internally or into board memory, depending on the platform used. The data is then read by the FPGA and transmitted to a DAC EVM across the mating connector.

HSDC Pro GUI utilizes a DLL and a set of API's to communicate from the GUI to the TSW14J5x via a Cypress FX3 USB 3.0 device. This next-generation USB 3.0 controller provides a programmable parallel interface which connects directly to the FPGA to provide high speed data transfers. The interface is compatible with both USB 2.0 and 3.0 systems. The theoretical limit for data transfer via USB 3.0 is 5Gbps and USB 2.0 is 480 Mbps. But with packet overhead and handshaking latency the effective throughput via the Cypress FX3 device is 2Gbps for USB 3.0 systems and 320Mbps for USB 2.0 systems. The samples that are transferred to PC will undergo post processing and will be stored as a binary file, due to which the effective data transfer rate is again reduced. With a 3.0 system, the user can capture 1GBytes ≈ 20 seconds (400Mbps). With a 2.0 system, around 45 seconds (177Mbps). This controller is also used to configure the onboard FPGA using parallel programming mode, which allows for configuration in less than three seconds.

For the TSW1400/05/06 EVMs, the GUI communicates via a FTDI FT4232H device. The FT4232H is a USB 2.0 Hi-Speed to UART IC. It has the capability of being configured in a variety of industry standards, such as serial or parallel interfaces. The FT4232H features 4 UARTs. Two of these have an option to independently configure an MPSSE engine, this allows the FT4232H to operate as two UART/Bit-Bang ports plus two MPSSE engines used to emulate JTAG, SPI, I2C, Bit-bang or other synchronous serial modes.

Key features of the HSDC Pro Software:

- Single- or multiple-tone frequency tests

- Continuous data captures

- · Channel power measurement

- External trigger capability

- · Master and slave operation

- · Pattern generator

- Load custom patterns

- · Save and export captured data

- Frequency and Time analysis

- One GUI supports all TSW14xxx platforms

The TSW14xxx family consists of the following EVM's:

- TSW1400 The TSW1400 EVM supports all high-speed ADC and DAC EVM's that use an LVDS or CMOS interface for the data path.

- TSW1405 Low cost, limited memory data capture card to be used with all high-speed ADC EVM's with LVDS interface.

- TSW1406 Low cost, limited memory pattern generator card to be used with all high-speed DAC EVM's with LVDS interface.

- TSW14J10 The TSW14J10 EVM allows users to evaluate TI JESD204B high-speed data converters using existing FPGA vendor development platforms.

- TSW14J50 The TSW14J50 EVM supports all high-speed ADC and DAC EVMs using a JESD204B interface for the data path.

- TSW14J56 The TSW14J56 EVM supports all high-speed ADC and DAC EVMs using a JESD204B interface for the data path.

www.ti.com Introduction

• TSW14J57 – The TSW14J57 EVM supports up to 16 lanes for all high-speed ADC and DAC EVMs using a JESD204B interface for the data path.

- TSW14J58 The TSW14J58 EVM supports up to 16 lanes for all high-speed ADC and DAC EVMs using a JESD204C interface for the data path.

- TSW14DL3200 The TSW14DL3200 EVM supports up to 48 pairs of high-speed LVDS signals or to provide up to 48 pairs of LVDS data.

Consult the TSW140x High Speed Data Capture/Pattern Generator Card User's Guide (SLWU079) for more information regarding the hardware aspect of the TSW1400, TSW1405 and TSW1406 EVMs.

Consult the TSW14J5x JESD204B/C High Speed Data Capture and Pattern Generator Card User's Guide for more information regarding the hardware aspect of these four EVMs.

Consult the TSW14DL3200EVM High Speed LVDS Data Capture/Pattern Generator Card User's Guide for more information regarding the hardware aspect of this EVM.

Additionally, the user has the option of using Xilinx FPGA development kits to interface with TI's JESD204B based high-speed data converter EVMs.

Software Start up www.ti.com

# 2 Software Start up

## 2.1 Installation Instructions

Download the latest version of the HSDC Pro GUI to a local location on a host PC. This can be found on the TI website by entering "HIGH SPEED DATA CONVERTER PRO GUI INSTALLER" or "TSW1400EVM" in the search parameter window at www.ti.com.

- Unzipping the software package will generate a folder called "High Speed Data Converter Pro Installer vx.xx.exe", where x.xx is the version number. Run this program to start the installation.

- Make sure to disconnect all USB cables from any TSW14xxx boards before installing the software.

- Follow the on-screen instructions during installation.

- Click on the "Install" button. A new window opens. Click the "Next" button.

- Accept the License Agreement. Click on the "Next" button to start the installation. After the installer has finished, click the "Next" button one last time.

- The installation is now complete. The GUI executable and associated files will reside in the following directory:

- C:\Program Files (x86)\Texas Instruments\High Speed Data Converter Pro.

- Power up the TSW14xxx under test.

- To start the GUI, click on the file called "High Speed Data Converter Pro.exe", located under C:\Program Files (x86)\Texas Instruments\High Speed Data Converter Pro.

#### Note

If an older version of the GUI has already been installed, make sure to uninstall it before loading a newer version. If the GUI detects that a newer version of the GUI is available online (http://www.ti.com/tool/tsw1400evm), it will assist the user with downloading the latest version from the TI website. The GUI automatically interrogates the product website for latest version every seven days but the latest version check can also be manually invoked through use of the pull-down menu Help->Check for updates.

#### Note

When new TI HSDC EVMs become available that are not supported with the current GUI software release, the HSDCProv\_xpxx\_Patch\_setup executable, available on the TI website (www.ti.com), will allow the user to add these EVMs to the GUI device list. Doing a search for TSW1400 will direct the user to this location. The user should download this patch. Start the application and follow the on screen instructions. The patch will display the files that will be either added or replaced and have tabs for viewing what files will be deleted and release notes. After running the patch, the user will then be able to start the High Speed Data Converter Pro GUI and notice new parts added to the ADC and DAC device drop down selection box. The patch is always specific to a core GUI version so the patch application would not work for any GUI version that the patch was not explicitly created for.

www.ti.com Software Start up

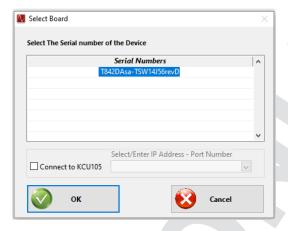

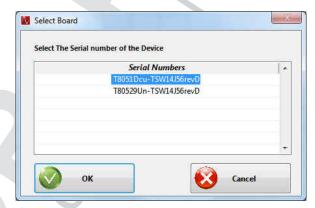

#### 2.2 USB Interface and Drivers

The HSDC Pro GUI will first attempt to connect to the EVM USB interface. If the GUI identifies a valid board serial number, a pop-up will open displaying this value, as shown in Figure 2-1. The serial number also has an EVM type number attached to it. This indicates to the GUI which TSW14xxx board is presently connected to the host PC. It is possible to connect several TSW14xxx EVM's to one host PC but the GUI can only connect to one at a time. If multiple boards are connected to the PC, the pop-up displays all of the serial numbers found. It is then up to the user to select which board the GUI will be associated with.

Figure 2-1. TSW14xxx EVM Serial Number

Click on "OK" to connect the GUI to the board. If the FPGA firmware version read by the GUI does not match the firmware to be used as determined by the device selected (see section 3.4 for more info on device selection), the following message appears as shown in Figure 2-2. This message also appears after power up as the FPGA is not programmed.

Figure 2-2. Firmware Does Not Match the Device Selected

Software Start up Vivil Com

Click on "OK". The Top level GUI now opens and appears as shown in Figure 2-3.

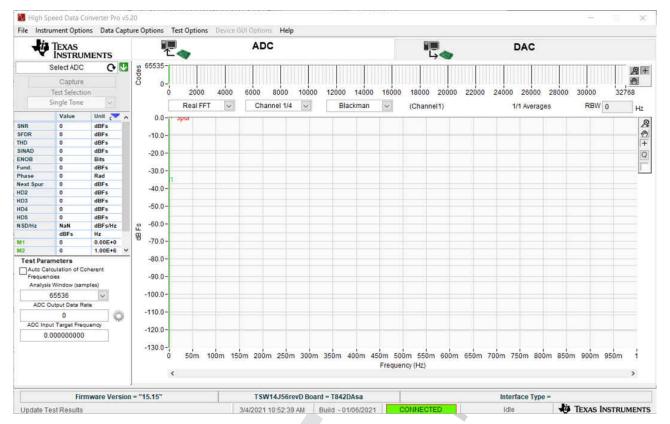

Figure 2-3. TSW14xxx EVM GUI Top Level

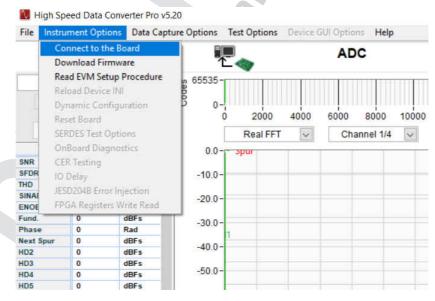

After the software has established a connection, if the message "No Board Connected" opens, double check the USB cable connections and that power is present. If the cable connections appear fine, try establishing a connection by clicking on the "Instrument Options" tab at the top left of the GUI and select "Connect to the Board" (see Figure 2-4). If this does not help, disconnect the USB cable from the board then reconnect it, click on the "Instrument Options" tab, then select "Connect to the Board". If this still does not correct the issue, check the status of the host USB port.

Figure 2-4. Connecting GUI to EVM

www.ti.com Software Start up

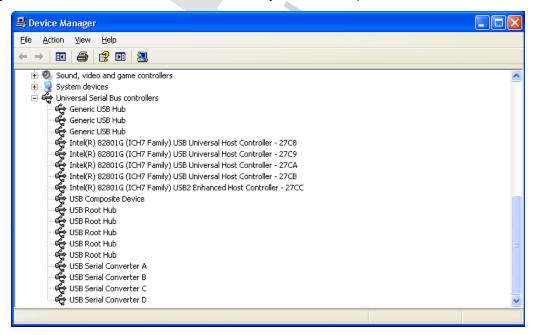

When the software has been installed and the USB cable has been connected to a TSW1400/05/06 EVM and the PC, the USB serial converter should be located in the Hardware Device Manager under the Universal Serial Bus controllers as shown in Figure 2-5. This is a quad device which is why there is an A, B, C, and D USB Serial Converter shown. When the USB cable is removed, these four will no longer be visible in the Device Manager. If the drivers are present in the Device Manager window and the software still does not connect, cycle power to the board and repeat the steps above.

If the GUI starts up but freezes before it brings up the "Connected to Board" dialog, or takes an unusually long time for other actions to occur, it is possible the USB being used from the host PC is operating at USB 1.0 speeds. A common indication of this is when the status bar on the bottom left of the screen keeps reading "Disable all Controls" upon loading the software without ever going to the "Connect Board Dialog". The GUI is designed to run at USB 3.0 speeds and some computers have USB 1.0 ports on the front panel and 2.0 or 3.0 on the back panel. Using the 3.0 ports on the back of the PC if at all possible is recommended.

The .exe file installs the FTDI drivers during software installation. If after connecting the USB cable and Windows lists the board as an "unknown device", this could be caused by corrupted FTDI drivers being installed on the computer. This happens in cases where the same computer has been used to interface with previous products that used FTDI drivers. In this case, users are advised to download and install a utility from FTDI at <a href="http://www.ftdichip.com/Support/Utilities/CDMUninstaller\_v1.4.zip">http://www.ftdichip.com/Support/Utilities/CDMUninstaller\_v1.4.zip</a>.

The help file for using this utility can be found at: http://www.ftdichip.com/Support/Utilities/CDM\_Uninst\_GUI\_Readme.html

Users will need to use the following hex values to uninstall previous versions of the ftdi drivers:

Vendor ID (VID): 0403 Product ID (PID): 6010

After removing the drivers for this PID and VID, users are advised to re-connect the TSW14xxx USB cable and check if the TSW14xxx ports get listed properly in Device Manager.

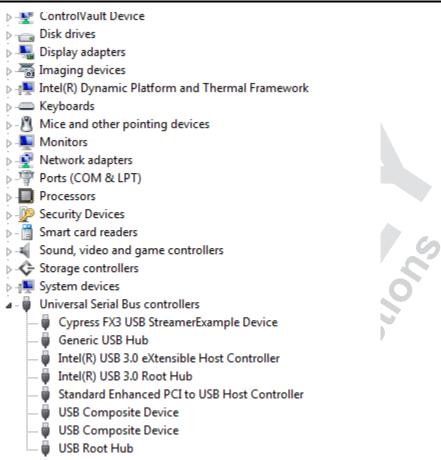

For the TSW14J5x, the .exe file installs the Cypress USB 3.0 drivers during software installation. The USB 3.0 driver, called "Cypress FX3 USB StreamerExample Device", should be located in the Hardware Device Manager under the Universal Serial Bus controllers as shown in Figure 2-6.

If after connecting the USB cable and Windows lists the board as an "unknown device", this could be caused by the Cypress USB 3.0 not booting properly from the flash device. Press the USB reset switch SW11 (SW5 on J57) and try to reconnect the GUI. If this does not work cycle the board power.

Figure 2-5. Hardware Device Manager

Software Start up www.ti.com

Figure 2-6. Cypress FX3 USB Streamer Example Device in USB Controllers

#### 2.3 Device ini Files

Included in the installation for the HSDC Pro GUI software is a subdirectory of ini files for each category of ADC and DAC that is supported by the TSW14xxx EVMs. TI strongly recommends that these files are not edited except at the factory. These files contain necessary information for the GUI software to properly configure the TSW14xxx EVM FPGA registers for proper operation with the desired ADC or DAC EVM. Some of the entries within the ini file are obvious, such as defining the bit resolution for a device as 11, 12, 14, or 16 bits. Other entries in the ini file define for the FPGA which LVDS pairs within the Samtec connector comprise the data bus, and correct operation may not be possible if these entries are edited. The use of ini files allows for new device types to be supported by the TSW14xxx EVM as they become available without having to modify, re-release, or re-install the HSDC Pro GUI software. New device types may be supported at a later date simply by adding a new ini file to the proper subdirectory.

#### 3 User Interface

When the HSDC Pro GUI software is started, the initial setup screen of Figure 2-3 appears. The TSW14xxx EVM serial number is reported in the lower center of the GUI. After the FPGA is loaded with the selected firmware, the GUI will report the firmware version in the lower left and the interface type will be reported in the lower right. The connection status should read "Connected" and be highlighted in green (lower center of the GUI). The status panel, located in the lower right, will report "IDLE". Many of the TSW14xxx software controls are available from the main screen, such as "ADC or DAC" mode, "Select device", "Capture and Test Selection" (ADC mode only), and "Load External Pattern File" (DAC mode only).

#### 3.1 Toolbar

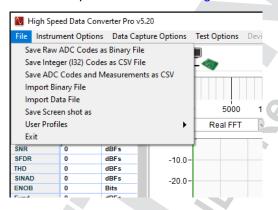

The toolbar contains options and settings that are independent of the device selected for test or the test to be performed, such as configuration options and save/recall operations. The operations available under the toolbar are grouped in categories as follows: File, Instrument Options, Data Capture Options, Test Options and Help.

## 3.1.1 File Options

The file tab contains all of the options for saving or importing test results. Placing the mouse indicator over the File tab will open a window with the available options as shown in Figure 3-1.

Figure 3-1. File Tab Options

There are options for saving the ADC captured data as 32 bit singed integer (I32) CSV or Binary format in a directory specified by the user for export or archival purposes. The "Save I32 Codes as CSV File" options will save the captured ADC data as 32 bit singed integers with each channel's data across columns in a CSV file. The CSV data can range from  $-2^{\circ}$  (Number of Bits -1) to  $2^{\circ}$  (Number of Bits -1) -1. The "Save ADC Codes and Measurements as CSV" option will save the captured ADC data as 32 bit singed integers along with the measurements data as CSV file. The "Save Raw ADC Codes as Binary File" option will save the raw data captured from the ADC as a binary file. The "Save Screen shot as" option, when selected, will open a window that will allow the user to save the current GUI screen shot as either a bmp, jpeg, or png file in the directory specified by the user.

Note: Number of Bits = Sample resolution.

The GUI provides an option to allow the user to replay files captured from an ADC by the GUI itself. To use this feature, import a test file by either selecting "Import Binary File" or "Import Data File" in the drop down. A new navigator window will open. Select the desired file to be loaded. If a binary file is to be used select "Import Binary File" menu option, after the file is selected (.bin file), a new window will open asking for number of channels and number of bits. Provide this information then click "OK". The format of the binary sample is big-endian and the size of the samples should be either 2 Bytes (for sample resolutions less than or equal to 16) or 4 Bytes (for sample resolutions greater than 16 and less than or equal to 32). For multiple channel test cases, the test file must have channel data interleaved. For example, if there are 4 channels, the samples should be arranged as Channel1Sample1, Channel2Sample1, Channel3Sample1, Channel4Sample1, Channel4Sample2, Channel3Sample2, Channel4Sample2, Channel3SampleN, Channel4SampleN, Channel4SampleN,

For the "Import Data File" option, the user can use several different types of files. After the file is selected, the GUI will ask for number of channels and number of bits. The user must know this information for proper data to be displayed. The data test file must be in text format having integer values from  $-2^{\circ}$  (Number of Bits -1) to  $2^{\circ}$  (Number of Bits -1) -1. For two channel test cases, channel 1 is the data in the first column and channel 2 is the data in the second column. The different file types that can be used include .gcin (space), .ssv (space), .csv (comma), .txt (tab), and .tsw. The GUI expects such files to be delimited by the delimiters shown in the parentheses. Adjacent columns are separated by the delimiter. The .tsw files are proprietary encoded files created by Texas Instruments.

# 3.1.1.1 User Profiles

This option can be used to save the user interface settings to a file and load it while launching the GUI (by default) or whenever needed. The list of UI settings that are being saved are *Test Selection*, *Graph Type*, *FFT Window*, and *Filter Parameters* available in *Notch Frequency* bins of the GUI. Clicking on 'User Profiles' under 'File' menu will list down the submenu as shown in Figure 3-2.

Figure 3-2. User Profiles

Load User Profile – Clicking on this option opens the 'Open' dialog box where user-saved file, default file, or factory settings file can be loaded.

Save User Profile – This option saves the current UI settings to a file and prompts the user to specify the name of the file in the 'Save As' dialog box.

Save as Default Profile - This option will replace the default profile file with the current settings in the GUI. Whenever the GUI is launched, the default profile will be loaded.

Restore Factory Defaults – This option will restore the default settings that came along with the installer and also replace the default profile file with these values.

## 3.1.2 Instrument Options

The Instrument Options menu tab contains 4 generic options: Connect or Disconnect from the board, Download Firmware, Read EVM Setup Procedure, and Reload INI. The Dynamic Configuration, Reset Board and SERDES Test Options, Onboard Diagnostics, CER Testing, IO Delay, JESD204B Error Injection and FPGA Registers Write Read options are specific to some TSW14xxx boards and selected device INIs. These options are listed when selecting the Instrument Options menu as shown in Figure 3-3.

Figure 3-3. Instrument Options

The Connect to the Board command will cause the GUI to read the serial number inside the USB controller on the TSW14xxx and display the value found or report that no board is connected. This can be used when a user removes power from the TSW14xxx board, then re-applies power while leaving the GUI active. Disconnect from the Board will release the GUI from the USB interface and allow the GUI to now be connected to another board. This is useful when operating multiple TSW14xxx EVMs with one computer.

The Download Firmware command allows the user to select a file that will be used to program the FPGA. These files need to be .rbf or .bin files for this to work. The files used by the GUI currently reside in the directory called "Firmware", under the TSW14xxx directory. This option would be used if the GUI cannot identify the firmware file called out in the ini file, or if an advanced user has a new file they would like to try.

The Read EVM Setup Procedure command causes the HSDC Pro software to read a comment string from the ini file for the device that is currently selected and then display that comment string in the status pane. This comment string generally contains necessary setup information pertaining to the EVM under test, such as possibly requiring a non-default data format or required jumper setting for the EVM to communicate properly with the TSW14xxx. Some ini files may not support this feature though.

Reload Device INI causes HSDC Pro software to reload INI files for the selected ADC or DAC device. For more information on INI files, refer to Section 2.3.

The Dynamic Configuration command is used by the TSW14J5x JESD204B serial interface EVMs only. This command allows the user to change certain JESD204B parameters such as number of lanes, number of converters, number of octets per frame, and so forth. See Section 10 for more information regarding this command.

The Reset Board command is currently only used with the TSW14J5x EVMs. The firmware for this EVM has a reset register that will initialize the firmware without reloading the firmware.

The SERDES Test Options tab provides the ability to analyze the device by measuring the eye opening. The EyeQ Scan feature is discussed in further detail in the section below.

IO Delay, JESD204B Error Injection, and FPGA Registers Write Read is discussed in the sections below.

## 3.1.2.1 TSW14J56 and High Speed Data Converter (HSDC) Pro Eye Quality Analysis

The TSW14J56EVM utilizes an Intel PSG® Arria® V GZ FPGA device for the receive and transmit functions for the JESD204B link. One of the features of the Arria® V GZ device is the On-Chip Signal Quality Monitoring Circuitry (EyeQ). The EyeQ feature is a debug and diagnosis tool that analyzes the received data by measuring the horizontal and vertical eye opening.

The following section provides a quick start-up example that highlights the software features of the EyeQ Scan analysis.

- 1. Verify that the ADC EVM provides an FFT capture on HSDC Pro.

- Under the "Instrument Options" tab, click on "SERDES Test Options".

- 3. A new window should appear with the following features:

- Lane Selects one of the available lanes for the selected interface mode

- Time per iteration Selects how long data is accumulated before generation of the Eye diagram. Increasing this value also increases the Test Time proportionally

- EQ DC Gain Adjusts DC gain of FPGA receive hardware block

- EQ AC Gain Adjusts AC gain of FPGA receive hardware block

- Display Standard Eye Overlays one of the JESD204B receive eye-mask templates onto the Eye diagram

- 4. After configuring the parameters, click on "START". The scan may take a few seconds to a few minutes depending on the parameters chosen.

Figure 3-4 shows an eye diagram of the ADC34J45EVM in 442 mode, sampling at 140 MHz and a lane rate of 2.8 GHz.

Figure 3-4. Example Eye Diagram Plot

## 3.1.2.2 IO Delay

The "IO Delay" Calibration process will sweep the IO Delay tap values across a lane and get the tap values where there are no bit errors. Selecting the IO Delay opens the window shown in Figure 3-5 below, using this one can calibrate the lane wise delay adjustments.

Figure 3-5. IO Delay Calibration

Calibration is done sequentially for the selected lanes, one after the other. The "Tap Resolution" denotes the minimum step size with which the tap values should be swept across IO Delay tap values. "Bit Error Validation time (ms)" specifies the time delay to wait before checking if the Error Bit is true/false while sweeping across the IO Delay tap vales. "Check all Lanes?" can be used to check/uncheck all the lanes. After selecting the required lanes to calibrate, click on the "Start Calibration Data" button, this will run the calibration on the selected lanes one after the other. Once calibration has been started ("Start Calibration" will then turn into "Stop Calibration"), it can be stopped anytime using "Stop Calibration" button. After the calibration completes, the calibrated data can be saved by clicking on "Save Calibration Data" and entering the target file location. Click on "Load Calculated Delay" and load the previously saved file with Calibration data, this action will derive the "Calculated Delay" for all the selected/calibrated lanes and the same calculated delay gets loaded to the FW. This completes the IO Delay Calibration. After the IO Delay Calibration steps are done, data capture can be done from HSDC Pro as usual.

**Note:** Currently the IO Delay option is supported only in the TSW14DL3200 EVM board. Do not close the IO Delay window when the calibration is running. If closed when the calibration is running, restart HSDC Pro. Before doing the calibration, ensure that the FW has been downloaded and no capture/calibration has been done after the FW download.

## 3.1.2.3 JESD204B Error Injection

The JESD204B Error Injection option (shown in Figure 3-6) is a debug feature that enables the user to inject errors like LOS events, disparity error and Not In Table error in the TX SERDES Lanes of the FPGA and verifying the same at the DAC devices.

User can turn off/on the TX SERDES Lanes Individually by unchecking/checking the "FPGA STX Lane # to (Device SRX Lane #)" check boxes. Whenever a TX lane powers down, a pulse (rising edge) of configurable width will be sent out of FPGA on SMA pin (TRIG OUTA). The width of the pulse can be configured with the "Trigger Pulse Width (ns)" input control.

**Note:** When a specific TX lane is powered down, in addition to LOS Event, the disparity error and Not In Table Error are set in that particular lane and the same can be observed in the DAC devices. This feature is currently available only in the DAC Mode of TSW14J57revE board.

Figure 3-6. JESD204B Error Injection Window

## 3.1.2.4 FPGA Registers Write Read

The FPGA Registers Write Read menu option (shown in Figure 3-7) allows the user to write/read the registers of the FPGA Firmware. The firmware register map of the TSW14xxx board will be loaded and the Register Name, Register Address, R/W Mode, Register Values and Register Description will be shown. The register write operation can be done by selecting the required register element from the tree or by specifying the required register address in the "Address" input control and providing a value to be written at "Write Data" input control and then clicking on the "Write Register" button. Similarly, the register read operation can be done by clicking on the "Read Register" button after specifying the required register address and the read register value will be updated both in the register tree and "Read Data" output indicator. The current register configuration listed in the register map can be exported as ".cfg" file by using the "Save Config" button and the same can be loaded by using the "Load Config" button. The "Load Config" operation will overwrite the existing data in registers with the value specified in the loaded configuration file.

Figure 3-7. FPGA Registers Write Read Window

Note: This feature is currently implemented only for the TSW14J58EVM.

## 3.1.3 Data Capture Option

The Data Capture Options drop-down menu (ADC mode only) has three choices: (1) Capture Option (2) Number of Channels and (3) Trigger Option.

## 3.1.3.1 Capture Option

Selecting the *Capture Option* opens the window shown in Figure 3-8. From this menu, one can capture continuously by checking the appropriate box – allowing the monitoring of continuous captures over time.

Figure 3-8. Capture Option

The Capture Option allows the flexibility to set the # samples (per channel) to be captured. This value is limited by the memory available on the TSW EVM. For example, if using the TSW1400, which has 1GB of RAM, with a 4-channel ADC, the value that would utilize all memory, and, therefore, the maximum value, would be:

(1048576 Mbytes) × (1 sample / 2 bytes) × (1/4 ADC channels) = 131072 Msamples / channel

The TSW14J56 has 1GB (8Gb) of RAM which allows up to 536,870,912 16-bit samples divided by the number of channels. Similarly, the TSW14J57 has 2GB (16Gb) of RAM which allows up to 1,073,741,824 16-bit samples divided by the number of channels. The sample amounts for the TSW14J56 and TSW14J57 are calculated under the assumption that no tail bits are present in the data frames.

The GUI default value for both boards is 65,536.

The GUI automatically rounds down to the nearest multiple of the displayed value on the right of the "# samples (per channel)" control field and updates the entered value. This value determines the number of samples that will be captured and saved to binary or CSV file. This value does not affect the record length used to generate the FFT plot. The record length used by the FFT plot is determined by the value of *Analysis Window (samples)* in the fixed left front panel of HSDCpro and can be set from 4096 to 524,288 samples when using the TSW14xxx.

The processed FFT data can be averaged over N captures by checking the box *Average FFT*? and setting the value N into the *Number of Captures* box. The average FFT uses the root mean square method so as to minimize PC memory usage. This value is limited to 1024 averages. If *Average FFT*? is enabled at the same time that *Continuous Capture*? is enabled, then the displayed FFT is a rolling average of the last N captures.

When the "Write captured data to a file" option is checked:

- For TSW14J5x data capture boards, data for each channel is stored in a separate file at the location:

C:\Users\Public\Documents\Texas Instruments\High Speed Data Converter Pro\HSDCPro Data

- For TSW14xx data capture boards, all of the channel data is stored in a single file using an interleaved format at the location: C:\Users\Public\Documents\Texas Instruments\High Speed Data Converter Pro\ADC Temp.bin

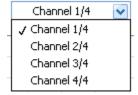

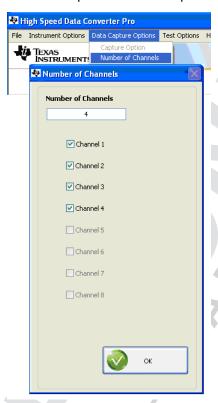

#### 3.1.3.2 Number of Channels

The *Number of Channels* option allows the user to specify the number of channels to be captured regardless of the number of channels the DUT has. This allows user to utilize the full memory capacity for a single channel if desired. This feature is presently only supported on the TSW1405 capture card where memory is 128KB (KBytes).

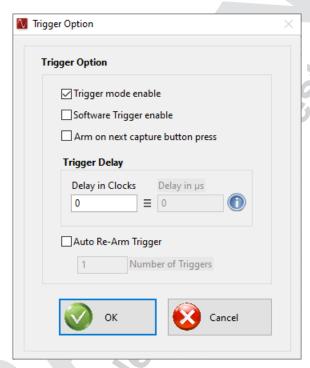

## 3.1.3.3 Trigger Option

Clicking on the Trigger Option will open a new panel as shown in Figure 3-9. This option is not available for the TSW1405/06. The GUI provides four options of capturing data using a trigger function. Selecting *Trigger mode enable* will arm the TSW14xxx to accept an external trigger.

Figure 3-9. Trigger Option

With both enables selected, the capture button on the main panel of the GUI will now change from "Capture" to "Generate Trigger". When the user clicks on this button, the GUI will send a CMOS logic level (1.8 VDC) active high pulse to the four SMA connectors labeled SYNC1, SYNC2, SYNC3, and SYNC4 on the TSW1400. On the TSW14J5x, these are labeled as TRIG\_OUT\_A, TRIG\_OUT\_B, and TRIG\_OUT\_C. This signal can be used to trigger other TSW14xxx EVMs or the same TSW14xxx. To use this rising edge to trigger the same TSW14xxx, the user must connect a cable from the SMA labeled as "EXT\_TRG\_INPUT" SMA (J11) on the TSW1400 ("TRIG\_IN", SMA J13 on the TSW14J5x) to one of the SYNC (TRG\_OUT) SMA's. Without this connection, the GUI will never detect a trigger and will report "No trigger occurred" a short time after the user has clicked on the "Generate Trigger" button. Once a trigger is detected, the GUI will do a capture.

Another trigger option is to use an external trigger source. To use this mode, only select "Trigger mode enable". When this mode is selected, the status button located at the bottom of the main GUI screen will display "TRIGGER ARMED" in yellow and the capture button will display "Read DDR Memory". The software is now waiting for a CMOS logic low to high transition to occur on the "EXT\_TRG\_INPUT" (TRG\_IN) input SMA. Once this occurs, a data capture will occur. The user will now click on the "Read DDR Memory" button to display the captured data. If the user clicks on this button before a trigger occurred, a short time later a "No trigger occurred" message appears. If the external trigger is a continuous event, the GUI will not do a new capture until the user clicks on "Read DDR Memory". This causes the software to display the results from the first trigger event and reload the memory with new data on the next rising edge of the external trigger input.

Another trigger option invloves selecting both "Trigger mode enable" and "Arm on next capture button press". With these two selected, the software will do a capture on the next rising edge detected on EXT\_TRG\_INPUT/

TRIG\_IN connectors only after the user clicks on the "capture" button. This mode comes in handy if there are multiple trigger pulses arriving but the user does not want to trigger until a certain time later. If a trigger is not detected within about 12 seconds after clicking on capture, the software will time out and report no trigger detected.

When using the trigger capture mode, the user has an option to capture data a fixed amount of samples after the capture has actually started. This is useful for devices that have a "High Resolution Burst mode", where it takes several clock cycles to occur before valid samples are available. This delay is determined by the value entered in the "Trigger CLK Delays" box. The default value is "0". The user can enter a value from 0–7 with the corresponding sample delay shown in Table 3-1. Note that the delay is also based on the number of channels captured. For example, if a user selects a Trigger Delay of "2" and is capturing data from 2 Channels, after a trigger is detected by the GUI, the data capture starts. With this delay setting though, the first data sample used by the GUI will be the 81<sup>th</sup> sample from the ADC after the trigger occurred.

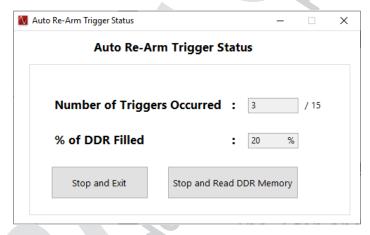

Another trigger option involves selecting both "Trigger mode enable" and "Auto Re-Arm Trigger". With these two selected the TSW14xxx EVM will capture the configured amount of samples ("# of samples per channel", from the Capture Option) for every trigger pulse (CMOS logic low to high transition that occurs on the "EXT\_TRG\_INPUT" (TRIG\_IN, TSW14J5x) SMA.) and accumulate the captured samples in the DDR memory until the defined numbers of "Number of Triggers" gets completed.

When using this capture mode, the status button located at the bottom of the main GUI screen will display "TRIGGER ARMED" in yellow and the capture button will display "Show Trigger Status". Clicking on the "Show Trigger Status" button will open up a popup window displaying the status of the trigger operations with "Number of Triggers Occurred" and "% of DDR Filled". Clicking on the "Stop and Exit" button will stop the current capture operations without reading the captured sample. Clicking on the "Stop and Read the DDR Memory" button will stop the current capture operations and read the captured samples from the DDR. After the configured Number of Triggers occurs and required amount of DDR gets filled, the "Stop and Read the DDR Memory" button will display "Read DDR Memory" and clicking on the same will read the captured samples from the DDR.

Figure 3-10. Auto Re-Arm Trigger Status Window

For DAC mode, with both enables selected, the send button on the main panel of the GUI now changes from "Send" to "Generate Trigger". When this button is clicked, the GUI sends a CMOS logic high level (3 VDC) to the four SYNC SMA's on the TSW1400 and the three TRIG\_OUT SMA's on the TSW14J5x. This signal can trigger other TSW14xxx EVMs or the same TSW14xxx. A cable must be connected from the "EXT\_TRG\_INPUT" (TRIG\_IN, TSW14J5x) SMA to one of the SYNC (TRIG\_OUT, TSW14J5x) SMA's to use this rising edge to trigger the same TSW14xxx. Without this connection, the GUI will never send the data from the memory.

| Trigger Delay | Number of Samples Skipped Per Channel |           |           |           |

|---------------|---------------------------------------|-----------|-----------|-----------|

| Trigger Delay | 1 Channel                             | 2 Channel | 4 Channel | 8 Channel |

| 1             | 80                                    | 40        | 20        | 10        |

| 2             | 160                                   | 80        | 40        | 20        |

| 3             | 240                                   | 120       | 60        | 30        |

**Table 3-1. Trigger Delay Options**

**Table 3-1. Trigger Delay Options (continued)**

| Trigger Deley | Number of Samples Skipped Per Channel |           |           |           |

|---------------|---------------------------------------|-----------|-----------|-----------|

| Trigger Delay | 1 Channel                             | 2 Channel | 4 Channel | 8 Channel |

| 4             | 320                                   | 160       | 80        | 40        |

| 5             | 400                                   | 200       | 100       | 50        |

| 6             | 480                                   | 240       | 120       | 60        |

| 7             | 560                                   | 280       | 140       | 70        |

Another trigger option involves selecting both "Trigger mode enable" and "Auto Re-Arm Trigger". With these two selected the TSW14xxx EVM will capture the configured amount of samples ("# of samples per channel", from the Capture Option) for every trigger pulse (CMOS logic low to high transition that occurs on the "EXT\_TRG\_INPUT" (TRIG\_IN, TSW14J5x) SMA.) and accumulate the captured samples in the DDR memory until the defined numbers of "Number of Triggers" gets completed.

When using this capture mode, the status button located at the bottom of the main GUI screen will display "TRIGGER ARMED" in yellow and the capture button will display "Show Trigger Status". Clicking on the "Show Trigger Status" button will open up a popup window displaying the status of the trigger operations with "Number of Triggers Occurred" and "% of DDR Filled". Clicking on the "Stop and Exit" button will stop the current capture operations without reading the captured sample. Clicking on the "Stop and Read the DDR Memory" button will stop the current capture operations and read the captured samples from the DDR. After the configured Number of Triggers occurs and required amount of DDR gets filled, the "Stop and Read the DDR Memory" button will display "Read DDR Memory" and clicking on the same will read the captured samples from the DDR.

For DAC Auto Re-Arm Trigger mode, whenever the board receives a trigger signal at "EXT\_TRG\_INPUT" (TRIG\_IN, TSW14J5x) SMA, the samples from the start index will be sent out to the DAC from the FPGA.

## 3.1.3.4 Using Multiple TSW14xxx and ADC EVM's for Simultaneous Capture using Trigger Option

Multiple TSW14xxx EVMs can connect to a single PC. To access up to four individual TSW14xxx EVMs with the HSDC Pro software, use the disconnect and connect function of the HSDC Pro GUI.

- To disconnect: go to "Instrument Options > Disconnect from the Board"

- To connect: go to "Instrument Options > connect to the Board"

Before setting the trigger option, determine which EVM is the master and which is the slave. In the example shown in Figure 3-11, one board has serial number "T8051Dcu and the other is T80529Un. Use this info and the cabling setup for selecting which be is the slave board and which is the master board.

Figure 3-11. Two TSW14J56 EVM's Connected to one PC

#### 3.1.3.4.1 Hardware Setup

Connect a cable from the Master TSW14xxx SYNC/TRIG\_OUT SMA to the Master TSW14xxx EXT\_TRIG\_INPUT/TRIG\_IN SMA. This allows the Master TSW14xxx to register its own trigger output.

Connect another cable from an unused SYNC/TRIG\_OUT SMA on the Master to the SLAVE EXT\_TRIG\_INPUT SMA. This allows the slave TSW14xxx to receive the trigger signal from the Master.

#### **Note**

All SYNC/TRIG\_OUT SMA's contain the same signal. The order does not matter. The cables of each trigger signal should have equal length to ensure the trigger signal arrives at the same time for all boards.

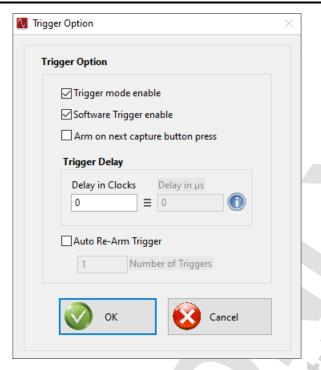

## 3.1.3.4.2 Setting up the Slave Board

With the HSDCPro GUI, establish connection to the slave TSW14xxx. Select the device, sample rate, and set up the slave TSW14xxx to accept a trigger signal, go to "Data Capture Options > Trigger Option".

Setup the trigger option as shown in Figure 3-12. This step arms the TSW14xxx slave board to detect trigger signal.

Figure 3-12. Slave Trigger Setup

The capture button will now change to "Read DDR Memory" and the message "Trigger Armed" will appear in the bottom of the GUI display. Disconnect the TSW14xxx slave board from the HSDC Pro GUI. To disconnect, go to "Instrument Options > Disconnect from the Board".

## 3.1.3.4.3 Setting up the Master Board

Connect the GUI to the master TSW14xxx board. Select the device, set the sample rate, then go to "data capture options > trigger option".

Set up the trigger option as shown in Figure 3-13. The software trigger sends out a trigger signal upon a software GUI button press. This also arms the TSW14xxx master board to register its own trigger signal. To capture data using the "Software Trigger enable" option, click on the "Generate Trigger" button on the main panel of the GUI. This will send out a pulse on the SYNC/TRIG\_OUT outputs. This signal, which is now connected to the EXT\_TRG\_INPUT/TRIG\_IN of both boards, starts a capture once detected by the FPGA of each board.

Figure 3-13. Master Trigger Setup

## 3.1.3.4.4 Read Captured Memory from the Slave Board

Disconnect the HSDC Pro from master board, and connect the software to slave. The user must select the device under test on the slave board again as the GUI does not keep track when using multiple boards.

Once the device is selected from the drag down menu, the message in Figure 3-14 will occur. Click OK to continue.

Figure 3-14. Trigger Confirmation Window

In the GUI main panel, enter the sampling rate to ensure correct FFT processing. Once this value is entered, the captured data from the trigger event is displayed.

For the TSW14J5x, there is an advanced option available for Master/Slave triggering that is synchronized with the SYSREF signal used by the JESD204B interface. This mode enables a Master/Slave triggering synchronized with SYSREF rising edges. In master mode, a hardware output trigger is generated on the TRIG\_OUT\_A/B/C SMA's at the first rising edge of SYSREF that occurs after the user presses the 'Capture' button. The data will then be captured at the next rising edge of SYSREF.

In the case of slave triggering mode, the capture occurs at the first SYSREF rising edge following the trigger input rising edge on the TRIG\_IN SMA input. This way both Master and Slave will start capturing data at the same SYSREF edge in a Synchronized manner.

# Software Changes Required: (The following steps are applicable for both ADC and DAC)

To put the TSW14J5x boards in Sysref-Based Master Slave Triggering mode, add the following INI parameter just below the [Version 1.0] entry in the corresponding master and slave device INI files, as shown in Figure 3-15.

· Sysref Based Master Slave Trigger = 1

```

DLL Version=1.0

Read EVM Setup Procedure="EVM Setup Procedure not available"

[version 1.0]

Sysref Based Master Slave Trigger = 1

JESD IP Core_CS=0

JESD IP Core_F=2

JESD IP Core_HD=0

JESD IP Core_K=16

JESD IP Core_L=8

JESD IP Core_M=2

JESD IP Core_N=16

JESD IP Core_NTotal=16

JESD IP Core_S=4

JESD IP Core_SCR=0

JESD IP Core_Tailbits=2

JESD IP Core_LaneSync=1

JESD IP Core_Subclass=1

```

Figure 3-15. Sysref-Based Master Slave Triggering INI Setting

In the HSDC Pro GUI, select the Trigger Option menu under Data Capture Options.

For the master board, select Trigger mode enable and Arm on next capture button press.

For the slave board, select **Trigger mode enable** in the Trigger Option window.

HSDC Pro GUI is now configured for SYSREF-Based Master Slave Triggering. Go back to the master board and the software will do a capture on the next rising edge detected on EXT\_TRG\_INPUT/TRIG\_IN connectors after the user clicks on the "capture" button.

#### 3.1.4 Test Options

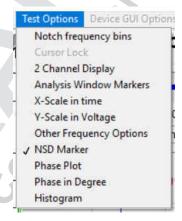

The Test Options menu tab allows for setting the parameter options for the different frequency and time domain tests. These options include Notch frequency bins, Cursor Lock, 2 channel display, Analysis Window Markers, X-Scale in time, Y-Scale in Voltage, Other Frequency Options, NSD Marker, Phase Plot, Phase in Degree, and Histogram as shown in Figure 3-16.

Figure 3-16. Test Options

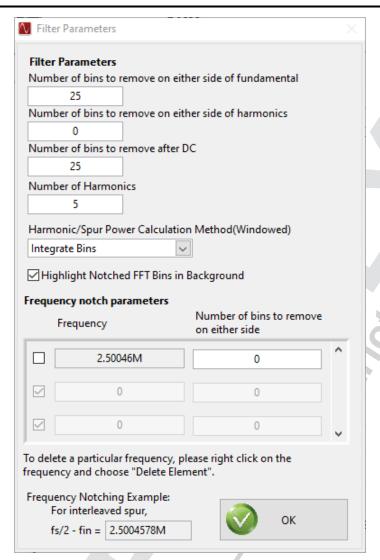

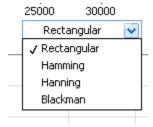

## 3.1.4.1 Notch Frequency Bins

The Notch Frequency Bins option allows the user to remove a number of bins from the SNR calculation of the input frequency around the fundamental, DC and a predetermined number of harmonics. The default values for these settings when capturing data using Blackman window mode is 25, 0, 25, and 5, as shown in Figure 3-17. When the capture mode is set to Rectangular mode, the default values are 0, 0, 1, 5.

User Interface

Figure 3-17. Notch Frequency Bin Removal

By default, the noise calculations for SNR and SINAD are based on the FFT of the captured data with the Notch Filter parameters applied. The first FFT bin at DC is not used because the first bin contains DC offset and thus does not effect AC parameters or AC performance. The rest of the FFT bins out to the Nyquist frequency are included in the calculation of the total noise.

The Harmonic/Spur Power Calculation Method(Windowed) button allows the user to either Integrate the Bins or Don't Integrate the bins. When "Integrate Bins" is selected, the neighboring bins are also included in the harmonic and spur calculations. Apart from the harmonic frequency bin, its neighboring bins will also be used for harmonic power calculation.

When "Don't Integrate" is selected, the neighboring bins are not included in the harmonic and spur calculations. Only the single harmonic frequency bin will be used for the harmonic power calculation.

This option will also affect the FFT filtering. In "Integrate" mode, neighboring bins of the harmonics will not be notched.

There is also an option to notch out bins around a user defined frequency. The default sets the number of bins to 0. If the clock input is mixing with the input signal, there may be a spur at fs/2 - fin, where fs is the ADC sample frequency and fin is the input frequency. This option could be used to notch this spur from the results if desired. Select the top entry to enable notching for this frequency. Select the other boxes below this one to notch out bins around user defined frequencies. If the user enters a "1" for number of bins to be removed, 1 bin will be removed at the frequency entered and one bin will be removed from each side of this frequency. If the user enters a "2", the bin at the frequency will be removed along with 2 bins on each side of the frequency, and so on. The GUI

User Interface

calculates the fs/2-fin frequency for informational use only in the equation box. The default value is "0" since the default value of both fs/2 and fin is "0". This value is updated when the user enters the ADC sample rate and ADC Input target frequency in the main GUI panel.

The "Highlight Notched FFT Bins in Background" option is used to highlight the area of notched frequency bins in the FFT display window.

## 3.1.4.2 2 Channel Display and Cursor Lock

If the 2 channel display option is selected, a second data capture display window will open (Figure 3-18). The user can now use this window to display the same channel but a different parameter, or a different channel if a multi-channel ADC is under test. To remove the second channel display and go back to a single channel display, click on this option again to remove the selected check mark.

Figure 3-18. Two Channel Display

When 2 channels are displayed, if Cursor lock is enabled, the cursors in the lower display is locked to the ones in the upper display.

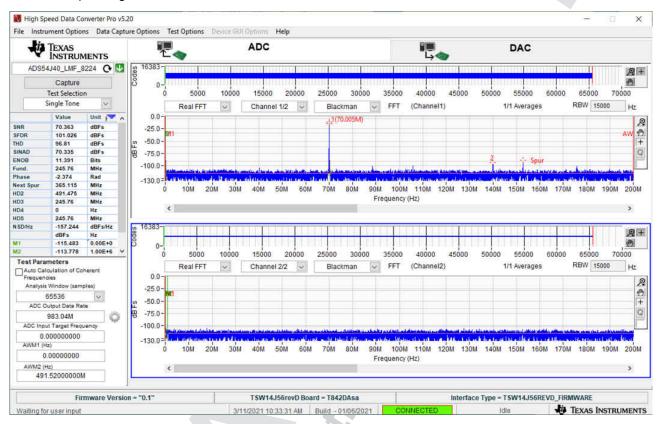

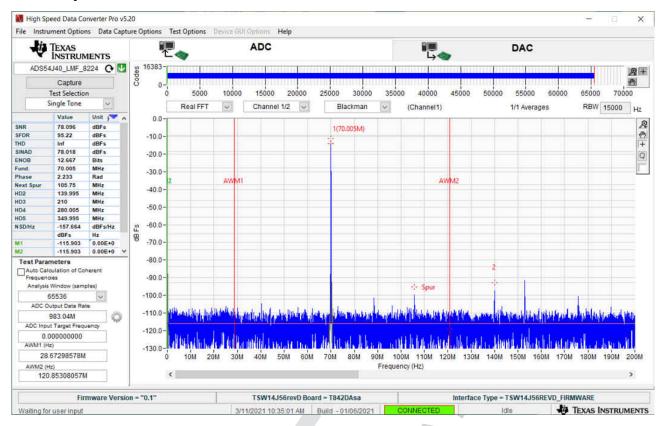

#### 3.1.4.3 Analysis Window Markers

Figure 3-19. Analysis Window Marker Example

When this option is selected, two new markers labeled AWM1 and AWM2 will appear on the FFT plot when using the GUI in Single Tone mode only. All of the calculated AC performance statistics in the left column will only use the captured values between these window markers for the calculations. The default location of marker AWM1 is at 0 MHz and marker AWM2 is at ½ the ADC sample rate (Nyquist). The location of these markers can be set either by entering a frequency value (in Hertz) in the AWM1 and AWM2 location boxes located in the bottom left corner of the GUI or by clicking on the markers directly and dragging them with the computer mouse. The AC parameters update immediately after the markers have been moved. Figure 3-19 shows an example of the Analysis Window Markers being used to display AC parameters inside a 90-MHz analysis window centered around a 70-MHz tone inside the FFT.

#### 3.1.4.4 X-Scale in Time

When using the Time Domain option, the user can change the X-scale of the display from samples to time (µs).

## 3.1.4.5 Y-Scale in Voltage

When using the Time Domain option (Test Selection in 'Time Domain'), the user can change the Y-scale of the top graphical display of the GUI from Codes to Voltage. The default setting is Codes.

## 3.1.4.6 Other Frequency Options

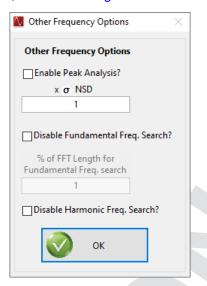

The Other Frequency Options menu has 3 features - Peak Analysis, Disable Fundamental Frequency Search, and Disable Harmonic Frequency Search, as shown in Figure 3-20.

Figure 3-20. Other Frequency Options Menu

## **Peak Analysis**

When Peak Analysis is enabled, it finds the other peaks above the average noise floor (those other than fundamental, harmonics, and next spur) and marks them from "A" to "Z", based on the amplitude of the peaks. The threshold is set as n number of standard deviations above the noise floor and will be shown as a horizontal line in the graph when enabled.

## **Disable Fundamental Frequency Search**

When Disable Fundamental Frequency Search is enabled, the GUI takes the user-provided *Input Target Frequency* as the location of the fundamental (and will not search the entire FFT for the fundamental). This option is typically used if there is a spur or harmonic frequency whose amplitude is greater than the actual signal frequency's amplitude. By default, this selection is inactive, and the software searches the spectrum for the largest signal as the fundamental frequency.

#### **Disable Harmonic Frequency Search**

When Disable Harmonic Frequency Search is enabled, the GUI will no longer search the entire FFT for harmonics. By default, this selection is inactive, and the software searches the spectrum to find four harmonics (HD2 - HD5).

#### 3.1.4.7 NSD Marker

When this option is selected, a horizontal marker (in red) representing the *Noise Spectral Density* will appear on the FFT plot when using the GUI in Single Tone mode only. Refer to Appendix A.8 for additional details.

## 3.1.4.8 Phase Plot

When this option is selected, the GUI will plot phase of the captured signal (in radian) on the FFT window.

# 3.1.4.9 Phase in Degree

Enabling this option will display phase in degrees. Disabling this option will revert phase display to radians.

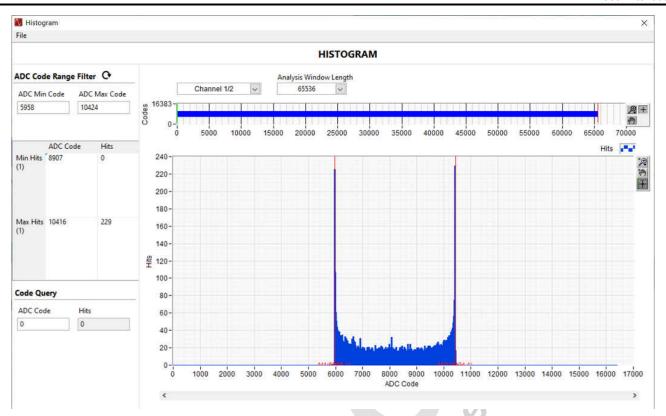

## 3.1.4.10 Histogram

Clicking on this feature will open a new window that displays a histogram of codes from the data in HSDC Pro, as shown in Figure 3-21.

Figure 3-21. Code Histogram

The analysis window length should match the number of samples from the data capture, in order to get a histogram analysis for full capture data. In order to analyze the ADC Codes over a particular section of capture length, set the required "Analysis Window Length" appropriately and move the green cursor over the length of the context plot graph to include the desired section of ADC capture data to be considered for Histogram analysis.

## 3.1.5 Help

Clicking on the help tab opens a window with five options. The first option, labeled "About", opens a status window displaying the current version of the GUI, the software DLL, the loaded firmware, and patch version.

The second option labeled "Debug Support", enables a debug email option. With this option enabled, if a GUI error occurs, the software prompts the user that it is emailing a debug log to a TI support team. For every subsequent error until the user disables this feature, the GUI will silently send the log file. The third option, labeled "Check for Updates", will verify if the user's GUI is the latest version available on the TI website.

The fourth option, labeled "EVM GUI Help", opens a window displaying the contents of the User's Guide, allowing the user to search for topics regarding the operation of the GUI.

The fifth option, labeled "Version History", opens a window showing the revision history of the HSDC Pro GUI.

## 3.2 Status Windows

The HSDC Pro GUI reports system status such as downloading, capturing, warnings, errors, and informational output in several locations. In the lower right portion of the screen, when the GUI is loading the FPGA, loading data to memory, or performing a data capture, a rolling bar will appear in place of the IDLE message. A new window will also open in the middle of the screen describing what the GUI is currently doing. An example showing the status windows during a firmware load is shown in Figure 3-22.

Figure 3-22. Status Window

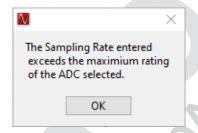

During operation of the HSDC Pro GUI software, warnings may appear in the center status window if selections made from the drop-down menus of the interface are incompatible with the hardware selections or settings. For example, if a sample rate is entered that is faster than that supported by a particular ADC data sheet, a warning appears as shown in Figure 3-23.

Figure 3-23. Center Status Window

## 3.3 Mode Selection

The first selection a user needs to make is to select the type of EVM that is to be tested with the TSW14xxx EVM. The user will click on either the "ADC" or "DAC" button located at the top of the GUI as shown in Figure 3-24.

Figure 3-24. TSW1400 and TSW14J5x Modes

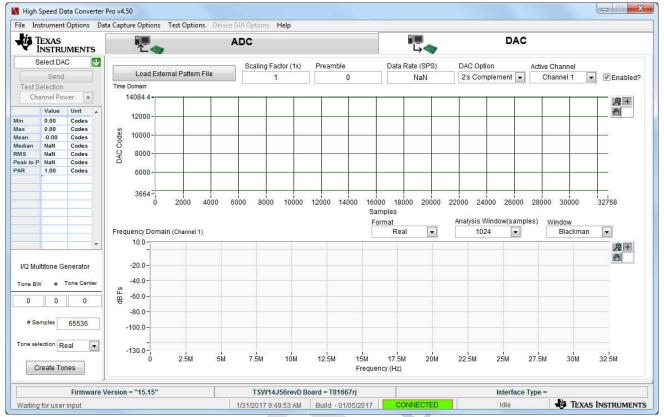

The mode selected will determine the main screen format. When ADC is selected, the GUI will be setup for displaying ADC data capture results. If DAC is selected, the GUI will setup controls to load a test pattern, create a test pattern, and display the graphical representation of the test pattern to be sent to a DAC EVM once the file has been read by the GUI.

User Interface

#### 3.4 Device Selection

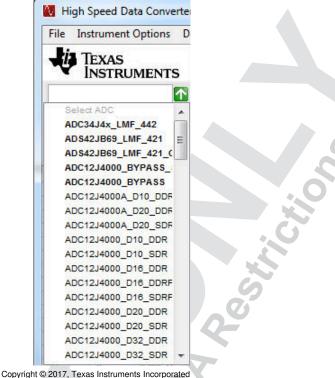

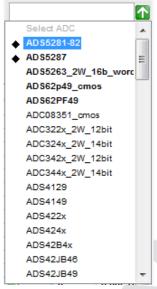

After the board mode has been set, the user needs to select the device to be tested from the device selection drop-down menu. If the GUI is in ADC mode, clicking on the drop down arrow will display the ADC options available, as shown in Figure 3-25. If in DAC mode, the list will display available DAC's.

Figure 3-25. ADC Device Selection Window

Each device that has an ini file installed in the proper directory automatically has an entry in the device selection drop-down menu.

## 3.5 Capture Button (ADC Mode Only)

The Capture button initiates a data capture once all other selections are made. The data capture can be a single capture and display, or a continuous repeating capture (Capture option under Data Capture Option tab in Tool Bar). When continuous capture is enabled, this button display will change from "Capture" to "Stop". Clicking on this button when in this mode will stop the continuous capture. After a captured has been issued, the GUI will store the setups currently used. If the GUI is closed and then re-opened, most of the settings will be restored if the original firmware is still present in the FPGA.

## 3.6 Test Selection (ADC Mode only)

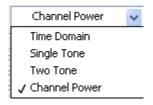

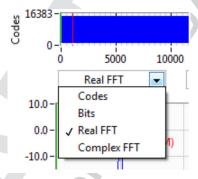

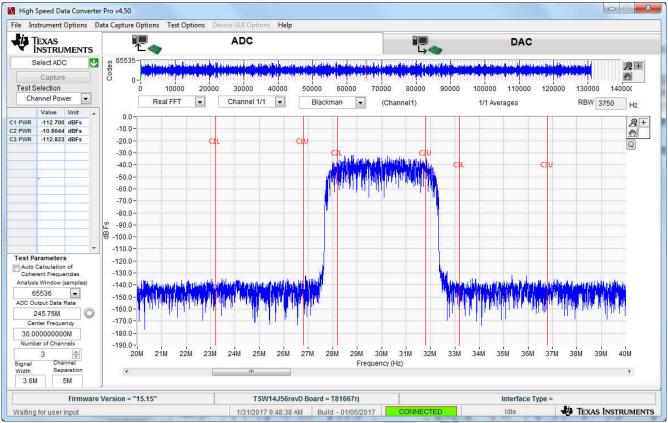

The Test Selection drop-down has options for displaying data as a Time Domain, Single Tone, Two Tone, or Channel Power, as shown in Figure 3-26. The Single Tone FFT displays the power spectrum of the captured data with calculated AC performance statistics. Time Domain displays the raw captured data in the format of a logic analyzer display and output level over time. Two tone mode sets up cursors and displays results normally used with this type of testing. Channel Power will place cursors around the channels selected by the user (up to 5) and report the power of each.

Figure 3-26. Test Selection Drop-Down Options

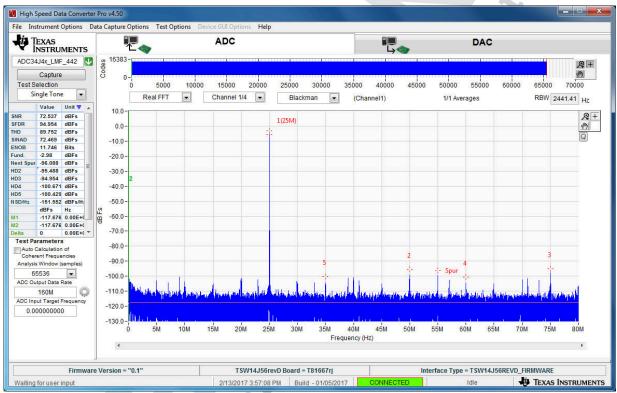

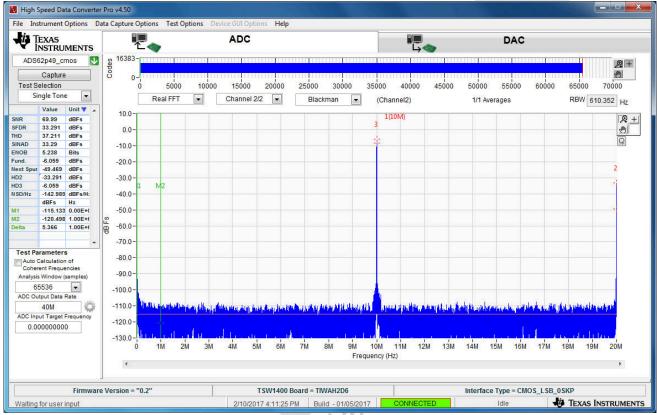

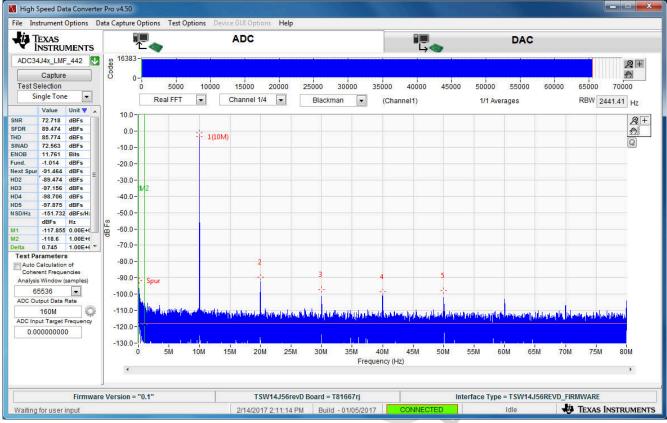

## 3.6.1 Single Tone FFT

The Single Tone FFT screen is shown in Figure 3-27. The larger central pane displays the FFT power spectrum, whereas the calculated statistics are grouped into categories on the left side of the screen. Settings and inputs relevant to the test are entered in drop-down menus or text input boxes on the bottom left portion of the window.

The red horizontal line shown is the RMS line. This line indicates the RMS average of the noise floor of the FFT plot. The RMS average is computed over all of the FFT bins except the bin containing the input frequency. More precisely, the RMS line = SINAD + FFT Record Length Process Gain where FFT Record Process Gain = 10log(number of points/2).

Copyright © 2017, Texas Instruments Incorporated

Figure 3-27. Single Tone FFT Display

## 3.6.1.1 Parameter Controls

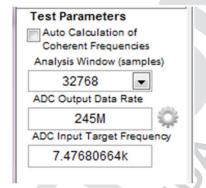

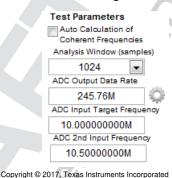

The output data rate is entered in the ADC Output Data Rate text box. In most cases this value will be the same as the sample rate of the ADC. For parts that support decimation, this value is usually lower. For example, this number is usually 2x lower if the part decimates by 2 and 4x lower if it decimates by 4. The number is entered in Hertz (Hz), although the letter M may be appended to represent the sampling rate in MHz. For example, 125M = 125 MHz or 125,000,000 Hz.

The expected input frequency is entered in the ADC Input Target Frequency text box. If the Auto Calculation of Coherent Input Frequency mode is enabled, then this input frequency is adjusted up or down slightly away from the input frequency automatically. If coherent input frequency is required, the signal generator used to source

the input frequency must be set to this exact calculated coherent frequency. The coherent frequency calculation takes the ADC sampling rate, the input frequency as entered by the user in Hertz, and the FFT record length and adjusts the input frequency so that the captured data starts and ends on the same place of the sine wave of the input frequency. This avoids an artifact of the FFT calculation from presenting a smeared power spectrum due to the fact that the FFT presumes the sample of the input is part of a continuous input signal. If the input and sampling frequency is not coherent, and the sampled data is appended end to end to form a continuous input signal, then there is an apparent phase discontinuity at the beginning and the end of the sampled data. Making the sampling and input frequencies coherent avoids this apparent discontinuity. If the input frequency cannot be made coherent, then the windowing functions other than Rectangular can be used to process out this effect to some degree.

The FFT record length can be set in the Analysis Window (samples) text box. The TSW1400 and TSW14J5x EVMs support FFT analysis lengths of as much as 524,288 samples, or as little as 1024 samples. In order to analyze the ADC Samples over a particular section of capture length, set the required "Analysis Window (samples)" appropriately and move the green cursor over the length of the context plot graph to include the desired section of ADC capture data to be considered for analysis. The red vertical line shown in the codes graph represents where the last sample is used from the captured data for analysis. The GUI will only allow record lengths that are the same size or smaller than the number of captured samples, which is set by the value in the capture option under the Data Capture Options tab (See Section 3.1.3.1). The default value is 65,536.

Figure 3-28. Test Parameters

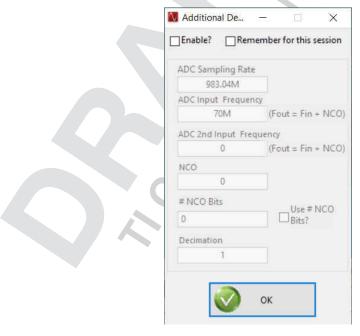

Clicking on the Settings button (a gear) near the 'ADC Output Data Rate' will open a window as shown in Figure 3-29, which allows the user to specify the additional device parameters. Check "Enable" to enable this option.

Figure 3-29. Additional Device Parameters

This additional setting is used to calculate the exact location of the spurs in the captured tone based on the following device parameters:

*ADC Sampling Rate* – Actual ADC sampling rate from the device. The ADC Output Data Rate value displayed in Figure 3-28 will be (Actual ADC Sampling Rate / Decimation).

ADC Input Target Frequency – Actual signal frequency on the device input.

ADC 2nd Input Target Frequency - Actual signal frequency on the second device input.

NCO – NCO frequency configured in the device that goes to the mixer. The NCO frequency provides a frequency shift of specified frequency value to the input tone. The spur search algorithm in HSDC Pro will account for this and identify the spurs properly.

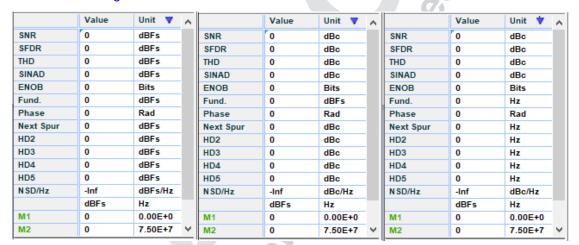

# of NCO Bits – Number of NCO accuracy bits used in adjusting the user specified NCO frequency. To include the same amount in the calculation of NCO frequency, check on the "Use # NCO Bits?" The formula used to modify the User Specified NCO Frequency, based on the number NCO accuracy bits is given below. In order to use the # of NCO Bits, the "Auto Calc of Coherent Frequencies" should be enabled.