# Interfacing Op Amps to High-Speed DACs, Part 1: Current-Sinking DACs

Jim Karki Member, Technical Staff, High-Performance Analog

#### ABSTRACT

This article shows a circuit implementation using a single-stage op amp to convert complementary-current outputs from a current-sinking DAC to a single-ended voltage.

#### Contents

| 1 | Introduction                                                | 2  |

|---|-------------------------------------------------------------|----|

|   | Overview of Complementary-Current-Steering DAC              |    |

| 3 | Architecture and Compliance Voltage of Current-Sinking DACs | 3  |

|   | Op Amp Interface                                            |    |

| 5 | Design Example and Simulation                               | 7  |

| 6 | DAC Image-Filter Considerations                             | 9  |

| 7 | Conclusion                                                  | 13 |

| 8 | Related Web Sites                                           | 13 |

#### List of Figures

| 1  | Simplified Block Diagram of Current-Steering DAC                                     | 2  |

|----|--------------------------------------------------------------------------------------|----|

| 2  | Simplified NMOS and NPN Current Sinks                                                | 3  |

| 3  | Proposed Circuit for an Op Amp Interface                                             | 4  |

| 4  | Positive Side of Analysis Circuit                                                    | 4  |

| 5  | Negative Side of Analysis Circuit                                                    | 5  |

| 6  | Simulation of Current-Sinking DAC Interfaced to Op Amp                               | 8  |

| 7  | Inserting DAC Image Filter                                                           | 9  |

| 8  | Simulation of AC Transfer Function With Matched vs. Unmatched Filter Implementations | 11 |

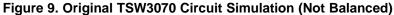

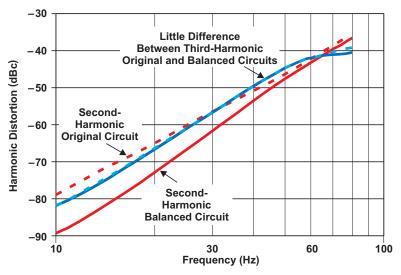

| 9  | Original TSW3070 Circuit Simulation (Not Balanced)                                   | 12 |

| 10 | Harmonic Distortion With Balanced Versus Unbalanced Impedance                        | 12 |

|    |                                                                                      |    |

#### List of Tables

| 1 | Example of I <sub>OUT1</sub> and I <sub>OUT2</sub> Currents for 20-mA Full Scale | 2 |

|---|----------------------------------------------------------------------------------|---|

|---|----------------------------------------------------------------------------------|---|

TINA-TI is a trademark of Texas Instruments. WinZip is a trademark of Microsoft. Excel is a registered trademark of Microsoft. All other trademarks are the property of their respective owners.

#### 1 Introduction

Digital-to-analog converters (DACs) come in many bit resolutions and sampling speeds. Outputs from lower-speed DACs are often single-ended and have either a voltage or a current output. Most highspeed DACs are designed with complementary outputs that either source or sink current. This article, Part 1 of a three-part series, discusses the interface between a current-sinking DAC and an op amp. Part 2, which will appear in a future issue of the *Analog Applications Journal*, will discuss the interface between a current-sourcing DAC and an op amp. Part 3, also in a future issue of the *Analog Applications Journal*, will provide a simplified approach to the interface analogy presented in Part 2.

High-speed DACs are used in endequipment applications like communications, test equipment, medical applications, industrial applications, and others that require signal generation. Each of these applications has its own specific requirements for signal characteristics and performance. This article series focuses on end equipment that requires DC coupling, such as signal generators with frequency bandwidths of up to 100 MHz and a single-ended output. In these cases, high-speed op amps can provide a good solution for converting the complementary-current output from a high-speed DAC to a voltage that can drive the signal output.

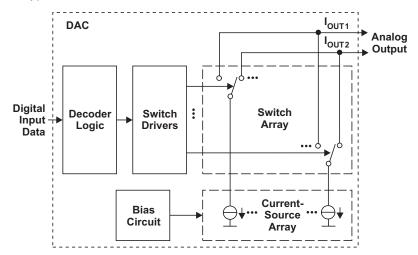

#### 2 Overview of Complementary-Current-Steering DAC

A simplified block diagram of a complementary-currentsteering DAC is shown in Figure 1. The digital input is decoded for the switch drivers that switch or steer the appropriate current sources in the current-source array to the outputs,  $I_{OUT1}$  and  $I_{OUT2}$ .  $I_{OUT1}$  and  $I_{OUT2}$  are complementary, so if current flows out of one it is subtracted from the other and vice versa, keeping the total current constant. For example, if full scale is 20 mA, the minimum code input or zero-scale input may provide 0 mA at  $I_{OUT1}$  and 20 mA at  $I_{OUT2}$ . At midscale, each output provides 10 mA; and at maximum or full scale,  $I_{OUT1} = 20$  mA and  $I_{OUT2} = 0$  mA. This example is illustrated in Table 1. It is important to note that the midscale input, with each output at 10 mA, sets the output common-mode condition for the design.

The current-source array is constructed with either n-type or p-type transistors. The word "source" is used generically to refer to the transistor circuit structure, which may either source or sink current. This article considers the interface between a current-sinking DAC and an op amp where the source array is constructed with n-type transistors.

Figure 1. Simplified Block Diagram of Current-Steering DAC

| Input         | I <sub>out1</sub> (mA) | I <sub>OUT2</sub> (mA) |

|---------------|------------------------|------------------------|

| Maximum Scale | 20                     | 0                      |

| Midscale      | 10                     | 10                     |

| Zero Scale    | 0                      | 20                     |

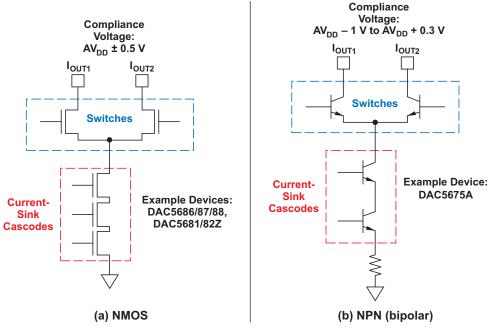

# 3 Architecture and Compliance Voltage of Current-Sinking DACs

Figure 2 shows simplified examples of NMOS and NPN current sinks and lists a few devices that use them. The compliance voltage shown for each group of devices is the voltage range at the DAC outputs within which a device will perform as specified. Lower voltages tend to shut down the outputs, and higher voltages have the potential to cause breakdown. Both of these should be avoided to provide the best performance and long-term reliability.

Generally the output is terminated by impedance to a positive power supply. This impedance supplies a current path needed for the sink array, and the voltage drop across the same impedance can be a voltage output. The impedance can be constructed in various ways; it can be a simple resistor divider, a transformer-coupled impedance, or a combination of passive components and an active circuit. This article focuses on the latter option, with an op amp as the active circuit.

Figure 2. Simplified NMOS and NPN Current Sinks

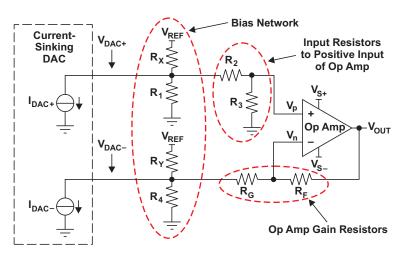

# 4 Op Amp Interface

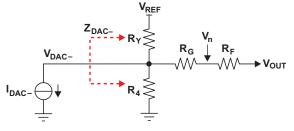

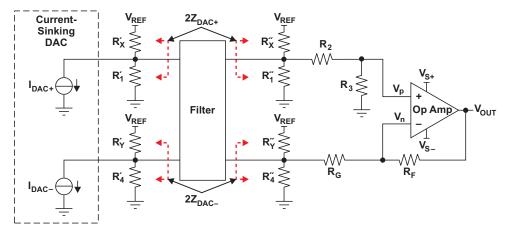

The proposed op amp interface is shown in Figure 3. This circuit provides biasing of the DAC outputs, converts the DAC currents to voltages, and provides a single-ended output voltage through the op amp. The op amp is the active amplifier element for the circuit and uses  $R_2$ ,  $R_3$ ,  $R_G$ , and  $R_F$  to make a difference amplifier.

- $I_{DAC+}$  and  $I_{DAC-}$  are the current outputs from the DAC.

- R<sub>2</sub> and R<sub>3</sub> are input resistors to the positive input of the op amp.

- $R_G$  and  $R_F$  are the main gain-setting resistors for the op amp.

- $R_X$ ,  $R_1$ ,  $R_Y$ , and  $R_4$  provide bias and impedance termination for the DAC outputs.

- $V_{DAC+}$  and  $V_{DAC-}$  are the voltages at the outputs of the DAC.

- $V_p$  and  $V_n$  are the input terminals of the op amp.

- $V_{S+}$  and  $V_{S-}$  are the power supplies to the op amp.

Op Amp Interface

Figure 3. Proposed Circuit for an Op Amp Interface

Proper component selection provides the impedance required to maintain voltage compliance with maximum amplitude, and balance for the best performance.

Typically, harmonic distortion in an op amp is dominated (at least at lower frequencies) by the secondorder harmonics. Balanced inputs to the difference-amplifier circuit will help suppress second-order harmonics and provide for the best performance, but little impact is expected on third-order harmonics if the inputs are not balanced.

For analysis, it is easiest to break the circuit into positive and negative halves and examine each separately. Assume that the op amp is ideal.

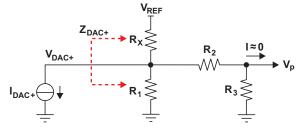

## 4.1 Analysis of Positive Side

Figure 4. Positive Side of Analysis Circuit

The positive half of the circuit is shown in Figure 4. To start the analysis, use Kirchhoff's current law to write a node equation at  $V_{DAC+}$ :

$$I_{DAC+} + \frac{V_{DAC+} - V_{REF}}{R_X} + \frac{V_{DAC+}}{R_1} + \frac{V_{DAC+}}{R_2 + R_3} = 0$$

(1)

The input impedance can be expressed as:

$Z_{DAC+} = R_X || R_1 || (R_2 + R_3)$

Equation 1 and Equation 2 are simultaneous equations with many variables, and designers must choose or identify values based on other design criteria to solve them. The following assumptions are made for this article:

- The DAC output current, I<sub>DAC+</sub>, and the voltage swing, V<sub>DAC+</sub>, are defined by the designer, which sets a target value for Z<sub>DAC+</sub>.

- An existing circuit voltage or other known voltage is used for V<sub>REF</sub>.

- In a difference amplifier,  $R_3/R_2$  must equal  $R_F/R_G$  to balance the gain of the amplifier. Note that in a voltage-feedback op amp, it is desirable to make the impedance at  $V_p$  equal to that at  $V_n$  to cancel

(2)

Copyright © 2009, Texas Instruments Incorporated

voltage offset caused by the input bias current. In a current-feedback op amp, the input bias currents are not correlated; so it is acceptable not to balance these impedances, but it may be desirable to minimize them.

The equations are solved for the condition where the DAC current on the positive side is zero: I<sub>DAC+</sub> = 0 mA. This sets the DAC voltage on the positive side to its maximum value, V<sub>DAC+</sub> = V<sub>DAC+</sub>(max).

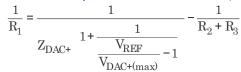

With these constraints, the designer can apply algebra and simultaneous-equation techniques to Equation 1 and Equation 2 to solve for  $1/R_1$ :

(3)

The known value for  $R_1$  can be substituted into Equation 2, which can then be rearranged to find  $1/R_X$ :

$$\frac{1}{R_X} = \frac{1}{Z_{DAC^+}} - \frac{1}{R_1} - \frac{1}{R_2 + R_3}$$

(4)

#### 4.2 Analysis of Negative Side

Figure 5. Negative Side of Analysis Circuit

The negative half of the circuit is shown in Figure 5. Analysis of the negative side is complicated, because  $V_n$  is driven not only by the negative side of the DAC, but also by the positive side through the op amp action. To start the analysis, use Kirchhoff's current law to write a node equation at  $V_{DAC}$ .

$$I_{DAC-} + \frac{V_{DAC-} - V_{REF}}{R_{Y}} + \frac{V_{DAC-}}{R_{4}} + \frac{V_{DAC-} - V_{n}}{R_{G} + R_{3}} = 0$$

(5)

The input impedance can be expressed as:

$$Z_{\text{DAC}-} = \frac{V_{\text{DAC}-}}{I_{\text{DAC}-}}$$

(6)

With substitution and rearrangement, the designer can use:

$$V_{\rm p} = V_{\rm DAC+} \times \frac{R_3}{R_2 + R_3}$$

(7)

and  $V_n = \alpha V_p$  to rewrite Equation 6 as:

$$\frac{1}{Z_{\text{DAC}-}} = \frac{1}{\frac{Z_{\text{DAC}+} \times \alpha \left(\frac{R_3}{R_2 + R_3}\right)}{1 - \frac{Z_{\text{DAC}+} \times \alpha \left(\frac{R_3}{R_2 + R_3}\right)}{R_{\text{G}}}} \times \left(\frac{1}{R_{\text{Y}}} + \frac{1}{R_4} + \frac{1}{R_{\text{G}}}\right)$$

(8)

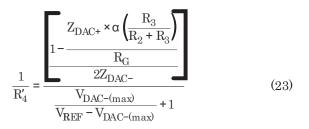

Using the same substitutions and general design constraints used on the positive side to drive values for  $Z_{DAC_-}$ ,  $V_{REF}$ , and  $R_G$ , simultaneous-equation techniques can be applied to Equation 5 and Equation 8 to solve for  $1/R_4$  (Equation 9). Note that the equations are solved for the condition where the DAC current on the negative side is zero:  $I_{DAC_-} = 0$  mA. This sets the DAC voltage on the negative side to its maximum value,  $V_{DAC_-} = V_{DAC_-}(max)$ , and sets the DAC voltage on the positive side to its minimum value,  $V_{DAC_+} = V_{DAC_+}(min)$ .

(9)

**Op Amp Interface**

$$\frac{1}{R_{4}} = \frac{\frac{1 - \frac{Z_{DAC+} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right)}{R_{G}}}{Z_{DAC-}} + \left[\frac{V_{DAC+(min)} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right) - V_{DAC-(max)}}{V_{REF} - V_{DAC-(max)}} - 1\right] \left(\frac{1}{R_{G}}\right)}{\frac{V_{DAC-(max)}}{V_{REF} - V_{DAC-(max)}} + 1}$$

The value of  $1/R_4$  can then be used to find  $1/R_Y$ :

$$\frac{1}{R_{Y}} = \frac{\frac{Z_{DAC+} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right)}{Z_{DAC-}} - \left(\frac{1}{R_{4}} + \frac{1}{R_{G}}\right)$$

(10)

Note that  $\alpha$ , the multiplication factor from V<sub>p</sub> to V<sub>n</sub>, expresses the difference between the input pins. In a voltage-feedback amplifier,  $\alpha$  is set by the loop gain of the amplifier. In a current-feedback amplifier,  $\alpha$  is the gain of the input buffer between the inputs.  $\alpha$  is typically close enough to 1 that it can be removed from the calculation.

#### 4.3 Calculating Output Voltage

Superposition can be used to write equations for the separate sources referred to  $V_{OUT}$ . Since the DAC only sinks current, which is by convention negative current flow, the output-voltage swing is the opposite of what might be expected. In other words, when the DAC is sinking current on the positive side, the output of the op amp tends to swing negative, and when the DAC is sinking current on the negative side, the output of the op amp tends to swing positive. Thus, in the following equations  $I_{DAC+}$  and  $I_{DAC-}$  are always negative or zero.

The output-referred DC bias from the positive side is:

$$V_{OUT_{-}V_{p(DC)}} = \left(1 + \frac{R_{F}}{R_{G} + R_{Y}||R_{4}}\right) \times \left[V_{REF} \times \frac{R_{1}R_{3}}{R_{1}(R_{2} + R_{3}) + R_{X}(R_{1} + R_{2} +)R_{3}}\right]$$

(11)

The output-referred DAC signal from the positive side is:

$$V_{OUT_{-}V_{p}(DAC)} = \left(1 + \frac{R_{F}}{R_{G} + R_{Y} || R_{4}}\right) \times \left[I_{DAC+} \times \frac{R_{X}R_{1}R_{3}}{R_{X}R_{1} + (R_{1} + R_{X})(R_{2} + R_{3})}\right]$$

(12)

The output-referred DC bias from the negative side is:

$$V_{OUT_V_{n(DC)}} = -\left(V_{REF} \times \frac{R_4}{R_Y + R_4} \times \frac{R_F}{R_G + R_Y || R_4}\right)$$

(13)

The output-referred DAC signal from the negative side is:

$$V_{OUT_{-}V_{n}(DAC)} = -\left(I_{DAC^{-}} \times \frac{R_{Y}R_{4}R_{F}}{R_{Y}R_{4} + R_{G}R_{4} + R_{Y}R_{G}}\right)$$

(14)

Adding these four equations provides an expression for  $V_{\mbox{\scriptsize OUT}}$ :

$$V_{OUT} = V_{OUT_{-}V_{p(DC)}} + V_{OUT_{-}V_{p(DAC)}} + V_{OUT_{-}V_{n(DC)}} + V_{OUT_{-}V_{n(DAC)}}$$

(15)

If it is assumed that  $I_{DAC} = I_{DAC+} - I_{DAC-}$ ,  $Z = Z_{DAC+} = Z_{DAC-}$ , and  $R_F/R_G = R_3/R_2$ , the DC component of the DAC outputs will cancel, and the AC signal gain equation from the DAC output current to the voltage output of the op amp can be simplified and written as:

$$\frac{V_{OUT}}{I_{DAC}} = 2Z \times \frac{R_F}{R_G}$$

(16)

#### 5 Design Example and Simulation

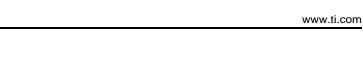

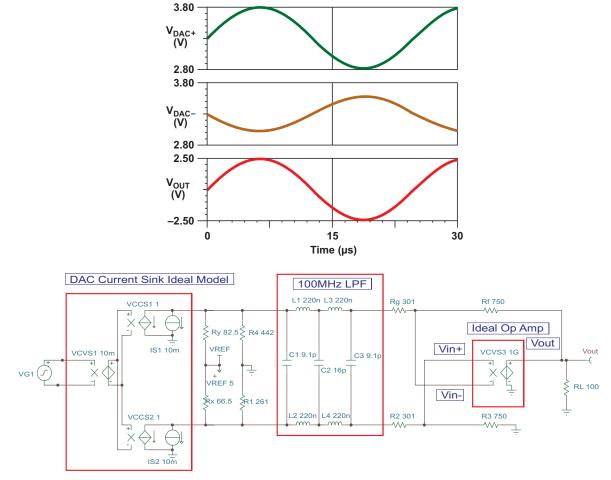

For an example of how to proceed with the design, assume use of one of the NMOS DACs noted earlier, with a compliance voltage of 3.3 ±0.5 V. Also assume that the full-scale output is set to 20 mA. To get a 5-V<sub>PP</sub>, DC-coupled, single-ended output signal, use the circuit shown in Figure 3. Because a ±5-V power supply is being used for the op amp, set  $V_{REF} = 5$  V. Given that  $I_{DAC\pm} = 20$  mA and  $V_{DAC\pm} = 1$   $V_{PP}$ , the target impedance,  $Z_{DAC\pm}$ , can be calculated to equal 50  $\Omega$ .

With the starting design constraints given earlier, the THS3095 current-feedback op amp is selected as the amplifier, where  $R_3 = R_F = 750 \ \Omega$ . The gain from  $V_{DAC\pm}$  to the output is given by the resistor ratios  $R_F/R_G = R_3/R_2$ , so  $R_G$  can be calculated as:

$$R_{G} = R_{2} = R_{F} \times \frac{V_{DAC\pm}}{V_{OUT}} = 750 \,\Omega \times \frac{2(1 \, V)}{5 \, V} = 300 \,\Omega$$

(17)

Use the nearest standard 1% value, 301  $\Omega$ .

Equation 3, Equation 4, Equation 9, and Equation 10 can be used to find, respectively, R<sub>1</sub>, R<sub>x</sub>, R<sub>4</sub>, and R<sub>y</sub>:

$$R_{1} = \frac{1}{\frac{1}{Z_{DAC+} \left(1 + \frac{1}{\frac{V_{REF}}{V_{DAC+(max)}} - 1}\right)^{-} \frac{1}{R_{2} + R_{3}}} = \frac{1}{\frac{1}{\frac{1}{50 \Omega \left(1 + \frac{1}{\frac{5 V}{3.8 V} - 1}\right)^{-} \frac{1}{301 \Omega + 750 \Omega}}} = 259.8 \Omega$$

$$R_{X} = \frac{1}{\frac{1}{Z_{DAC^{+}}} - \frac{1}{R_{1}} - \frac{1}{R_{2} + R_{3}}} = \frac{1}{\frac{1}{50 \Omega} - \frac{1}{259.8\Omega} - \frac{1}{301\Omega + 750\Omega}} = 65.8 \Omega$$

$$R_{4} = \frac{\frac{V_{DAC-(max)}}{V_{REF} - V_{DAC-(max)}} + 1}{\frac{Z_{DAC+} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right)}{Z_{DAC-}} + \left[\frac{V_{DAC+(min)} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right) - V_{DAC-(max)}}{V_{REF} - V_{DAC-(max)}} - 1\right] \left(\frac{1}{R_{G}}\right)$$

$$= \frac{\frac{3.8 V}{5 V - 38 V} + 1}{\frac{1 - \frac{50 \Omega \times 1 \times \frac{750 \Omega}{301 \Omega + 750 \Omega}}{5 0 \Omega}}{\frac{301 \Omega}{5 0 \Omega}} + \left(\frac{2.8 V \times 1 \times \frac{750 \Omega}{301 \Omega + 750 \Omega} - 3.8 V}{5 V - 38 V} - 1\right) \left(\frac{1}{301 \Omega}\right)$$

$$R_{Y} = \frac{1}{\frac{Z_{DAC^{+}} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right)}{1 - \frac{R_{G}}{Z_{DAC^{-}}} - \left(\frac{1}{R_{4}} + \frac{1}{R_{G}}\right)} = \frac{1}{\frac{1 - \frac{50 \,\Omega \times 1 \times \frac{750 \,\Omega}{301 \,\Omega + 750 \Omega}}{301 \,\Omega}}{50 \,\Omega} - \left(\frac{1}{447.2 \,\Omega} + \frac{1}{301 \Omega}\right)}$$

(18)

DAC Current Sink Ideal Model

Figure 6. Simulation of Current-Sinking DAC Interfaced to Op Amp

The nearest standard 1% values should be used:  $R_1 = 261 \Omega$ ,  $R_x = 66.5 \Omega$ ,  $R_4 = 442 \Omega$ , and  $R_y = 82.5 \Omega$ .

(V) -2.52

0

15

Time (µs)

These equations are more easily solved when set up in a spreadsheet. To see an example Excel<sup>®</sup> worksheet, go to <u>http://www.ti.com/lit/zip/slyt342</u> and click Open to view the WinZip<sup>™</sup> directory online (or click Save to download the WinZip file for offline use). Then open the file DAC\_\_\_\_\_\_\_ Sink\_to\_Op\_Amp\_Wksht.xls and select the "DAC Sink to Op Amp, No Filter" worksheet tab.

SPICE simulation is an excellent way to validate the design. To see a TINA-TI<sup>™</sup> simulation of the circuit in this example, go to <u>http://www.ti.com/lit/zip/slyt342</u> and click Open to view the WinZip directory online (or click Save to download the WinZip file for offline use). If the TINA-TI software is already installed, open the file DAC\_ Sink\_to\_Op\_Amp\_No\_Filter.TSC to view the example. To download and install the free TINA-TI software, visit <u>www.ti.com/tina-ti</u> and click the Download button.

The simulation circuit and waveforms in Figure 6 show that the circuit simulates as expected.  $I_{DAC+}$  and  $I_{DAC-}$  are the DAC currents,  $V_{DAC+}$  and  $V_{DAC-}$  are the voltages developed at the DAC outputs, and  $V_{OUT}$  is the output of the amplifier. The current-sinking DAC and op amp are ideal elements constructed with SPICE macros, and are intended to show that the equations derived earlier for  $R_1$ ,  $R_X$ ,  $R_4$ , and  $R_Y$  are valid for ideal elements. Actual performance will vary depending on selected devices.

DAC Image-Filter Considerations

## 6 DAC Image-Filter Considerations

The DAC output signal will have the desired baseband signal, as well as the sampling images that occur at multiples of the sampling frequency. Filtering is usually used to reduce the amplitude of the sampling images, because they degrade performance. Filtering directly at the DAC output before the op amp preserves the best performance. This is especially important with multitone signals, where second-order intermodulation products from the sampling images appear at the baseband.

Filter design is not the topic of this article, so it will not be covered in detail; but for proper operation the filter component values are calculated based on the input and output impedances seen by the filter. While finding the exact value of the impedance is not difficult, it is usually easier to find standard component values to implement the filter when the input and output impedances to the filter are equal. With this in mind, consider how to achieve the same goals as before, while keeping the impedance seen by the filter balanced.

Figure 7. Inserting DAC Image Filter

Figure 7 shows the proposed circuit implementation.  $R_1$ ,  $R_X$ ,  $R_4$ , and  $R_Y$  have been replaced with prime and double-prime components on either side of the filter, where

$R_1 = R'_1 || R''_1,$

$\mathsf{R}_\mathsf{X} = \mathsf{R}'_\mathsf{X} \mid\mid \mathsf{R}''_\mathsf{X},$

$R_4 = R'_4 || R''_4$ , and

$$\mathsf{R}_\mathsf{Y} = \mathsf{R'}_\mathsf{Y} \mid\mid \mathsf{R''}_\mathsf{Y}.$$

With the additional constraint that the impedance seen on each terminal of the filter is  $2 \times Z_{DAC\pm}$ , the following equations can be derived by:

DAC Image-Filter Considerations

$$\frac{1}{R_{1}'} = \frac{1}{2Z_{\text{DAC}+} \left(1 + \frac{1}{\frac{V_{\text{REF}}}{V_{\text{DAC}+(\text{max})}} - 1}\right)}$$

(19)

$$\frac{1}{R_{1}'} = \frac{1}{2Z_{DAC+} \left(1 + \frac{1}{\frac{V_{REF}}{V_{DAC+(max)}} - 1}\right)} - \frac{1}{R_{2} + R_{3}}$$

(20)

$$\frac{1}{R'_X} = \frac{1}{2Z_{DAC^+}} - \frac{1}{R'_1}$$

(21)

$$\frac{1}{R'_{X}} = \frac{1}{2Z_{DAC^{+}}} - \frac{1}{R'_{1}} - \frac{1}{R_{2} + R_{3}}$$

(22)

$$\frac{1}{R_{4}^{\prime}} = \frac{\frac{1 - \frac{Z_{DAC^{+}} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right)}{R_{G}}}{2Z_{DAC^{-}}} + \frac{V_{DAC^{+}(\min)} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right) - V_{DAC^{-}(\max)}}{V_{REF} - V_{DAC^{-}(\max)}} - 1 \left(\frac{1}{R_{G}}\right)}{\frac{V_{DAC^{-}(\max)}}{V_{REF} - V_{DAC^{-}(\max)}}} + 1}$$

(24)

$$\frac{1}{R'_{Y}} = \frac{\frac{Z_{DAC^{+}} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right)}{R_{G}}}{\frac{1}{2Z_{DAC^{-}}}} - \frac{1}{R'_{4}}$$

(25)

$$\frac{1}{R_{Y}'} = \frac{\frac{Z_{DAC^{+}} \times \alpha \left(\frac{R_{3}}{R_{2} + R_{3}}\right)}{2Z_{DAC^{-}}} - \left(\frac{1}{R_{4}'} + \frac{1}{R_{G}}\right) \quad (26)$$

These equations are more easily solved when set up in a spreadsheet. To see an example Excel worksheet, go to <u>http://www.ti.com/lit/zip/slyt34</u>2 and click Open to view the WinZip directory online (or click Save to download the WinZip file for offline use). Then open the file DAC\_Sink\_ to\_Op\_Amp\_Wksht.xls and select the "DAC Sink to Op Amp, With Filter" worksheet tab.

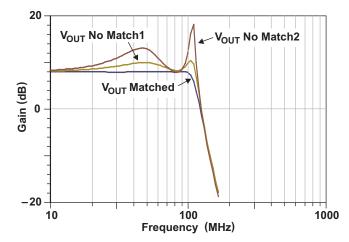

SPICE simulation is an excellent way to validate the design. To see a TINA-TI simulation comparing results with a filter used in the circuit, open the WinZip directory as described above for the worksheet. If the TINA-TI software is already installed, open the file DAC\_Sink\_to\_Op\_Amp\_ With\_Filter.TSC to view the example. To download and install the free TINA-TI software, visit www.ti.com/tina-ti and click the Download button. To show the effects of balancing the filter impedance, a 100-MHz differential filter designed for 100- $\Omega$  input and output impedance is inserted into the interface of the DAC and op amp. In the top circuit, the filter is inserted between the bias resistors and amplifier gain resistors with no regard for balancing the impedance; the output is labeled "V<sub>OUT</sub> No Match1." In the bottom circuit, the filter is labeled "V<sub>OUT</sub> No Match2." In the center circuit, the bias network is designed for 100- $\Omega$  balanced impedance; the output is labeled "V<sub>OUT</sub> Matched." The transient simulation waveforms look the same as those shown in Figure 6 for each of these circuits, but simulation of an AC transfer function (see Figure 8) shows that the unmatched implementations result in significant ripple in the frequency response while the matched design performs as desired.

#### Figure 8. Simulation of AC Transfer Function With Matched vs. Unmatched Filter Implementations

During design of the Texas Instruments TSW3070 evaluation board, a circuit was derived as shown in Figure 9 that appears to be well-balanced and that provides for proper impedance matching to the 100-MHz low-pass filter (LPF). However, the simulation waveforms of the circuit show that the impedances seen by the outputs of the DAC are not balanced, and that the voltage at  $V_{DAC+}$  is not the mirror image of that at  $V_{DAC-}$ . Per the last example given, this circuit was modified to balance the impedances for the DAC and the LPF. Performance of the second and third harmonics was tested before and after the modification, and the results (shown in Figure 10) show as much as a 10-dB improvement in the second harmonics (depending on the frequency) with basically no change in the third harmonics.

Figure 10. Harmonic Distortion With Balanced Versus Unbalanced Impedance

## 7 Conclusion

This article shows a circuit implementation using a single-stage op amp to convert complementary-current outputs from a current-sinking DAC to a single-ended voltage. Equations are derived and a methodology presented for proper selection of component values to set the DAC output-voltage compliance, while maintaining balanced input signals to the op amp for best overall performance. Filter-design considerations are also included to explain proper insertion when filtering before the amplifier is desired.

Conclusion

# 8 Related Web Sites

#### amplifier.ti.com

www.ti.com/sc/device/partnumber

(Replace *partnumber* with DAC5675A, DAC5681, DAC5682Z, DAC5686, DAC5687, DAC5688, or THS3095)

#### www.ti.com/tsw3070

TINA-TI and spreadsheet support files for examples: www.ti.com/lit/zip/slyt342

To download TINA-TI software: www.ti.com/tina-ti

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated