The DAC56X2 family datasheets do not include guaranteed timing numbers for interleaved input data mode. This document describes the internal operation and requirements for interleaved interface mode.

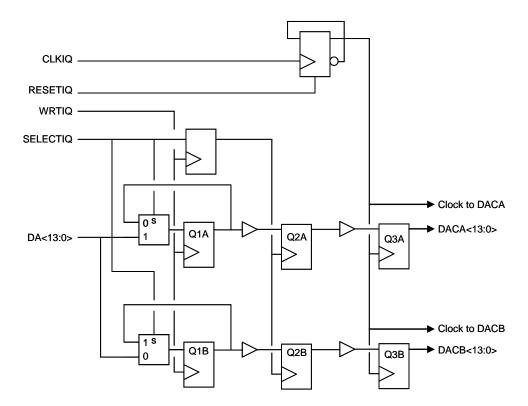

Interleaved Mode Simplified Schematic

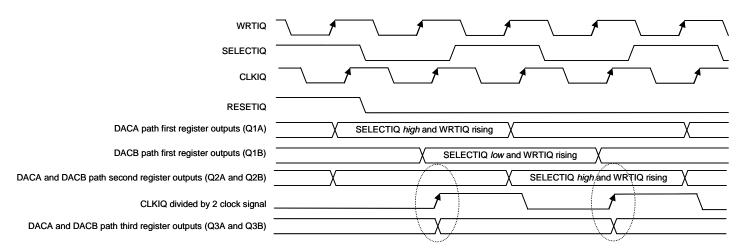

DACA and DACB (Q3A and Q3B) sample in the middle of valid data when RESETIQ is used to initialize the divide by 2 to the correct phase

Interleaved Mode Timing Diagram

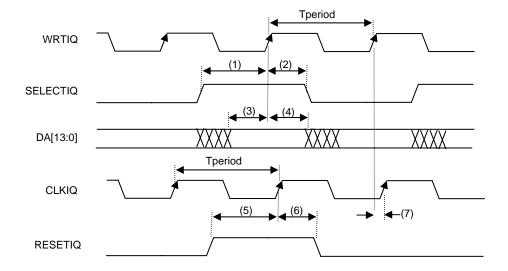

| Timing no. | Description                                             | Min | Max | Units |

|------------|---------------------------------------------------------|-----|-----|-------|

| (1)        | Setup Time: SELECTIQ rising or falling edge to          | 2.5 |     | ns    |

|            | WRTIQ rising edge                                       |     |     |       |

| (2)        | Hold Time: SELECTIQ rising or falling edge to           | 1   |     | ns    |

|            | WRTIQ rising edge                                       |     |     |       |

| (3)        | Setup Time: DA[13:0] rising or falling edge to WRTIQ    | 1   |     | ns    |

|            | rising edge                                             |     |     |       |

| (4)        | Hold Time: DA[13:0] rising or falling edge to WRTIQ     | 1   |     | ns    |

|            | rising edge                                             |     |     |       |

| (5)        | Setup Time: RESETIQ rising or falling edge to CLKIQ     | 1   |     | ns    |

|            | rising edge                                             |     |     |       |

| (6)        | Hold Time: RESETIQ rising or falling edge to CLKIQ      | 1   |     | ns    |

|            | rising edge                                             |     |     |       |

| (7)        | If RESETIQ is used to initialize the internal CLKIQ     |     |     |       |

|            | divider to the correct phase, CLKIQ and WRTIQ can be    |     |     |       |

|            | connected together.                                     |     |     |       |

|            | If RESETIQ is not used to initialize the internal CLKIQ |     |     |       |

|            | divider to the correct phase, the system must be        |     |     |       |

|            | designed with enough skew between WRTIQ and             |     |     |       |

|            | CLKIQ (more than 1nS between rising edges) to           |     |     |       |

|            | guarantee successful transfer of data between these two |     |     |       |

|            | clock zones.                                            |     |     |       |

|            |                                                         |     |     |       |