## **Optimal Voltage Reference Design for SAR ADCs**

Luis Chioye – Precision Data Converters

# **SAR ADC Architecture**

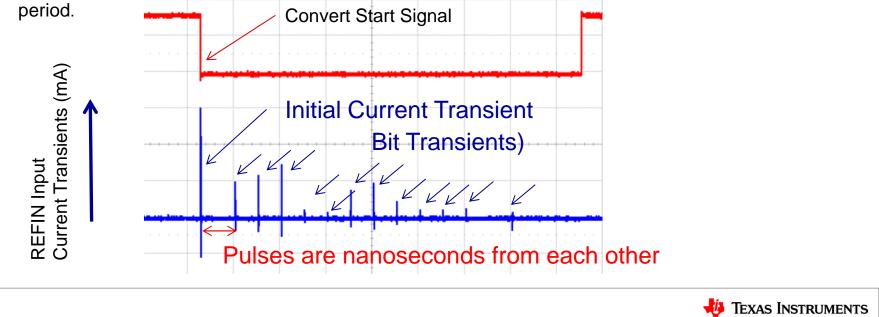

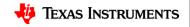

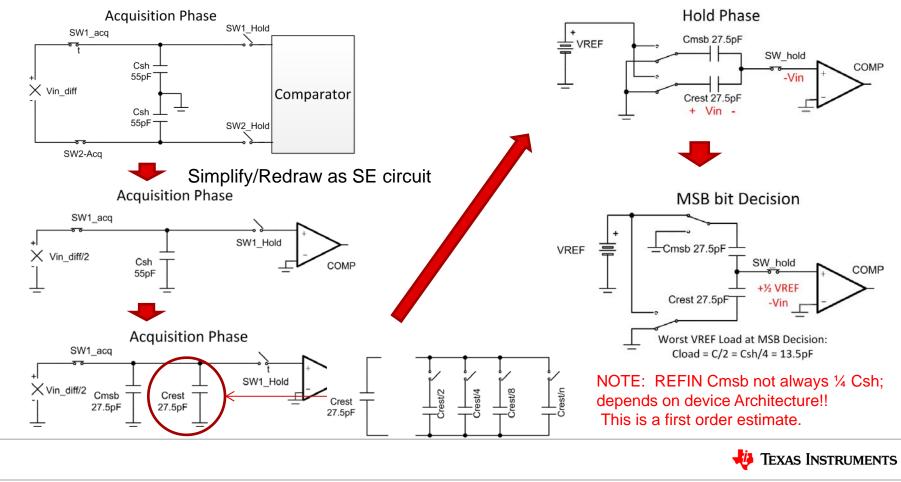

- The Reference is sampled several times during each conversion

- High-current transients (~10's mA range) are present in this REF input where the ADC's internal capacitor array is switched and charged as the bit decisions are made as binary weighted bit conversions are made.

- Current transient pulses occur only a few nanoseconds away of each other during the conversion

2

## **ADS8881 Reference Bypass capacitor**

- 10uF to 22µF range

- Ceramic X7R-grade, 0805-size, > 10-V rating

- Place right at the REFIN pin, use wide, low inductance connections

- Follow datasheet recommendations

ADS8881:18-Bit, 1-MSPS, SAR ADC:

| EXTERNAL REFERENCE INPUT |                                          |                                                    |     |     |    |  |  |  |

|--------------------------|------------------------------------------|----------------------------------------------------|-----|-----|----|--|--|--|

| V <sub>REF</sub>         | Input range                              | ADS8881C                                           | 3   | 5   |    |  |  |  |

|                          |                                          | ADS88811                                           | 2.5 | 5   | V  |  |  |  |

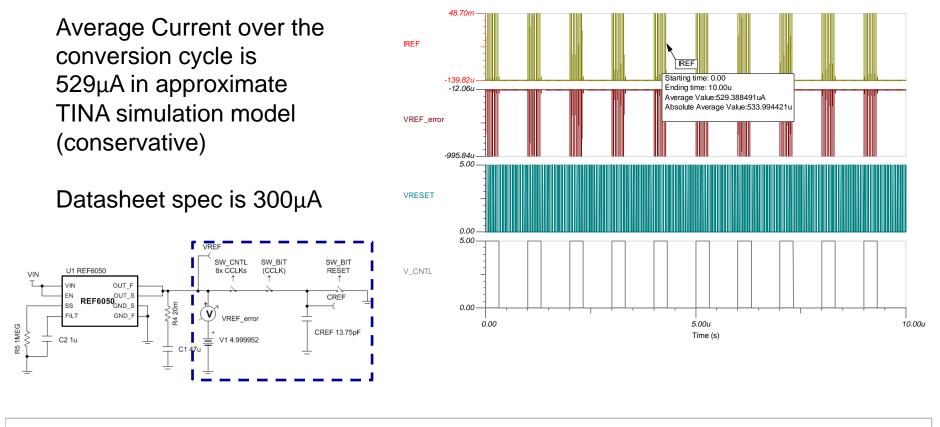

|                          | Reference input current                  | During conversion, 1-MHz sample rate, mid-<br>code |     | 300 | μA |  |  |  |

|                          | Reference leakage current                |                                                    |     | 250 | nA |  |  |  |

| C <sub>REF</sub>         | Decoupling capacitor at the<br>REF input |                                                    | 10  | 22  | μF |  |  |  |

|                          | Input leakage current                    | During acquisition for dc input                    |     | 5   | nA |  |  |  |

|                          | inpartiounago current                    | Saming acquisition for do input                    | K   |     | 10 |  |  |  |

High-performance (16-Bit) often require  $C_{REF} \ge 10 \mu F$

3

### **Reference Bypass capacitor**

- Why is the large reference bypass capacitor required?

- Works as large charge bucket

- Provides instantaneous charge at MSBs decisions

- Fast Transients are separated by CCLK period (10's ns)

- Reference droop must be less <  $\frac{1}{2}$  LSB between CCLKs

### **Reference Bypass capacitor**

- Why is the large reference bypass capacitor required?

- For example, ADS8881, 18-B, 1-MSPS, SAR ADC:

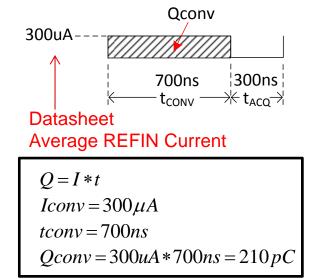

REFIN charge during each conversion

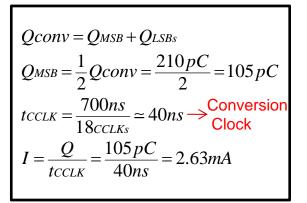

# Charge/current during MSB bit decision

## **Reference Bypass capacitor**

- Why is the large reference bypass capacitor required?

- For example, ADS8881, 18-B, 1-MSPS, SAR ADC:

For this approximate calculation, Assume most charge from bypass Capacitor and keep VREF voltage droop <1/4 LSB

$$Ic = C \frac{dV}{dt}$$

$$LSB = 38.14uV$$

$$dV = \frac{1}{4}LSB = 9.53uV$$

$$dt = t_{CCLK} = 40ns$$

$$Conversion$$

$$Clock$$

$$C = Ic \frac{dt}{dV} = 2.63mA \cdot \frac{40ns}{9.53uV} = \sim 11.04uF$$

Datasheet recommends 10uF - 22uF

6

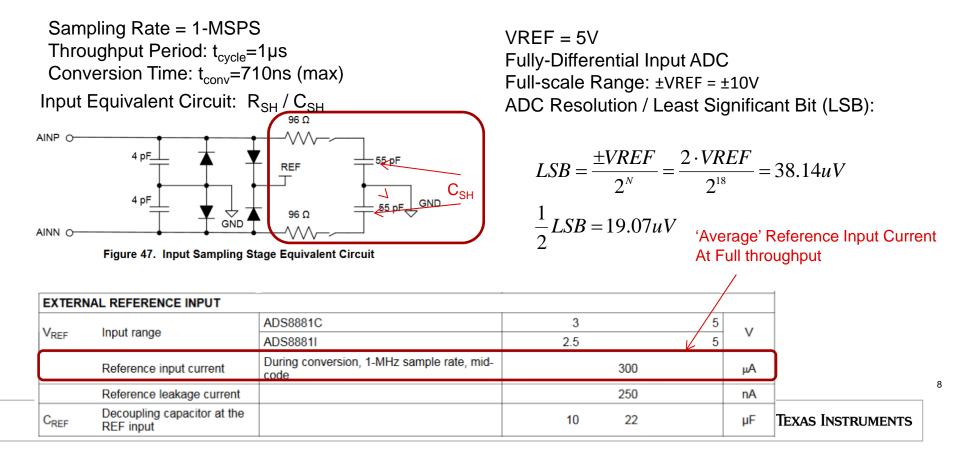

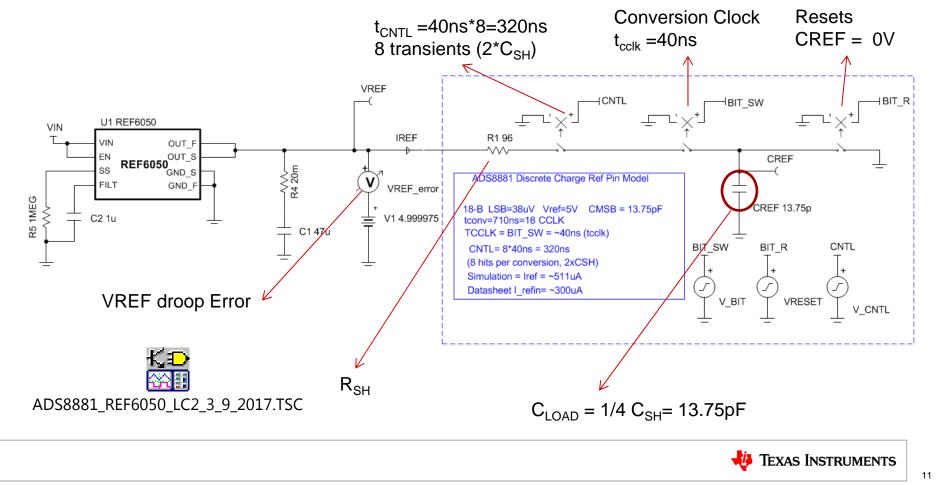

# ADS8881 Build TINA REF Input Model for a SAR

#### **Important Datasheet Parameters**

Example: ADS8881 18-B, 1-MSPS, Fully-Differential Input ADC

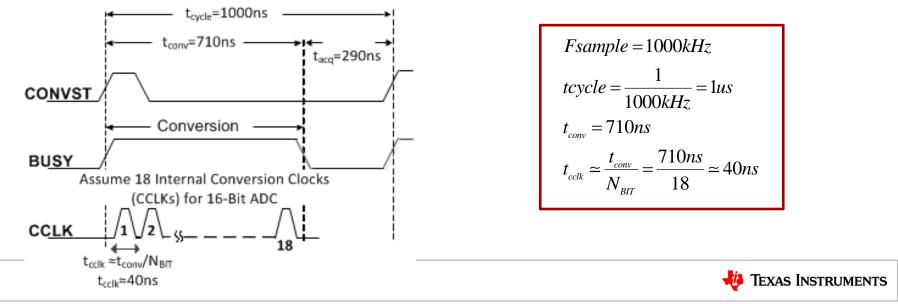

#### **Conversion Period and Conversion Clock Timing**

| ADS               | \$8881 uses an inter                               | K) Datasheet S | Datasheet Specifies t <sub>conv</sub> max |      |     |  |

|-------------------|----------------------------------------------------|----------------|-------------------------------------------|------|-----|--|

| SAMPLING DYNAMICS |                                                    |                |                                           |      |     |  |

| t <sub>conv</sub> | Conversion time                                    |                | 500                                       | 710  | ns  |  |

| t <sub>ACQ</sub>  | Acquisition time                                   |                | 290                                       |      | ns  |  |

|                   | Maximum throughput rate<br>with or without latency |                |                                           | 1000 | kHz |  |

#### Estimate internal Conversion Clock period

#### **TINA SPICE Equivalent Model**

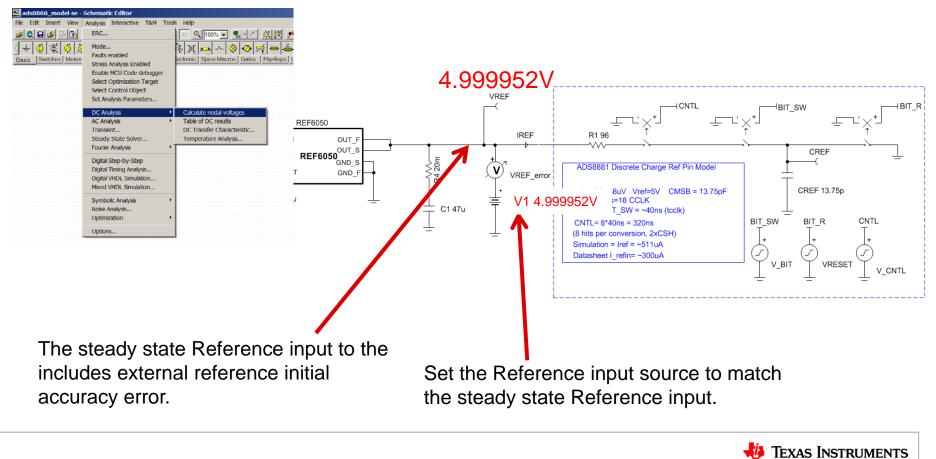

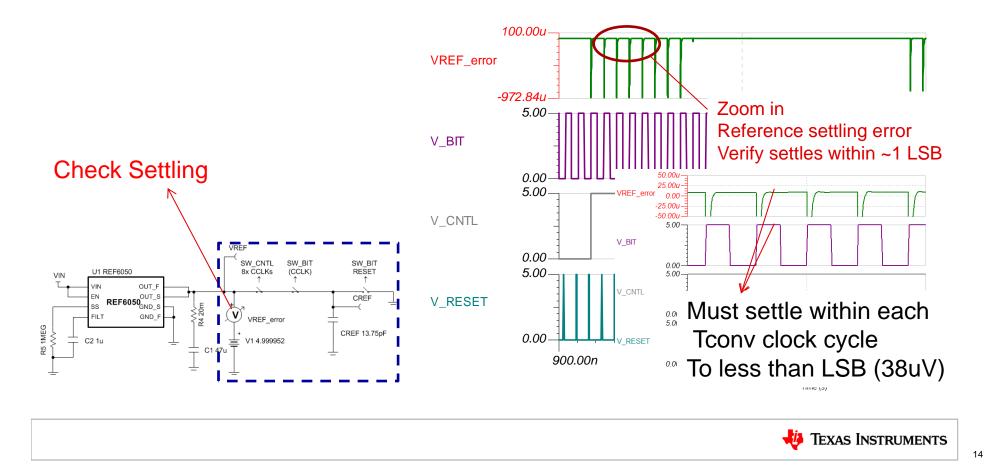

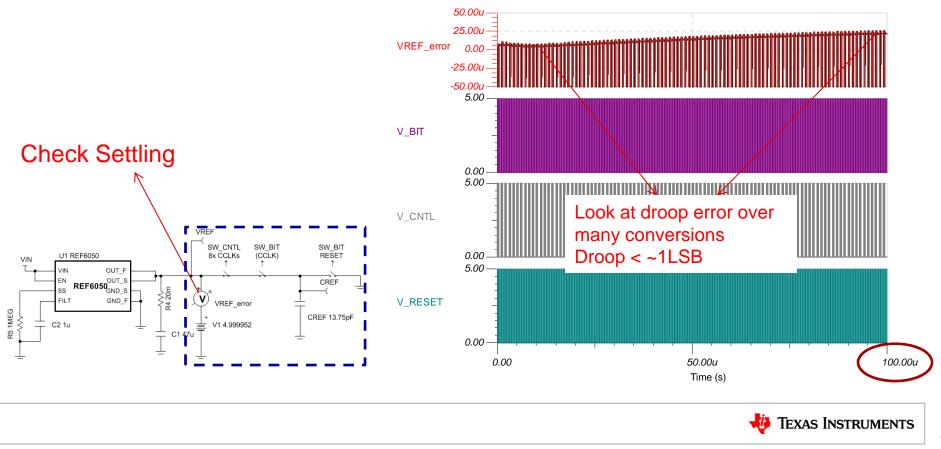

# **Steady state Simulation Results**

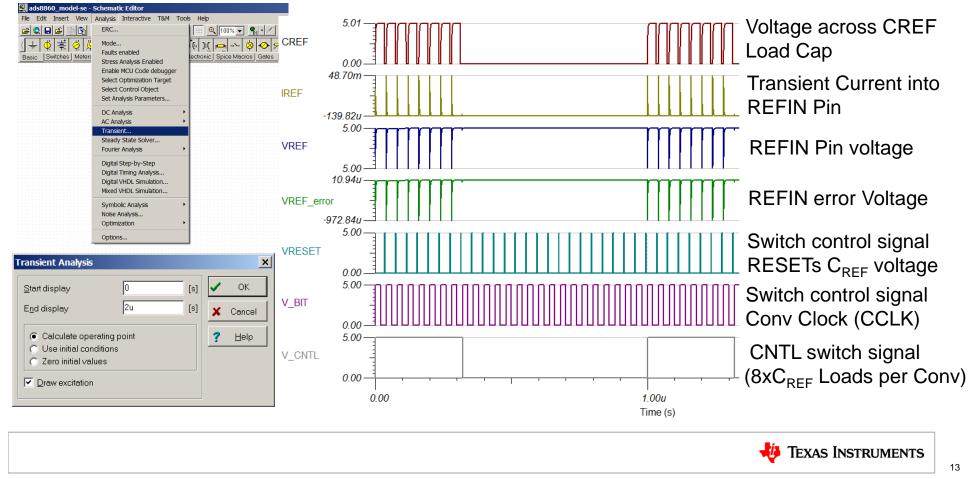

## **Example simulation: transient results**

## **Key Result: Error Signal**

## **Key Result: Error Signal**

# **Average Current in Simulation**