# **TPS65910Ax User's Guide For AM335x Processors**

**Version C**

# **User's Guide**

TEXAS INSTRUMENTS

Literature Number: SWCU093C August 2011–Revised May 2013

## WARNING: EXPORT NOTICE

Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorisation from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws. This provision shall survive termination or expiration of this Agreement.

According to our best knowledge of the state and end-use of this product or technology, and in compliance with the export control regulations of dual-use goods in force in the origin and exporting countries, this technology is classified as follows:

US ECCN: EAR99

EU ECCN: EAR99

And may require export or re-export license for shipping it in compliance with the applicable regulations of certain countries.

# Contents

| 1 | Introduc             | tion                                            | 5  |  |

|---|----------------------|-------------------------------------------------|----|--|

| 2 | Connect              | ion Diagram and TPS65910Ax EEPROM Definition    | 5  |  |

| 3 | First Initialization |                                                 |    |  |

|   | 3.1                  | I/O Polarity/Muxing Configuration               | 10 |  |

|   | 3.2                  | Define Wake-Up/Interrupt Event (SLEEP or OFF)   | 10 |  |

|   | 3.3                  | Backup Battery Configuration                    | 10 |  |

|   | 3.4                  | DCDC and Voltage Scaling Resource Configuration | 10 |  |

|   | 3.5                  | Sleep Platform Configuration                    | 10 |  |

| 4 | Event M              | anagement Through Interrupts                    | 11 |  |

|   | 4.1                  | INT_STS_REG.VMBHI_IT                            | 11 |  |

|   | 4.2                  | INT_STS_REG.PWRON_IT                            | 11 |  |

|   | 4.3                  | INT_STS_REG.PWRON_LP_IT                         |    |  |

|   | 4.4                  | INT_STS_REG.HOTDIE_IT                           | 11 |  |

|   | 4.5                  | INT_STS_REG.VMBDCH_IT                           | 11 |  |

|   | 4.6                  | INT_STS2_REG.GPIO_R/F_IT                        | 11 |  |

|   | 4.7                  | INT_STS_REG. RTC_ALARM_IT                       | 11 |  |

| 5 | Revisior             | History                                         | 12 |  |

## List of Figures

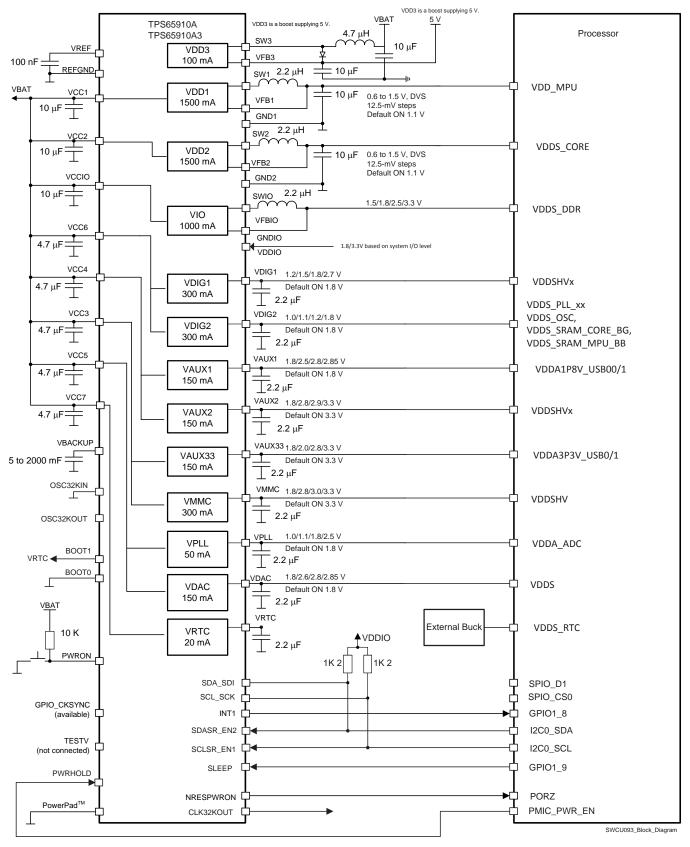

| 1 | AM335x Power Supply Connections with TPS65910A and TPS65910A3 | 6 |

|---|---------------------------------------------------------------|---|

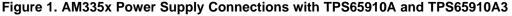

| 2 | AM335x Power Supply Connections with TPS65910A31              | 7 |

| 3 | Power-Up and Power-Down Timing Diagram                        | 9 |

## List of Tables

| 1 | TPS65910Ax comparison               | 5  |

|---|-------------------------------------|----|

| 2 | EEPROM Configuration for TPS65910Ax | 8  |

| 3 | Revision History                    | 12 |

## TPS65910Ax User's Guide For AM335x Processors

This user's guide can be used as a reference for connectivity between the TPS65910Ax powermanagement integrated circuit (PMIC) and the AM335x processor.

#### 1 Introduction

This user's guide can be used as a reference for connectivity between the TPS65910Ax PMIC and the AM335x processor. The TPS65910AA1 device is to support the AM335x processor with DDR2. TPS65910A3A1 and TPS65910A31A1 devices are to support the AM335x processor with DDR3. This user's guide does not provide details about the power resources or the functionality of the device. For such information, refer to the full specification document, *TPS65910 Data Manual*.

Table 1 compares TPS65910Ax devices

#### Table 1. TPS65910Ax comparison

|                                 | TPS65910A                                       | TPS65910A3                                      | TPS65910A31                                  |

|---------------------------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------------|

| Memory                          | DDR2<br>(VIO=1.8V)                              | DDR3<br>(VIO=1.5V)                              | DDR3<br>(VIO=1.5V)                           |

| VRTC power mode<br>in OFF state | Low power mode<br>(VRTC_REG.VRTC_OFFMASK<br>=0) | Low power mode<br>(VRTC_REG.VRTC_OFFMA<br>SK=0) | Full power mode<br>(VRTC_REG.VRTC_OFFMASK=1) |

#### 2 Connection Diagram and TPS65910Ax EEPROM Definition

Figure 1 shows the connection diagram between the processor and the TPS65910A or TPS65910A3. Figure 2 shows the connection diagram between the processor and TPS65910A31.

Notes for connection diagram:

- To support the processor power-up sequence, connect BOOT0 to ground and BOOT 1 to VRTC to select EEPROM boot mode.

- The TPS65910Ax digital control signal level is defined by the VDDIO connection.

- VAUX2 can support up to 300 mA for the specific case of a 3.3-V output level.

- The VDD1 and VDD2 connections shown in Figure 1 and Figure 2 is valid for processor version ZCZ (15 x 15). In ZCE (13 x 13), VDD\_MPU and VDD\_CORE are shorted internally. For ZCE, connect VDD1 to VDD\_MPU; VDD2 is free for system use.

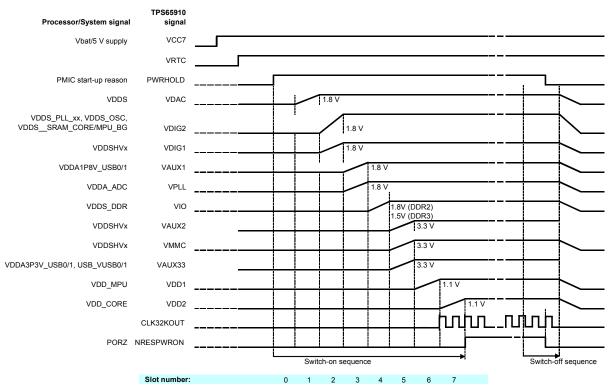

Table 2 lists the EEPROM definition of the TPS65910Ax and Figure 3 shows the corresponding power-up sequence.

| Register                     | Bit          | Description                                                                                                                | Option Selected                                                                                        |

|------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| VDD1_OP_REG                  | SEL          | VDD1 voltage level selection for boot                                                                                      | 1.1                                                                                                    |

| VDD1_REG                     | VGAIN_SEL    | VDD1 gain selection, x1 or x2                                                                                              | x1                                                                                                     |

| EEPROM                       |              | VDD1 time slot selection                                                                                                   | 6                                                                                                      |

| DCDCCTRL_REG                 | VDD1_PSKIP   | VDD1 pulse skip mode enable                                                                                                | Skip enabled                                                                                           |

| VDD2_OP_REG /<br>VDD2_SR_REG | SEL          | VDD2 voltage level selection for boot                                                                                      | 1.1                                                                                                    |

| VDD2_REG                     | VGAIN_SEL    | VDD2 gain selection, x1 or x3                                                                                              | x1                                                                                                     |

| EEPROM                       |              | VDD2 time slot selection                                                                                                   | 7                                                                                                      |

| DCDCCTRL_REG                 | VDD2_PSKIP   | VDD2 pulse skip mode enable                                                                                                | Skip enabled                                                                                           |

| VIO_REG                      | SEL          | VIO voltage selection                                                                                                      | TPS65910AA1 1.8V<br>(DDR2)<br>TPS65910A3A1 1.5V<br>(DDR3)<br>TPS65910A31A1 1.5V<br>(DDR3)              |

| EEPROM                       |              | VIO time slot selection                                                                                                    | 4                                                                                                      |

| DCDCCTRL_REG                 | VIO_PSKIP    | VIO pulse skip mode enable                                                                                                 | Skip enabled                                                                                           |

| EEPROM                       |              | VDD3 time slot                                                                                                             | OFF                                                                                                    |

| VDIG1_REG                    | SEL          | LDO voltage selection                                                                                                      | 1.8                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 2                                                                                                      |

| VDIG2_REG                    | SEL          | LDO voltage selection                                                                                                      | 1.8                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 2                                                                                                      |

| VDAC_REG                     | SEL          | LDO voltage selection                                                                                                      | 1.8                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 1                                                                                                      |

| VPLL_REG                     | SEL          | LDO voltage selection                                                                                                      | 1.8                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 3                                                                                                      |

| VAUX1_REG                    | SEL          | LDO voltage selection                                                                                                      | 1.8                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 3                                                                                                      |

| VMMC_REG                     | SEL          | LDO voltage selection                                                                                                      | 3.3                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 5                                                                                                      |

| VAUX33_REG                   | SEL          | LDO voltage selection                                                                                                      | 3.3                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 5                                                                                                      |

| VAUX2_REG                    | SEL          | LDO voltage selection                                                                                                      | 3.3                                                                                                    |

| EEPROM                       |              | LDO time slot                                                                                                              | 5                                                                                                      |

| CLK32KOUT pin                |              | CLK32KOUT time slot                                                                                                        | 7                                                                                                      |

| NRESPWRON pin                |              | NRESPWRON time slot                                                                                                        | 7 + 1                                                                                                  |

| VRTC_REG                     | VRTC_OFFMASK | 0 = VRTC LDO will be in low-power mode during<br>OFF state.<br>1 = VRC LDO will be in full-power mode during<br>OFF state. | TPS65910AA1 Low-<br>power mode<br>TPS65910A3A1 Low-<br>power mode<br>TPS65910A31A1 High-<br>power mode |

| DEVCTRL_REG                  | RTC_PWDN     | 0 = RTC in normal-power mode<br>1 = Clock gating of RTC register and logic, low-<br>power mode                             | 1                                                                                                      |

| DEVCTRL_REG                  | CK32K_CTRL   | 0 = Clock source is crystal/external clock.<br>1 = Clock source is internal RC oscillator.                                 | RC                                                                                                     |

| DEVCTRL2_REG                 | TSLOT_LENGTH | Boot sequence time slot duration:<br>0 = 0.5 ms<br>1 = 2 ms                                                                | 2 ms                                                                                                   |

#### Table 2. EEPROM Configuration for TPS65910Ax

| Register     | Bit            | Description                                                                                                                                   | Option Selected |

|--------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| DEVCTRL2_REG | IT_POL         | 0 = INT1 signal will be active low.<br>1 = INT1 signal will be active high.                                                                   | Active high     |

| INT_MSK_REG  | VMBHI_IT_MSK   | 0 = Device automatically switches on at NO<br>SUPPLY-to-OFF or BACKUP-to-OFF transition.<br>1 = Start-up reason is required before switch-on. | 1               |

| VMBCH_REG    | VMBCH_SEL[1:0] | Select threshold for main battery comparator threshold VMBCH.                                                                                 | 3 V             |

#### Table 2. EEPROM Configuration for TPS65910Ax (continued)

Figure 3. Power-Up and Power-Down Timing Diagram

#### 3 First Initialization

#### 3.1 I/O Polarity/Muxing Configuration

Program DEVCTRL2\_REG.SLEEPSIG\_POL according to the GPIO level setting on the processor. This can be set to active low or active high for SLEEP transitions. Software configuration allows specific power resources to enter a low consumption state.

Set DEVCTRL\_REG.DEV\_SLP = 1 to allow SLEEP transitions when requested.

Update the GPIO0 configuration (GPIO0\_REG) based on your needs.

#### 3.2 Define Wake-Up/Interrupt Event (SLEEP or OFF)

Select the appropriate bits in the INT\_MSK\_REG and INT\_MSK2\_REG registers to activate an interrupt to the processor on the INT1 line.

#### 3.3 Backup Battery Configuration

If a backup battery is used, enable backup battery charging by setting the BBCH\_REG.BBCHEN bit to 1. The maximum charge voltage can be set based on the backup battery specifications by using the BBSEL bits.

#### 3.4 DCDC and Voltage Scaling Resource Configuration

If the SmarReflex interface is not used for viltage scaling (power saving), these pins can be used to control the power resources.

Configure two operating voltages for DCDC1 and DCDC2

- VDDx\_OP\_REG.SEL= Roof voltage (ENx ball high)

- VDDx\_SR\_REG.SEL = Floor voltage (ENx ball low)

Assign control for DCDC1 to SCLSR\_EN1 and DCDC2 to SCLSR\_EN2:

- Set EN1\_SMPS\_ASS\_REG.VDD1\_EN1 = 1

- Set EN2\_SMPS\_ASS\_REG.VDD2\_EN1 = 2

- Set SLEEP\_KEEP\_RES\_ON\_REG.VDD1\_KEEPON = 1 (allow low-power mode)

- Set SLEEP\_KEEP\_RES\_ON\_REG.VDD2\_KEEPON = 1 (allow low-power mode)

#### 3.5 Sleep Platform Configuration

Configure the state of the LDOs when the SLEEP signal is used (by default all resources go into SLEEP state; in SLEEP state the LDO voltage is maintained but transient and load capability are reduced).

Resources that must provide full load capability must be set in the SLEEP\_KEEP\_LDO\_ON\_REG register.

Resources that can be set off in SLEEP state to optimize power consumption must be set in the SLEEP\_SET\_LDO\_OFF\_REG register.

#### 4 Event Management Through Interrupts

#### 4.1 INT\_STS\_REG.VMBHI\_IT

The INT\_STS\_REG.VMBHI\_IT bit indicates that the supply (VBAT) is connected (leaving the BACKUP or NO SUPPLY state), the system must be initialized. (See Section 3, *First Initialization*.)

#### 4.2 INT\_STS\_REG.PWRON\_IT

INT\_STS\_REG.PWRON\_IT is triggered when the PWRON button is pressed. If device is in the OFF or SLEEP state, this acts as a wake-up event and resources are reinitialized.

#### 4.3 INT\_STS\_REG.PWRON\_LP\_IT

INT\_STS\_REG.PWRON\_LP\_IT is the PWRON long-press interrupt. This interrupt is generated when the PWRON button is pressed for 6 seconds. The application processor can make a decision to acknowledge the interrupt. If this interrupt is not acknowledged in the next 2 seconds then the device interprets this as a power-down event.

#### 4.4 INT\_STS\_REG.HOTDIE\_IT

INT\_STS\_REG.HOTDIE\_IT indicates that the temperature of die is reaching the maximum limit. Software must take action to decrease the power consumption before automatic shutdown.

#### 4.5 INT\_STS\_REG.VMBDCH\_IT

INT\_STS\_REG.VMBDCH\_IT indicates that the input supply is low and the processor must prepare a shutdown to prevent losing data. This interrupt is linked to VBAT but does not apply to a system where the PMIC is connect to 5-V rails and not directly to VBAT.

#### 4.6 INT\_STS2\_REG.GPIO\_R/F\_IT

INT\_STS2\_REG.GPIO\_R/F\_IT is the GPIO interrupt event and can be used to wake up the device from SLEEP state. This can be an interrupt coming from any peripheral device or alike. This wake-up event is not valid for transitions from the OFF state.

#### 4.7 INT\_STS\_REG. RTC\_ALARM\_IT

INT\_STS\_REG. RTC\_ALARM\_IT is triggered when the RTC alarm set time is reached.

#### 5 Revision History

Table 3 lists the changes made since the previous version of this document.

#### Table 3. Revision History

| Section                                                   | Location | Additions/Modifications/Deletions                                                         |

|-----------------------------------------------------------|----------|-------------------------------------------------------------------------------------------|

| Connection Diagram and<br>TPS65910Ax EEPROM<br>Definition | Figure 1 | Update Figure 1: Replace Default OFF with<br>DEFAULT ON in VDIG1, VDIG2, VAUX1,<br>VAUX33 |

| Connection Diagram and<br>TPS65910Ax EEPROM<br>Definition | Figure 2 | Update Figure 2: Replace Default OFF with<br>DEFAULT ON in VDIG1, VDIG2, VAUX1,<br>VAUX33 |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated