| <u>Date</u> <u>Rev</u>       | <u>By</u> | <u>History</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

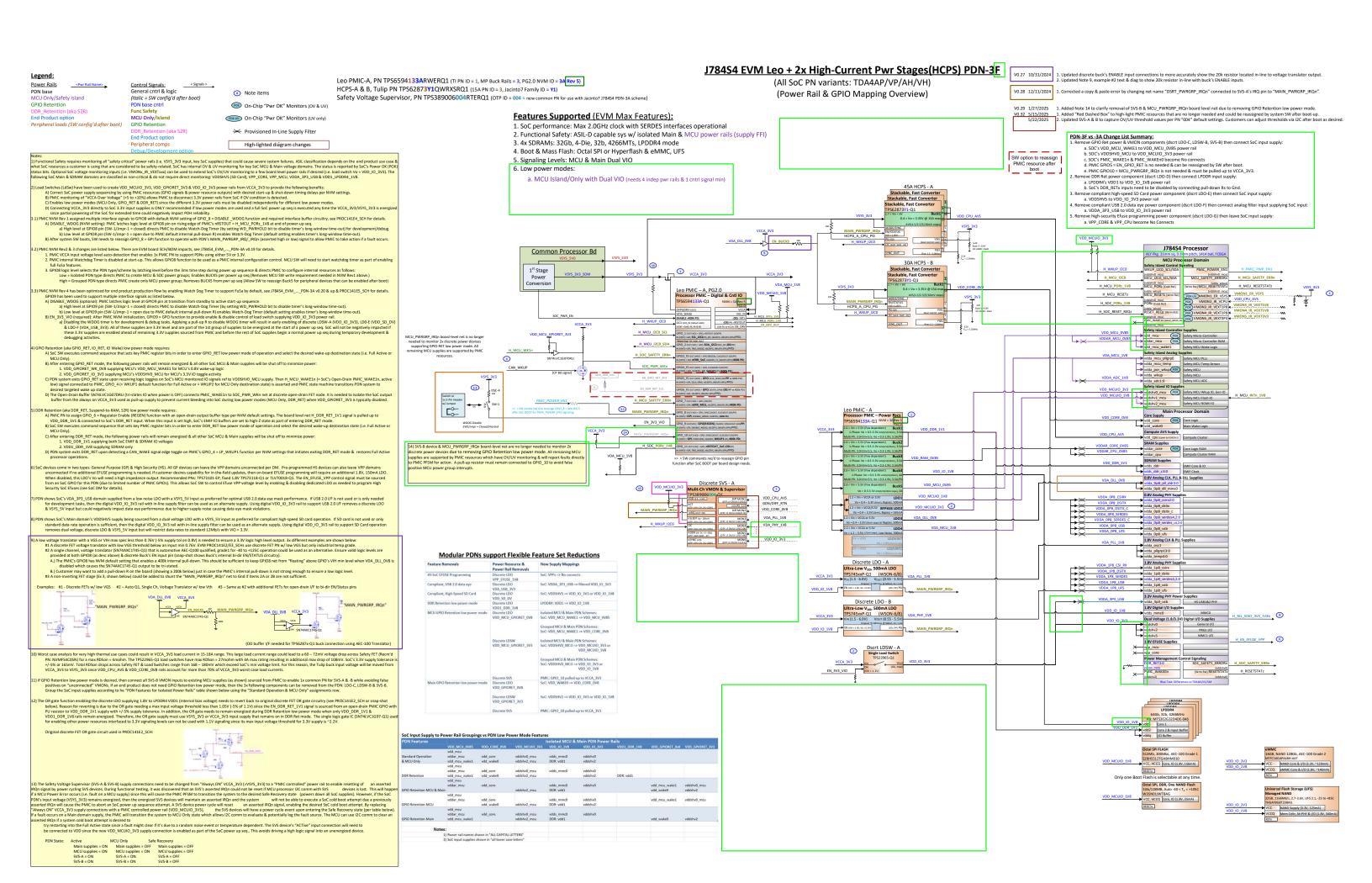

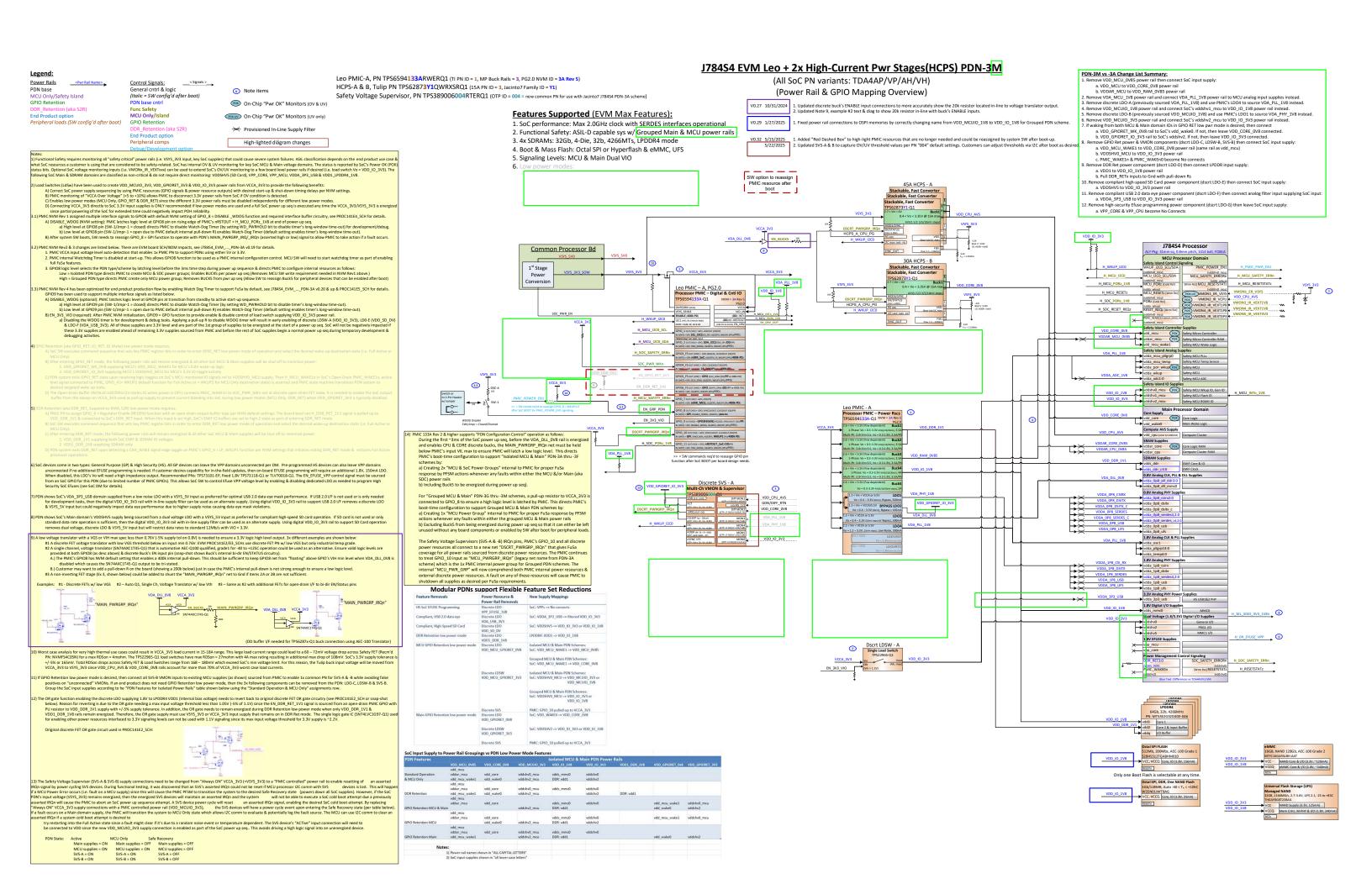

| V0.29 2/7/2025               | ВМс       | PDN-3G & -3M Diags only  1. Fixed power rail connections to OSPI memories by correctly changing name from VDD_MCUIO_1V8 to VDD_IO_1V8 for Grouped PDN scheme.  PDN-3F Diag only  2. Added Note 14 to clarify removal of SVS-B & MCU_PWRGRP_IRQn board level net due to removing GPIO Retention low power mode.  SoC Pwr Seqs:  1. Corrected power up seq timing diagram to correctly show time btw pwr up seq Time Step #2 vs #3 as only 0.5ms (instead of 1.0ms) per PMIC 133A's v4 update & as captured in v0.23 changes above. |

| v0.30 2/19/2025              | ВМс       | Soc Pwr Seqs:  1. Corrected diag to show SOC_PWR_EN (PMIC_ENABLE input) signal asserting low 0.1ms (PMIC's internal delay T <sub>DLYO</sub> ) before PMIC's state machine begins executing power down seq by 1 <sup>st</sup> setting MCU_PORz & SOC_PORz low.                                                                                                                                                                                                                                                                     |

| v0.31 3/21/2025              | ВМс       | SoC Pwr Seqs:  1. Corrected diag to show both VDD_GPIORET_IO_3V3 & VDD_IO_3V3 min enable time could be ~0.1ms after enabling signals (VDD_MCUIO_3V3 & EN_3V3_IO respectfully).  2. An "Immediate Shutdown/Power Down Seq" has recently been approved and will be add to an upcoming data manual version. This simplifies SoC power down to only require both PORz signals to be set low for 1-2us before disabling SoC input supplies in any order.                                                                               |

| V0.32 5/15/2025<br>5/22/2025 | ВМс       | PDN-3AFGM Diags  1. Added "Red Dashed Box" to high-light PMIC resources that are no longer needed and could be reassigned by system SW after boot-up.  2. Updated SVS-A & B to capture OV/UV threshold values per PN "004" default settings. Customers can adjust thresholds via I2C after boot as desired.                                                                                                                                                                                                                       |

### TPS6594133A NVM | Revision History

| Revision | Release Date                  | Comments                                                                 |

|----------|-------------------------------|--------------------------------------------------------------------------|

| 0.0      | April 25, 2022                |                                                                          |

| 1.0      | August 8, 2022                |                                                                          |

| 2.0      | October 10, 2022              | TI J784S4 EVM Samples                                                    |

| 3.0      | December 15, 2022             | RTM'd in January 2023                                                    |

| 4.0      | Only released in sample units |                                                                          |

| 5.0      | March 1, 2024                 | PCN released and all parts received after March 1st , 2024 contain Rev 5 |

| Rev | Change                                                                                                                                                                                                                                                                                                                                                                                                           | Impact of Change                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | GPIO Retention Entry/Exit Handling – If Wake signal triggers while being armed, PMIC will enter Retention and then immediately exit.                                                                                                                                                                                                                                                                             | Prevents PMIC from getting stuck in Retention                                                                                                                                                                                                                                                                                                                                                     |

| 1.0 | Power Down Sequence Timing Changes -Updated power down seq of VDA, DLL, DV8 to shift disabling from 2.5ms to 1.0ms due to -1ms delay in VDA, DLL, DV8 RC discharge before VDD, CPU, AVS & VDD_CORE, DV8 are disabled by VDA, DLL_0V8 dropping below 0.6V FET Yon thresholdUpdated power down seq of VDD, DCU, DV8 to shift disabling from 2.5ms to 2.0ms to -align with disabling of VDD_CPU_AVS & VDD_CORE_0V8. | Overall sequence time remains the same.<br>Better power down seq when using<br>discrete component rails to align with J7<br>SoC DM recommended seq.                                                                                                                                                                                                                                               |

| 1.0 | At startup, all PMIC power resources/rails mapped to a single MCU_PWR_ERR group                                                                                                                                                                                                                                                                                                                                  | Enables 1x PMIC PN to support both<br>Grouped & Isolated PDN board designs<br>Grouped MCU & Main PDNs (33 to<br>3M) need 1x PMIC power group to<br>enable fault on any monitored rail to<br>cause an orderly shutdown.  Isolated MCU & Main PDNs (34 to 3F)<br>will need MCU SW to create 2x power<br>groups (MCU & Main) by writing 0x1E 32<br>to PMIC register 0x44       To PMIC register 0x44 |

| Rev | Change                                                                                                                                                                                                                                             | Impact of Change                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | VCCA input voltage level auto-detection                                                                                                                                                                                                            | Enables 1x PMIC PN to support PDNs with VCCA voltage of 5V or 3.3V                                                                                                                                                                                                                                                                                                                                                  |

|     | Watchdog Timer disabled                                                                                                                                                                                                                            | GPIO8 used for PMIC config control     MCU SW will need to start     watchdog timer as part of enabling full FuSa features                                                                                                                                                                                                                                                                                          |

| 2.0 | GPIO8 logic level latched before 3ms time step of power up sequence & directs PMIC to configure internal resources:  Low = Creates 2x power groups; Enables BUCK5 per power up seq  High = Creates 1x power group; Removes BUCK5 from power up seq | Isolated MCU & Main PDNs (3A to 3F) need 2x power groups, use Buck5 for VDD MCU, V985 rail & connect MAIN PWRGRF IROn to GPI08 for discrete power resource monitoring.     Grouped MCU & Main PDNs (3G to 3M) need 1x power group, removes Buck5 from pwr up seq (Buck5 can be reassigned by SW conflig to supply a peripheral rail after Sec & SW bootup) & connects GPI08 to pull-up resistor to, set logic high. |

| Rev | Change                                                  | Impact of Change                                                                            |

|-----|---------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 2.0 | Removed any2ota sequence                                | PMIC OTA preparation sequence is no<br>longer available. Unused during normal<br>operation. |

| 2.0 | Fixed GPIO10 response during normal operation           | Prevents PMIC from getting stuck after<br>MCU_PWRGRP_IRQn triggers a<br>recovery attempt    |

| 3.0 | Adjusted internal setting for improved BUCK reliability | No impact to function                                                                       |

| Rev | Change                                                  | Impact of Change                                                                            |

|     | Watchdog enabled by default with 1 sec long window      | MCU SW must boot and configure watchdog within 1 second of nRSTOUT going high               |

|     |                                                         |                                                                                             |

| Rev | Change                                                    | Impact of Change                                                                                                                                                                                       |

|-----|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Watchdog enabled by default with 1 sec long window        | MCU SW must boot and configure watchdog within 1 second of nRSTOUT going high                                                                                                                          |

| 4.0 | Change default GPIO9 function from GPIO to WD_DISABLE     | GPIO9 starts as an input to set WD_PWRHOLD bit, then changes to an output. In Development: Customer has option to use external PU resistor to set WD_PWRHOLD = In End Equipment: No impact to function |

|     | TO_ACTIVE sequence has 500us delay between LDO3 and BUCK5 | In systems with split power groups, PMIC BUCK5 powers up fully before PMIC LDO3. Overall sequence time remains the same.                                                                               |

|     | LDO2 OV/UV Threshold changed from 5% to 10%               | When used as 3.3V load switch, PG Window will match that of VCCA. Customer can tighten after boot.                                                                                                     |

\*Error found EN\_I2C\_CRC sequence, only on Rev4

| Rev 4 I2C_CRC_EN Error and Workaround                          |    |

|----------------------------------------------------------------|----|

| What: Setting I2C 2 ESM Trigger high to enable the I2C CRC doe | 20 |

- What: Setting I2C\_2 FSM Trigger high to enable the I2C CRC does not work of Rev 4 of TPS6594133A

- Why: Implementation of changes for watchdog and GPIO9 for disable watchdog pushed NVM over the memory limit

- Affected Revisions: Only Rev 4 is impacted. This was fixed in Rev 5

- Software Workaround: Instead of using the I2C\_2 FSM trigger, please use SW workaround described on next page

# Change Impact of Change Watchdog Long Window set to 13 minutes. MCU SW must boot and configure watchdog within 13 minutes of first TOUT going high Fixed EN\_IZC\_CRC sequence error MCU can use IZC\_2 FSM Trigger to enable IZC CRC

\* Texas Instruments

#### **NVM Rev 4 Summary of Changes**

| Item | Change                                                     | Impact                                                                                                                                                                                                                                       |

|------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Watchdog enabled by default with 1 sec long window         | MCU SW must boot and configure watchdog within 1 sec of nRSTOUT (SoC's MCU_PORz) going high                                                                                                                                                  |

| 2    | Change GPIO9's default NVM function from GPI to WD_DISABLE | GPIO9 starts as an input to set WD_PWRHOLD bit, then changes to an output.  In Development/Debug; Customer has option to use external PU resistor to disable WD Timer by setting WD_PWRHOLD =1 In End Equipment: WD Timer enabled by default |

| 3    | TO_ACTIVE sequence adds 500us delay to LDO3 enable         | Adds timing margin to ensure BUCK5 (SoC's VDD_MCU_0V85) powers up fully before Tulip buck (SoC's VDD_CORE_0V8) that is enabled by LDO3                                                                                                       |

| 4    | LDO2 output OV/UV Threshold changed from 5% to 10%         | When used as 3.3V load switch, PG Window will match that of VCCA since both are supplied by VSYS_3V3 input voltage from pre-regulator. Customer can tighten after boot.                                                                      |

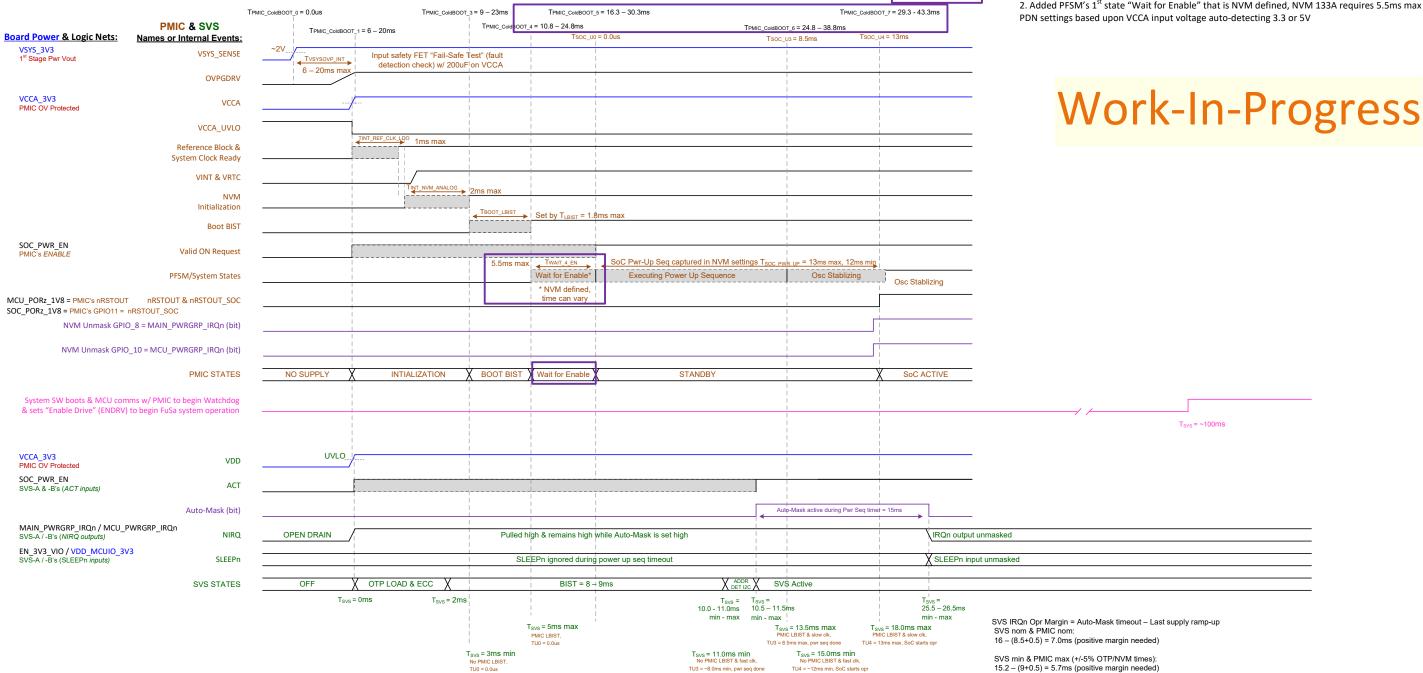

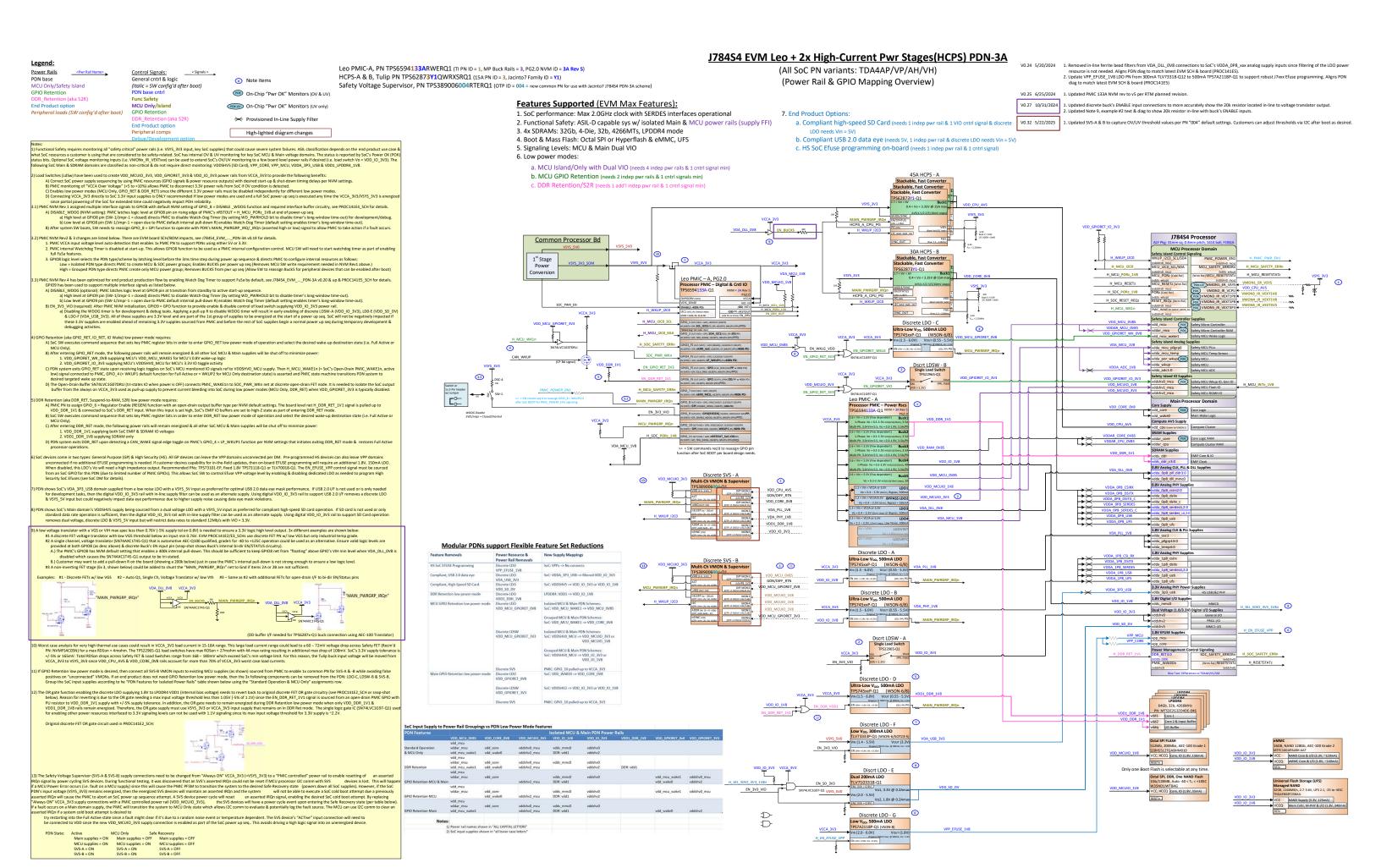

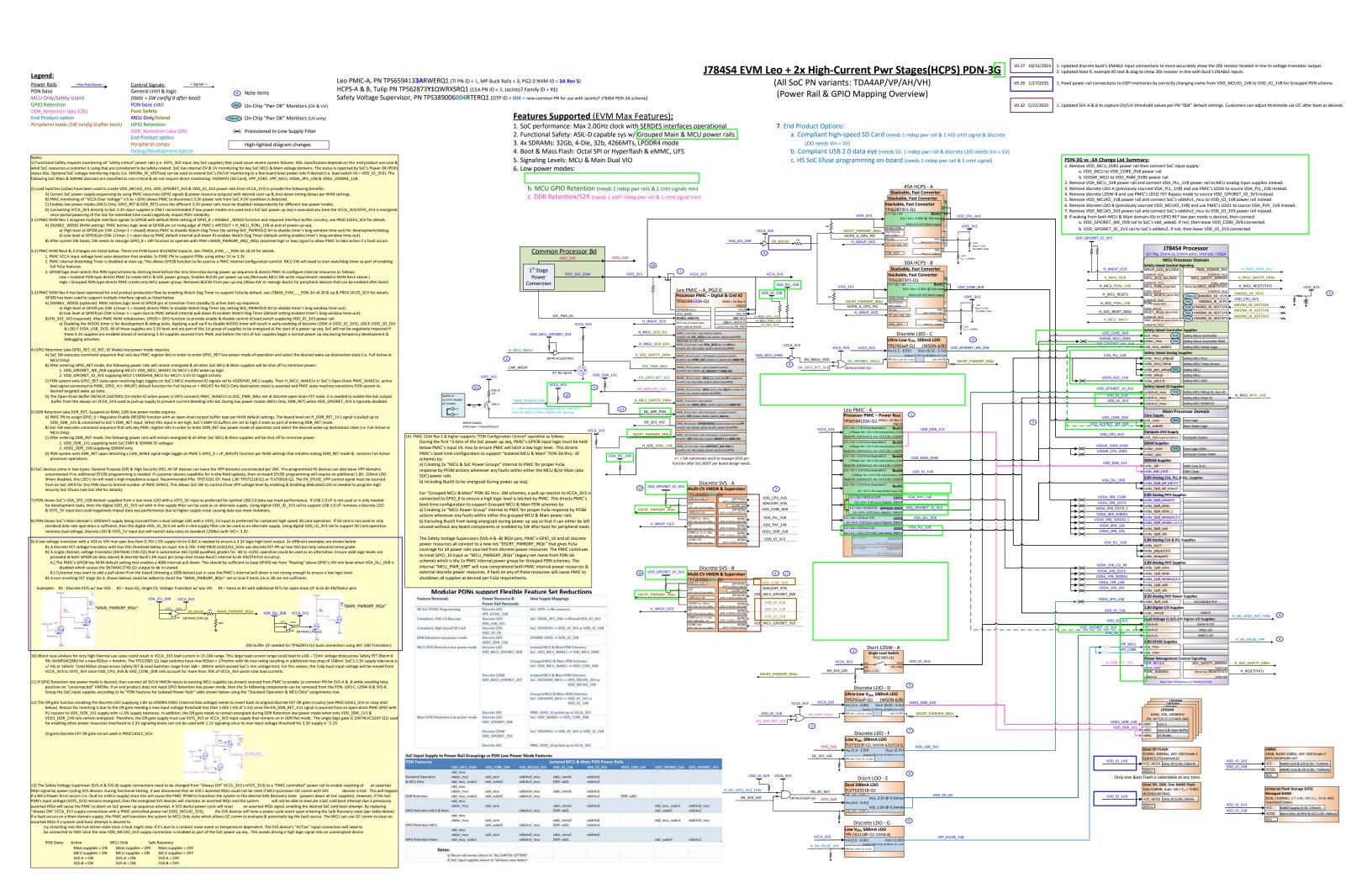

## J784S4 EVM Leo + 2x High-Current Pwr Stages(HCPS) PDN-3A

Leo PMIC-A, PN TPS6594133ARWERQ1 (TI PN ID = 1, MP Buck Rails = 3, PG2.0 NVM ID = 3A Rev 4 or higher)

Legend:

Device Timing Parameters

Board Power Rail – Active State / Control Signal Nets / SoC voltage domains

Board Power Rail – GPIO Retention / Control Signal Nets / SoC voltage domains

Rail - DDR Retention / Control Signal Nets / SoC voltage domain

ower component

NVM Settings: (Pwr Rsrc, Current Capacity, Boot Voltage, Delay After Enable [us], Slew Rate [mV/us])

(GPIO# = Function, Ref Voltage, Output Buffer Type, Logic @ T=0, Logic @ Elapsed time [us],

\$ Indicates PMIC Control Signal & Power Resource and Board Power Rail counts that transition during power sequences

HCPS-A & B, Tulip PN TPS62873Y1QWRXSRQ1 (15A PN ID = 3, Jacinto7 Family ID = Y1) Safety Voltage Supervisor, PN TPS389006004RTERQ1 (OTP ID = 004 = new common PN for use with Jacinto7

V0.23c 12/06/2023 BMc 3. Added new power up seg constraints list for quick reference as needed to align with Errata i2406 "IO Glitches during Pwr Up Segs"

Rev Date

V0.23 10/26/2023 BMc 1. Increase time btw pwr up seq Time Step #2 vs #3 to add 0.5ms margin btw VDD MCU 0V85 vs VDD CORE\_0V8 for worst case per SoC errata i2406

BMc 2. Updated PMIC PN NVM revision from v2 to v4

v0.29 2/07/2025 BMc 1. Corrected power up seq timing diagram to correctly show time btw pwr up seq Time Step #2 vs #3 as only 0.5ms (instead of 1.0ms). | V0.30 2/19/2025 | BMc | 1. Corrected diag to show SOC\_PWR\_EN (PMIC\_ENABLE input) signal asserting low 0.1ms (PMIC's internal delay T<sub>DLYO</sub>) before PMIC's state machine begins executing power down seq by 1<sup>st</sup> setting MCU\_POR2 & SOC\_POR2 low. | V0.31 3/21/2025 | BMc | 1. Corrected diag to show both DDD\_GPIORET\_IO\_3V3 & VDD\_IO\_3V3 min enable time could be "0.1ms after enabling signals" | V0.30 |

(VDD\_MCUIO\_3V3 & EN\_3V3\_IO respectfully).

2. An "Immediate Shutdown/Power Down Seq" has recently been approved and will be add to an upcoming data manual version. This simplifies SoC power down to only require both PORz signals to be set low for 1-2us before disabling SoC input supplies in any order

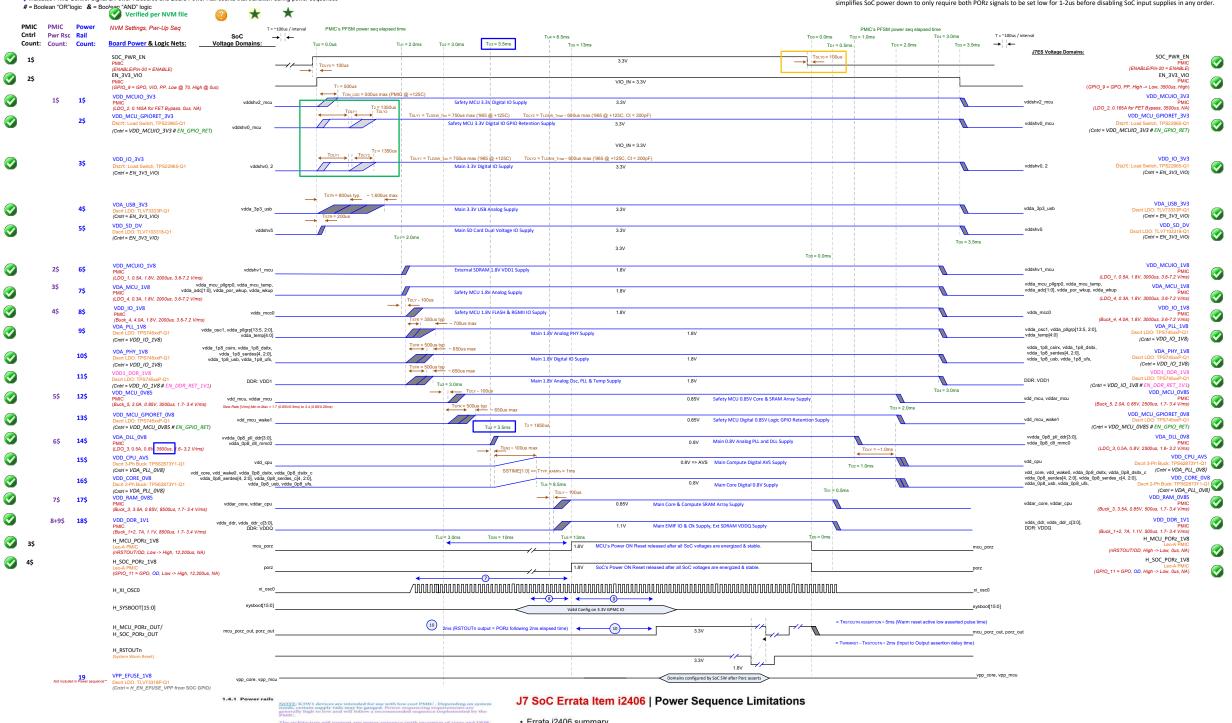

During active power ramp, the core supply must always lead the corresponding array supply during ramp-up and must lag the corresponding array supply durin ramp-down such that VDD\* (core) >= VDDAR\* (array).

To meet lifetime reliability specs, during any other uncontrolled ramp down, ensure that the array supply (VDDA\*) is not actively driven when the corresponding core (VDD\*) is  $\sim$ 200mV.

During active power ramp-up, the core supply must ramp to valid level before beginning DDR IO supply ramp (L.IV / 0.6V).

During active power ramp-down, the DDR IO supplies (1.1V/0.6V) must ramp down below DDR logic VII. levels before the core supply begins to ramp down below ralid level.

DDR IO supplies (17es\_arch\_gap.64);

- In order to prevent random IO signal pulses & potential IO drive contention during the

#### New power-up seg constraints

- VDD\_CORE must ramp-up before or from same power resource supplying VDD\_WAKE0. VDD MCU must ramp-up before or from same power resource supplying VDD MCU WAKE1.

- \( \text{VDD\_MCU should ramped-up based upon the Vnom level and power resource as follows: \)

a) \( \text{Vnom} = 0.8V \text{ s ame 0.8V power resource supplying all 0.8V core level supplies (VDD\_CORE, VDD\_WAKE0 \text{ k VDD\_MCU WAKE1} should ramp VDD\_MCU simultaneously with all 0.8V core level supplies.

b) \( \text{Vnom} = 0.85V \text{ s independent 0.85V power resource should ramp VDD\_MCU 0.5ms before all 0.8V core level supplies.} \)

- supplies.

VDDAR\_CPU or VDDAR\_CORE supplies cannot be grouped with 0.85V VDD\_MCU since they must ramp-up after VDD\_CORE & VDD\_CPU supplies.

VDDAR\_MCU & VDD\_MCU\_WAKE1 supply can be grouped with 0.85V VDD\_MCU power resource.

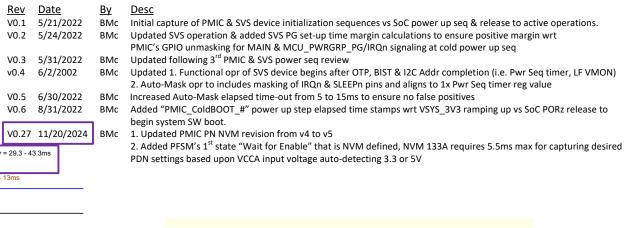

## TPS6594133A PMIC + TPS389006004 SVS Cold Boot-up Timing for PDN-3x

Leo PMIC-A, PN TPS6594133ARWERQ1 (TI PN ID = 1, MP Buck Rails = 2, PG2.0 NVM ID = 3A Rev 5)

HCPS-A & B, Tulip PN TPS62873Y1QWRXSRQ1 (15A PN ID = 3, Jacinto7 Family ID = Y1)

Safety Voltage Supervisor, PN TPS389006004RTERQ1 (OTP ID = 004 = new common PN for use with J7 PDN-3x scheme)