## PRU-ICSS EtherNet/IP Adapter Firmware Data Sheet

### FEATURES

- EtherNet/IP Adapter is compliant to Conformance Tool 13 from ODVA

- Declaration of Conformity [DOC] from ODVA with interoperability stamp\*.

- Min RPI of 1ms

- Integrated two-port cut-through switch

- 100 Mbps, 10Mbps

- Full Duplex, Half Duplex

- Quality of Service (QoS)

- Four priority receive queues on host port, each queue 6 KB in size

- Four priority transmit queues on each physical port, each queue 3 KB in size

- Total CIP Connections - 9

- IO Messaging – 6

- Explicit Messaging - 3

- DLR – Device Level Ring

- 100us beacon interval

- 200us beacon timeout

- Self-Configuring

- ACD support

- PTP/1588 – Time Synchronization

- E2E mode supported

- CIP Sync capable

- Transparent and Ordinary Clock

- 1 ms buffering per port

- 802.1d learning bridge for received source MAC addresses

- 1024 addresses per port

- API's for port state configuration and flushing learning table upon change in network topology

- Switch address learned table (FDB) is flushed in 2.4 us

- Multicast and Broadcast storm prevention per port

- API's to store configuration parameters in non-volatile memory

- Interrupt for Link loss detection.

- Link loss detection in under 200us

- Callback API's to perform tasks related to change in network topology

**NOTE:** \* Interoperability stamp implies that the device has passed an EtherNet/IP plugfest within 6 months of DOC

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## Description

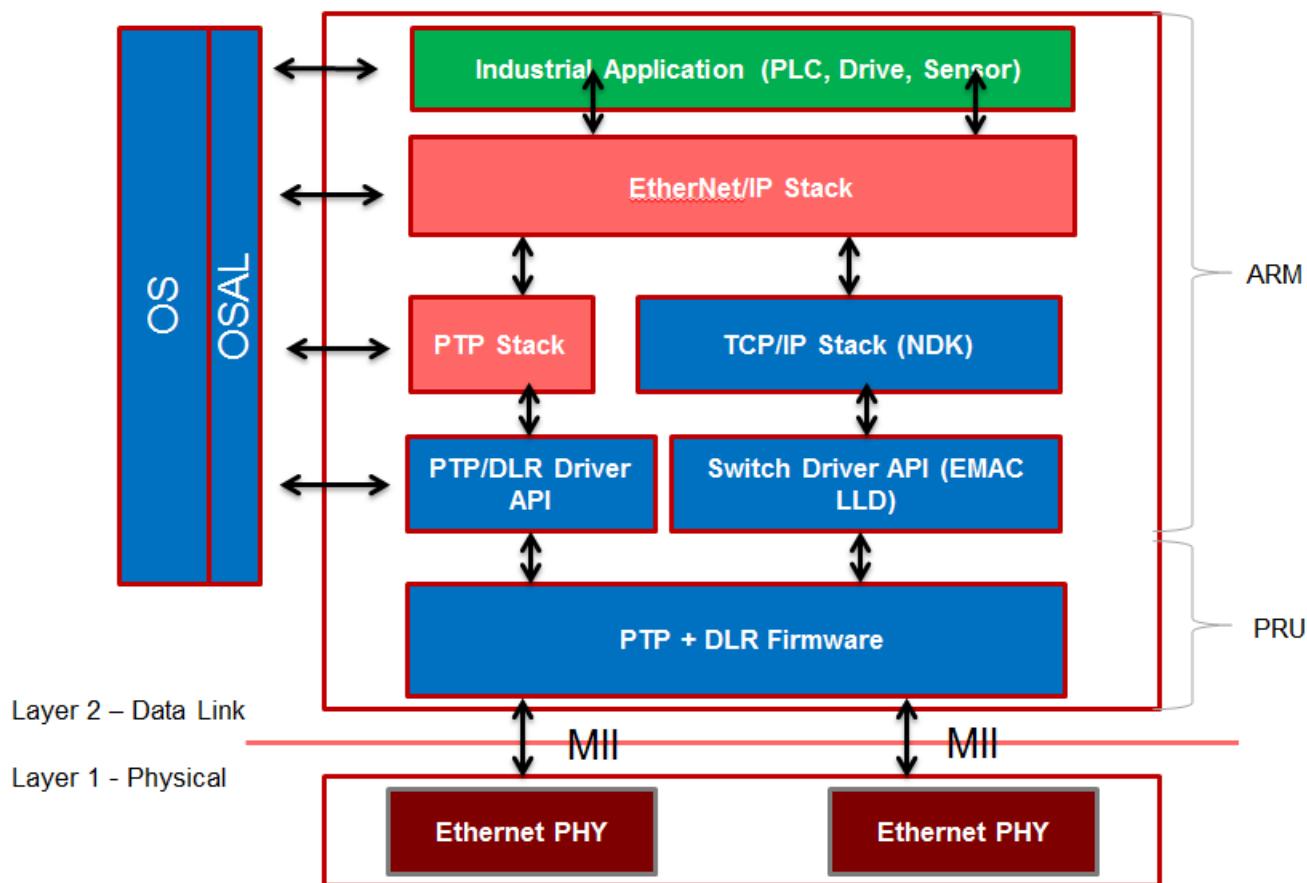

PRU-ICSS EtherNet/IP firmware implements EtherNet/IP + PTP + DLR functionality and provides EtherNet/IP ASIC like functionality integrated into AM335x, AM437x and AM57x class of devices. PRU-ICSS EtherNet/IP software from TI can be used by customers to add EtherNet/IP function on top of Processor SDK to Sitara processors.

When referring to EtherNet/IP we refer to the layer on top of TCP/IP layer. This can be implemented on the standard switch firmware and does not require any special driver support. The additional features in firmware and driver are PTP and DLR. When referring to the EtherNet/IP driver we refer to the standard switch driver and PTP and DLR driver layers.

EtherNet/IP firmware for PRU-ICSS is a black box product maintained by TI. EtherNet/IP driver allows loading and running EtherNet/IP firmware and interface with the firmware.

EtherNet/IP Driver is provided in full source so that customers can adapt this implementation to own hardware and Operating Systems. This driver provides stack interface for queue management, Rx, Tx, PTP Configuration, DLR management, interfacing PTP and EIP stack.

Operating System, Switch Driver (ICSS EMAC LLD), TCP/IP Stack (NDK) and associated documentation is available through Processor SDK. See Software section for details

## Performance Summary

A 300 MHz CPU speed is sufficient to support a simple IO or sensor application. More complex applications can use higher speed grades of up to 1.5 GHz. The PRU core speed remains 200 MHz for all speed grades.

## Memory Summary

This section describes memory usage of the EtherNet/IP PRU-ICSS firmware and Cortex-A driver.

**Table 1 EtherNet/IP PRU-ICSS Firmware Memory Statistics**

| Memory      | Program memory (AM3 Family) | Program memory (AM5 Family) | Data memory | Remarks                     |

|-------------|-----------------------------|-----------------------------|-------------|-----------------------------|

| L3 OCMC RAM | NA                          | NA                          | 54272 bytes | Receive and Transmit Queues |

**NOTE: Driver object files () used for this analysis with

gcc-arm-none-eabi-4\_8-2014q3 toolchain options : -mcpu=cortex-a8 -mtune=cortex-a8 -marm -mfloating-abi=hard -mfpu=neon -O2**

## Hardware Requirements

- Sitara Processor with PRU-ICSS IP and EtherNet/IP support

- EtherNet/IP implementation uses following interrupts mapped to Host Interrupt Controller

| Stack/application interrupts            |                  |                                                                         |

|-----------------------------------------|------------------|-------------------------------------------------------------------------|

| Firmware interrupt                      | Host Interrupt   | Remarks                                                                 |

| Frame Receive                           | PRU_ICSS_EVTOUT0 | Notifies host when firmware has stored a frame in host receive queue    |

| DLR Port 0 Interrupt                    | PRU_ICSS_EVTOUT1 | Raised when there is a state change in DLR on Port 0                    |

| DLR Port 1 Interrupt                    | PRU_ICSS_EVTOUT2 | Raised when there is a state change in DLR on Port 1                    |

| Tx Callback Interrupt                   | PRU_ICSS_EVTOUT3 | Raised when a PTP/1588 frame which requires Tx Timestamping is sent out |

| DLR Beacon Timeout Interrupt for Port 0 | PRU_ICSS_EVTOUT4 | Raised when the beacon timeout timer on Port 0 expires                  |

| DLR Beacon Timeout Interrupt for Port 1 | PRU_ICSS_EVTOUT7 | Raised when the beacon timeout timer on Port 1 expires                  |

| Link 0                                  | PRU_ICSS_EVTOUT6 | Interrupt is raised when the Link on MII0 port comes up or goes down    |

| Link 1                                  | PRU_ICSS_EVTOUT6 | Interrupt is raised when the Link on MII1 port comes up or goes down    |

- EtherNet/IP implementation makes use of one channel of EDMA for PTP implementation

- HW signals required to implement EtherNet/IP adapter functionality is shown below, this info needs to be used in conjunction with <http://www.ti.com/tool/PINMUXTOOL>

**NOTE: w.r.t prX, X is 1 or 2 (respectively PRU-ICSS1 and PRU-ICSS2 – refer to SOC TRM for availability)**

**Table 2 PRU-ICSS signals required for EtherNet/IP functionality**

| Signal name                                                     | Description                                     |                                                                                                       |

|-----------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| <b>PRU-ICSS MDIO</b>                                            |                                                 |                                                                                                       |

| prX_mdio_mdclk                                                  | Mandatory                                       | MDIO clock                                                                                            |

| prX_mdio_data                                                   | Mandatory                                       | MDIO data                                                                                             |

| <b>PRU-ICSS MII PORT0</b>                                       |                                                 |                                                                                                       |

| <b>PRU-ICSS MII PORT1</b>                                       |                                                 |                                                                                                       |

| prX_mii_mt0_clk                                                 | Mandatory                                       | MII0 and MII1 transmit clock                                                                          |

| prX_mii_mt1_clk                                                 |                                                 |                                                                                                       |

| prX_mii0_txd3                                                   | Mandatory                                       | MII0 and MII1 transmit data3                                                                          |

| prX_mii1_txd3                                                   |                                                 |                                                                                                       |

| prX_mii0_txd2                                                   | Mandatory                                       | MII0 and MII1 transmit data2                                                                          |

| prX_mii1_txd2                                                   |                                                 |                                                                                                       |

| prX_mii0_txd1                                                   | Mandatory                                       | MII0 and MII1 transmit data1                                                                          |

| prX_mii1_txd1                                                   |                                                 |                                                                                                       |

| prX_mii0_txd0                                                   | Mandatory                                       | MII0 and MII1 transmit data0                                                                          |

| prX_mii1_txd0                                                   |                                                 |                                                                                                       |

| prX_mii0_rxd3                                                   | Mandatory                                       | MII0 and MII1 receive data3                                                                           |

| prX_mii1_rxd3                                                   |                                                 |                                                                                                       |

| prX_mii0_rxd2                                                   | Mandatory                                       | MII0 and MII1 receive data2                                                                           |

| prX_mii1_rxd2                                                   |                                                 |                                                                                                       |

| prX_mii0_rxd1                                                   | Mandatory                                       | MII0 and MII1 receive data1                                                                           |

| prX_mii1_rxd1                                                   |                                                 |                                                                                                       |

| prX_mii0_rxd0                                                   | Mandatory                                       | MII0 and MII1 receive data0                                                                           |

| prX_mii1_rxd0                                                   |                                                 |                                                                                                       |

| prX_mii0_txen                                                   | Mandatory                                       | MII0 and MII1 TX enable                                                                               |

| prX_mii1_txen                                                   |                                                 |                                                                                                       |

| prX_mii_mr0_clk                                                 | Mandatory                                       | MII0 and MII1 receive clock                                                                           |

| prX_mii_mr1_clk                                                 |                                                 |                                                                                                       |

| prX_mii0_rxdv                                                   | Mandatory                                       | MII0 and MII1 RX data valid                                                                           |

| prX_mii1_rxdv                                                   |                                                 |                                                                                                       |

| prX_mii0_rxer                                                   | Mandatory                                       | MII0 and MII1 RXERR                                                                                   |

| prX_mii1_rxer                                                   |                                                 |                                                                                                       |

| prX_mii0_rxlink                                                 | Optional                                        | For fast link loss detection - connect LED_LINK/LED_SPEED from PHY here and enable MLINK mode in MDIO |

| prX_mii1_rxlink                                                 |                                                 |                                                                                                       |

| prX_mii0_crs                                                    | Optional                                        | Required to enable half duplex support on MII0                                                        |

| prX_mii0_col                                                    |                                                 |                                                                                                       |

| prX_mii1_crs                                                    | Optional                                        | Required to enable half duplex support on MII1                                                        |

| prX_mii1_col                                                    |                                                 |                                                                                                       |

| <b>PRU-ICSS PTP/1588 Clocks (Network clock synchronization)</b> |                                                 |                                                                                                       |

| prX_edc_sync0_out                                               | Recommended<br>(for PTP/1588<br>capable slaves) | SYNC0 out - Time synchronized OUT0                                                                    |

## Certification Information

Certification was done on [AM335x ICEv2](#) board on EtherNet/IP firmware using Industrial SDK 1.1.0.5 release as the base in July 2014.

### Declaration of Conformity to the EtherNet/IP™ Specification

ODVA hereby issues this Declaration of Conformity to *The EtherNet/IP™ Specification* for the product(s) described below. The Vendor listed below (the "Vendor") holds a valid Terms of Usage Agreement, which is incorporated herein by reference, for the EtherNet/IP Technology from ODVA, thereby agreeing that it is the Vendor's ultimate responsibility to assure that its EtherNet/IP Compliant Products conform to *The EtherNet/IP Specification* and that *The EtherNet/IP Specification* is provided by ODVA to the Vendor on an AS IS basis without warranty. NO WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE BEING PROVIDED BY ODVA.

In recognition of the below EtherNet/IP Compliant Product(s) having been EtherNet/IP Conformance Tested at ODVA-authorized Test Service Provider and having received a passing result from ODVA at the Composite Test Revision Level specified below, this Declaration of Conformity authorizes the Vendor to use the EtherNet/IP Certification Marks in conjunction with the specific EtherNet/IP Compliant Product(s) described below, for so long as the Vendor's Terms of Usage Agreement for the EtherNet/IP Technology remains valid.

EtherNet/IP CONFORMANCE TESTED™

Certification Logo Mark

Certification Word Mark

This Declaration of Conformity is issued on October 13, 2014, on behalf of ODVA by:

Katherine Voss

Executive Director

| Vendor Information                                                               |                            |                            |                                |                                         |

|----------------------------------------------------------------------------------|----------------------------|----------------------------|--------------------------------|-----------------------------------------|

| Vendor Name                                                                      | Texas Instruments          |                            |                                |                                         |

| Test Information                                                                 |                            |                            |                                |                                         |

| Test Date                                                                        | May 15, 2014               |                            |                                |                                         |

| Composite Test Revision                                                          | CT11                       |                            |                                |                                         |

| ODVA File Number                                                                 | 11290.01                   |                            |                                |                                         |

| Product Information                                                              |                            |                            |                                |                                         |

| Network Category: Node                                                           |                            |                            |                                |                                         |

| Identity Object Instance                                                         |                            |                            |                                |                                         |

| Vendor ID (Attribute 1)                                                          | 806                        |                            |                                |                                         |

| Device Type (Attribute 2)                                                        | 0x0C                       |                            |                                |                                         |

| Device Profile Name                                                              | Communications Adapter     |                            |                                |                                         |

| Products Covered under this Declaration of Conformity (Identity Object Instance) |                            |                            |                                |                                         |

| No.                                                                              | Product Code (Attribute 3) | Product Name (Attribute 7) | Product Revision (Attribute 4) | SOC File Name                           |

| 1                                                                                | 1026                       | TI/Molex EIP Adapter       | 1.001                          | <a href="#">TI_EIP_ICSS_Adapter.stc</a> |

## References

1. EtherNet/IP on Sitara Processors – [spry249](#)

2. Industrial Communications Solution Guide - [slyy050b](#)

3. [EtherNet/IP Communications Development Platform](#)

4. [Certified EtherNet/IP Adapter device](#)

5. [Molex EtherNet/IP Stack](#)

6. [EtherNet/IP Developer Guide](#)

## Acronyms

| Acronym    | Description                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------|

| AL         | Application Layer                                                                                              |

| ASIC       | Application Specific Integrated Circuit                                                                        |

| AM3 family | Implies AM3x, AM4x, AMIC110x class of devices because they use identical firmware                              |

| AM5 family | Implies AM57x, K2G class of devices because they use identical firmware                                        |

| DL         | Datalink Layer                                                                                                 |

| DLR        | Device Level Ring                                                                                              |

| DOC        | Declaration of Conformity (certification from ODVA)                                                            |

| EDMA       | Enhanced Direct Memory Access                                                                                  |

| FDB        | Forwarding Data Base                                                                                           |

| ISR        | Interrupt Service Routine                                                                                      |

| MDIO       | Management Data Input Output                                                                                   |

| MII        | Media Independent Interface                                                                                    |

| ODVA       | Open Device Vendors Association (Standards body for EtherNet IP)                                               |

| OS         | Operating Systems                                                                                              |

| PRUSS      | Programmable RealTime Unit Sub System                                                                          |

| PRU-ICSS   | Programmable RealTime Unit - Industrial Communication Sub System - PRUSS with industrial communication support |

| PTP-1588   | Precision Time Protocol (IEEE time synchronization protocol)                                                   |

| RPI        | Requested Packet Interval                                                                                      |

## IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have **not** been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

### Products

Audio [www.ti.com/audio](http://www.ti.com/audio)

Amplifiers [amplifier.ti.com](http://amplifier.ti.com)

Data Converters [dataconverter.ti.com](http://dataconverter.ti.com)

DLP® Products [www.dlp.com](http://www.dlp.com)

DSP [dsp.ti.com](http://dsp.ti.com)

Clocks and Timers [www.ti.com/clocks](http://www.ti.com/clocks)

Interface [interface.ti.com](http://interface.ti.com)

Logic [logic.ti.com](http://logic.ti.com)

Power Mgmt [power.ti.com](http://power.ti.com)

Microcontrollers [microcontroller.ti.com](http://microcontroller.ti.com)

RFID [www.ti-rfid.com](http://www.ti-rfid.com)

OMAP Applications Processors [www.ti.com/omap](http://www.ti.com/omap)

Wireless Connectivity [www.ti.com/wirelessconnectivity](http://www.ti.com/wirelessconnectivity)

### Applications

Automotive and Transportation [www.ti.com/automotive](http://www.ti.com/automotive)

Communications and Telecom [www.ti.com/communications](http://www.ti.com/communications)

Computers and Peripherals [www.ti.com/computers](http://www.ti.com/computers)

Consumer Electronics [www.ti.com/consumer-apps](http://www.ti.com/consumer-apps)

Energy and Lighting [www.ti.com/energy](http://www.ti.com/energy)

Industrial [www.ti.com/industrial](http://www.ti.com/industrial)

Medical [www.ti.com/medical](http://www.ti.com/medical)

Security [www.ti.com/security](http://www.ti.com/security)

Space, Avionics and Defense [www.ti.com/space-avionics-defense](http://www.ti.com/space-avionics-defense)

Video and Imaging [www.ti.com/video](http://www.ti.com/video)

### TI E2E Community

[e2e.ti.com](http://e2e.ti.com)