# Shared RAM Access Considerations on OMAPL1x/C674x/AM1x

### **Contents**

Memory Access Considertions on OMAPL1x/C674x/AM1x Devices

Non-cacheable Writes/Stores

Reads/Loads/Cache Fill

Shared RAM Access Considerations on OMAPL1x/C674x/AM1x

## Memory Access Considertions on OMAPL1x/C674x/AM1x Devices

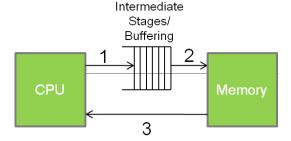

### Non-cacheable Writes/Stores

- "Buffered" or "fire-n-forget"

- Multiple transactions can be in flight at a time.

- Transactions progress through buffers or pipeline elements at each stage of the design

- In DSP memory system

- In SCR+ bridges (System Interconnect)

- In SRAM controller

- CPU doesn't have to wait for first transaction to complete at destination before starting next write

- Latency (at least for sender) is a don't care.

- Message can land at arbitrary later point in time.

- CPU write throughput is limited by:

- Throughput of #1 while buffer is empty

- Throughput of #2 while buffer is full

- For SRAM writes #1 Throughput == #2 Throughput

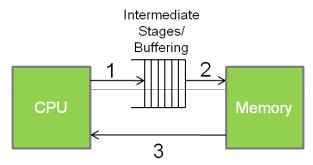

### Reads/Loads/Cache Fill

- "Pended" or "Blocking"

- New Read command cannot be issued until previous read is complete.

- Latency impacts Throughput

- 1 and 2 represent latency for read command through system interconnnect (SCR+bridges)

- 3 represents read response data back to the initiator

- CPU read throughput is limited by:

- Latency of #1, plus

- Latency of #2, plus

- Latency of #3, plus

- Number of dataphases

- LDW = 4 Bytes = 1 phase/cycle

- LDDW = 8 Bytes = 1 phase/cycle

- Cache Fill = 128 Bytes = 16 phases/cycles

### Shared RAM Access Considerations on OMAPL1x/C674x/AM1x

OMAPL1x/C674x/AM1x family of devices have upto 128KB of on chip memory outside the c674x DSP megamodule and ARM9 internal memory.

The following table provides the latency/throughput details for Shared RAM for accesses made by the DSP or ARM on these devices

#### **Shared RAM Access Considerations**

|        | Access Size | C674x DSP        |                          | ARM9             |                          |

|--------|-------------|------------------|--------------------------|------------------|--------------------------|

|        | Bytes       | Latency (cycles) | Throughput (Bytes/Cycle) | Latency (cycles) | Throughput (Bytes/Cycle) |

| Writes | 4           | 16               | 0.25                     | 6                | 0.67                     |

|        | 8           | 16               | 0.5                      | 6                | 1.33                     |

| Reads  | 4           | 32               | 0.13                     | 27               | 0.15                     |

| Troudo | 8           | 32               | 0.25                     | 27               | 0.3                      |

|        | 32          |                  |                          | 31               | 1.03                     |

|        | 128         | 48               | 2.67                     |                  |                          |

#### Keystone=

{{

1. switchcategory:MultiCore=

- For technical support on MultiCore devices, please post your questions in the C6000 MultiCore Forum

- For questions related to the BIOS MultiCore SDK (MCSDK), please use the **BIOS Forum**

OMAPL1x/C674x/AM1x here

For technical support on MultiCore devices, please post your questions in the C6000 MultiCore Forum

For questions related to the **BIOS MultiCore** SDK (MCSDK), please use the **BIOS Forum**

please post your questions on The C2000 your questions on The comments about the article Shared RAM Access Considerations on

C2000=For technical

support on the C2000

only OMAPL1x/C674x/AM1x OMAPL1x/C674x/AM1x OMAPL1x/C674x/AM1x OMAPL1x/C674x/AM1x

DaVinci=For technical support on DaVincoplease post Forum. Please post only DaVinci Forum. Please post only comments RAM Access Considerations on

MSP430=For technical support on MSP430 please post your questions on The post only comments about the article Shared about the article Shared article Shared RAM RAM Access Considerations on

Switches & Multiplexers

Wireless Connectivity

Temperature Sensors & Control ICs

here.

OMAP35x=For technical support on OMAP please post your questions on The OMAP MSP430 Forum, Please Forum, Please post only comments about the Access Considerations on here.

Please post only comments related Please to the article Shared RAM Access comments related to the here.

on article Shared Access Considerations

on

OMAPL1x/C674x/AM1x

here.

#### Links

here.

Considerations

Amplifiers & Linear Audio Broadband RF/IF & Digital Radio

Clocks & Timers Data Converters

**DLP & MEMS** High-Reliability Interface Logic

Power Management

Processors

- ARM Processors

- Digital Signal Processors (DSP)

- Microcontrollers (MCU)

- **OMAP Applications Processors**

Retrieved from "https://processors.wiki.ti.com/index.php?title=Shared\_RAM\_Access\_Considerations\_on\_OMAPL1x/C674x/AM1x&oldid=62331"

This page was last edited on 14 June 2011, at 16:17.

Content is available under Creative Commons Attribution-ShareAlike unless otherwise noted.