## TMS320C55x DSP Peripherals Overview Reference Guide

Literature Number: SPRU317H April 2006

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated

## Preface

## **Read This First**

### About This Manual

This manual is for the peripherals that are on the digital signal processors (DSPs) in the TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP generation.

This manual is in transition. Most peripheral information has been revised and moved from chapters in this manual to separate documents. These separate documents are referenced in Chapter 1. The peripheral information that is still in this manual is being revised and will be in separate documents in the future. When the revisions are complete, this manual is to remain as an overview that points to all of the separate documents. In some cases, information has been moved from this manual to the device-specific data manuals.

#### Notational Conventions

This document uses the following conventions:

- ☐ If an underscore is appended to the name of a signal (for example, RESET\_), the signal is active low.

- □ In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers usually are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form: 0100b

#### **Related Documentation From Texas Instruments**

The following documents describe the C55x devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

**TMS320VC5501 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS206) describes the features of the TMS320VC5501 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5502** Fixed-Point Digital Signal Processor Data Manual (literature number SPRS166) describes the features of the TMS320VC5502 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5509 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS163) describes the features of the TMS320VC5509 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5509A Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS205) describes the features of the TMS320VC5509A fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5510 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS076) describes the features of the TMS320VC5510 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320C55x Technical Overview** (literature number SPRU393). This overview is an introduction to the TMS320C55x DSPs, the latest generation of fixed-point DSPs in the TMS320C5000<sup>™</sup> DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features.

- *TMS320C55x DSP CPU Reference Guide* (literature number SPRU371) describes the architecture, registers, and operation of the CPU for the TMS320C55x DSPs.

- **TMS320C55x DSP Algebraic Instruction Set Reference Guide** (literature number SPRU375) describes the TMS320C55x DSP algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- **TMS320C55x DSP Mnemonic Instruction Set Reference Guide** (literature number SPRU374) describes the TMS320C55x DSP mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x Optimizing C/C++ Compiler User's Guide** (literature number SPRU281) describes the TMS320C55x<sup>™</sup> C/C++ Compiler. This C/C++ compiler accepts ISO standard C and C++ source code and produces assembly language source code for TMS320C55x devices.

- **TMS320C55x Assembly Language Tools User's Guide** (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x devices.

- **TMS320C55x DSP Programmer's Guide** (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x DSPs and explains how to write code that uses special features and instructions of the DSPs.

#### Trademarks

TMS320C5000, TMS320C55x, and C55x are trademarks of Texas Instruments.

MultiMediaCard is a trademark of the MultiMediaCard Association.

Other trademarks are the property of their respective owners.

# **Contents**

| 1 | Gives         | an ove            | <b>DSP Peripherals Overview</b><br>rview of which peripherals are available on the various TMS320C55x DSPs.<br>a chapter in this manual or to another document for details about each peripheral.  | 1-1 |

|---|---------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | [The ]        | ADC is            | <b>gital Converter (ADC)</b><br><i>described in the</i> TMS320VC5509 DSP Analog-to-Digital Converter (ADC)<br>ide ( <i>literature number SPRU586</i> ).]                                           | 2-1 |

| 3 | Descr<br>TMS3 | ibes th<br>20VC55 | ator<br>e clock generator that is in TMS320VC5509, TMS320VC5509A, and<br>510 DSPs. [For information about clock generation in TMS320VC5501 and<br>502 DSPs, see the device-specific data manuals.] |     |

|   | 3.1           | Introdu           | ction to the DSP Clock Generator                                                                                                                                                                   | 3-2 |

|   | 3.2           |                   | ional Flow of the DSP Clock Generator                                                                                                                                                              |     |

|   | 3.3           | •                 | Mode                                                                                                                                                                                               |     |

|   |               | 3.3.1             | Entering and Exiting the Bypass Mode                                                                                                                                                               |     |

|   |               | 3.3.2             | CLKMD Bits Used in the Bypass Mode                                                                                                                                                                 |     |

|   |               | 3.3.3             | Setting the Output Frequency for the Bypass Mode                                                                                                                                                   |     |

|   | 3.4           | Lock M            | lode                                                                                                                                                                                               |     |

|   |               | 3.4.1             | Entering and Exiting the Lock Mode                                                                                                                                                                 | 3-6 |

|   |               | 3.4.2             | CLKMD Bits Used in the Lock Mode                                                                                                                                                                   |     |

|   |               | 3.4.3             | Setting the Output Frequency for the Lock Mode                                                                                                                                                     | 3-7 |

|   |               | 3.4.4             | Lock Time                                                                                                                                                                                          | 3-7 |

|   | 3.5           | Idle (Lo          | ow-Power) Mode                                                                                                                                                                                     | 3-8 |

|   | 3.6           | The CL            | KOUT Pin and the Associated Clock Divider                                                                                                                                                          | 3-9 |

|   | 3.7           | DSP R             | eset Conditions of the DSP Clock Generator                                                                                                                                                         | -10 |

|   |               | 3.7.1             | Clock Generator During Reset 3                                                                                                                                                                     |     |

|   |               | 3.7.2             | Clock Generator After Reset 3                                                                                                                                                                      |     |

|   | 3.8           | Clock N           | Mode Register (CLKMD) 3                                                                                                                                                                            | -12 |

| 4 | <b>Direct Memory Access (DMA) Controller</b><br>[The DMA controller that is in TMS320VC5501 and TMS320VC5502 DSPs is described in the TMS320VC5501/5502 DSP Direct Memory Access (DMA) Controller Reference Guide (literature number SPRU613). The DMA controller that is in TMS320VC5509, TMS320VC5509A, and TMS320VC5510 DSPs is described in the TMS320VC5509/5510 DSP Direct Memory Access (DMA) Controller Reference Guide (literature number SPRU587).]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 5 | <b>External Memory Interface (EMIF)</b><br>[For the EMIF information that applies to your C55x device, see the corresponding device-specific reference guide: TMS320VC5501/5502 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU621</i> ), TMS320VC5509 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU670</i> ), or TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide ( <i>literature number SPRU590</i> ).] |                                                             |

| 6 | <b>General-Purpose I/O Port</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| 7 | Host Port Interface (HPI)<br>[For the HPI information that applies to your C55x device, see the corresponding<br>device-specific reference guide: TMS320VC5501/5502 DSP Host Port Interface (HPI)<br>Reference Guide (literature number SPRU620), TMS320VC5509 DSP Host Port Interface<br>(HPI) Reference Guide (literature number SPRU619), or TMS320VC5510 DSP Host Port<br>Interface (HPI) Reference Guide (literature number SPRU588).]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

| 8 | Idle Configurations   Describes how to deactivate and reactivate specific domains within a TMS320C55x DSP.   [Check the device-specific data manual for additional information about deactivating and reactivating these domains.]   8.1 Idle Domains   8.2 Idle Configuration Process   8.3 Valid Idle Configurations   8.4 To Change Idle Configurations (Key Conditions)   8.4.1 Condition 1: CLKGEN and CPU Domains Active   8.4.2 Condition 2: CLKGEN Domain Active, CPU Domain Idle   8.4.3 Condition 3: CLKGEN Domain Idle   8.5 Interrupt Handling When the CPU Is Reactivated   8.6 Effect of a DSP Reset on the Idle Domains   8.7 Idle Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-2<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-8 |

| 9 | Instruction Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |

| 10 | Inter-Integrated Circuit (I2C) Module                                                                                                                                                                                                                                                                                                                                                                |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | Multichannel Buffered Serial Port (McBSP)11-1[McBSP information is in the TMS320VC5501/5502/5509/5510 DSP Multichannel BufferedSerial Port (McBSP) Reference Guide (literature number SPRU592).]                                                                                                                                                                                                     |

| 12 | MultiMediaCard / SD Card Controller 12-1   [Information about the MultiMediaCard / SD card controller is in the TMS320VC5509 DSP   MultiMediaCard / SD Card Controller Reference Guide (literature number SPRU593).]                                                                                                                                                                                 |

| 13 | Real-Time Clock (RTC)13-1[Information about the RTC is in the TMS320VC5509 DSP Real-Time Clock (RTC) ReferenceGuide (literature number SPRU594).]                                                                                                                                                                                                                                                    |

| 14 | <b>System Control Registers</b>                                                                                                                                                                                                                                                                                                                                                                      |

| 15 | Timer (General-Purpose)15-1[The general-purpose timer that is in TMS320VC5501 and TMS320VC5502 DSPs is described<br>in the TMS320VC5501/5502 DSP Timers Reference Guide (literature number SPRU618). The<br>general-purpose timer that is in TMS320VC5509, TMS320VC5509A, and TMS320VC5510<br>DSPs is described in the TMS320VC5509/5510 DSP Timers Reference Guide (literature<br>number SPRU595).] |

| 16 | <b>Universal Asynchronous Receiver/Transmitter (UART)</b>                                                                                                                                                                                                                                                                                                                                            |

| 17 | Universal Serial Bus (USB) Module                                                                                                                                                                                                                                                                                                                                                                    |

| 18 | Watchdog Timer18-1[The watchdog timer that is in TMS320VC5501 and TMS320VC5502 DSPs is described in the<br>TMS320VC5501/5502 DSP Timers Reference Guide (literature number SPRU618). The<br>watchdog timer that is in TMS320VC5509 and TMS320VC5509A DSPs is described in the<br>TMS320VC5509/5510 DSP Timers Reference Guide (literature number SPRU595).]                                          |

| Α  | Revision History A-1   Describes the notable changes that were made to this document since its last revision.                                                                                                                                                                                                                                                                                        |

# Figures

| 3–1 | Operational Flow of the DSP Clock Generator                       | 3-3  |

|-----|-------------------------------------------------------------------|------|

| 3–2 | Dividing the CPU Clock for the CLKOUT Pin                         | 3-9  |

| 3–3 | Clock Mode Register (CLKMD)                                       | 3-12 |

| 8–1 | Idle Configuration Process                                        | 8-4  |

| 8–2 | Idle Configuration Register (ICR) and Idle Status Register (ISTR) | 8-9  |

# **Tables**

| 1–1 | TMS320C55x DSP Peripherals                                 | 1-1  |

|-----|------------------------------------------------------------|------|

| 3–1 | Operational States Shown in Figure 3–1                     |      |

| 3–2 | CLKMD Bits Used in the Bypass Mode                         |      |

| 3–3 | CLKMD Bits Used in the Lock Mode                           |      |

| 3–4 | Examples of Selecting a Lock Mode Frequency                |      |

| 3–5 | Effect of CLKDIV Bits on CLKOUT Frequency                  |      |

| 3–6 | Reset Values of CLKMD Bits and The Effects                 |      |

| 3–7 | Bit Field Descriptions for the Clock Mode Register (CLKMD) |      |

| 8–1 | Idle Domains in the DSP                                    |      |

| 8–2 | Changing Idle Configurations                               |      |

| 8–3 | CPU Response After Reactivation                            |      |

| 8–4 | ICR Bit Descriptions                                       |      |

| 8–5 | ISTR Bit Descriptions                                      | 8-11 |

## **TMS320C55x DSP Peripherals Overview**

Table 1–1 lists the peripherals of the TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP generation and indicates how many copies of each peripheral are on the specific C55x devices. The column labeled "5509" applies to both TMS320VC5509 and TMS320VC5509A devices. On a given device, some peripherals may share pins, making the peripherals' use mutually exclusive; see the device-specific data manual for details.

For a detailed description of a peripheral, see the chapter or document listed in the last column of the table. If a peripheral has its own reference guide, the table shows the literature number (SPRUxxx) for that reference guide. If you are viewing the table online, you can click the literature number to view or download a portable document format (PDF) file. Otherwise, you can find the PDF files on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

All information about general-purpose I/O pins and system control registers has been moved from this document to the device-specific data manuals.

| Peripheral                        | 5501 | 5502 | 5509 | 5510 | For Details, See                              |

|-----------------------------------|------|------|------|------|-----------------------------------------------|

| Analog-to-digital converter (ADC) |      |      | 1    |      | SPRU586                                       |

| Clock generator with PLL          |      |      | 1    | 1    | Chapter 3 and the device-specific data manual |

|                                   | 1    | 1    |      |      | Device-specific data manual                   |

| Direct memory access (DMA)        |      |      | 1    | 1    | SPRU587                                       |

| controller                        | 1    | 1    |      |      | SPRU613                                       |

| External memory interface (EMIF)  |      |      |      | 1    | SPRU590                                       |

|                                   |      |      | 1    |      | SPRU670                                       |

|                                   | 1    | 1    |      |      | SPRU621                                       |

Table 1–1. TMS320C55x DSP Peripherals

| Peripheral                                            | 5501 | 5502        | 5509 | 5510 | For Details, See                              |

|-------------------------------------------------------|------|-------------|------|------|-----------------------------------------------|

| -                                                     | 5501 | <b>3302</b> | 2208 |      |                                               |

| Host port interface (HPI)                             |      |             |      | 1    | SPRU588                                       |

|                                                       |      |             | 1    |      | SPRU619                                       |

|                                                       | 1    | 1           |      |      | SPRU620                                       |

| Instruction cache                                     |      |             |      | 1    | SPRU576                                       |

|                                                       | 1    | 1           |      |      | SPRU630                                       |

| Inter-integrated circuit (I2C) module                 | 1    | 1           | 1    |      | SPRU146                                       |

| Multichannel buffered serial port<br>(McBSP)          | 2    | 3           | 3    | 3    | SPRU592                                       |

| MultiMediaCard™ / SD card controller                  |      |             | 2    |      | SPRU593                                       |

| Power management /<br>Idle configurations             | 1    | 1           | 1    | 1    | Chapter 8 and the device-specific data manual |

| Real-time clock (RTC)                                 |      |             | 1    |      | SPRU594                                       |

| Timer, general-purpose                                |      |             | 2    | 2    | SPRU595                                       |

|                                                       | 2    | 2           |      |      | SPRU618                                       |

| Timer, watchdog                                       |      |             | 1    |      | SPRU595                                       |

|                                                       | 1    | 1           |      |      | SPRU618                                       |

| Universal Asynchronous<br>Receiver/Transmitter (UART) | 1    | 1           |      |      | SPRU597                                       |

| Universal Serial Bus (USB) module                     |      |             | 1    |      | SPRU596                                       |

## Table 1–1. TMS320C55x DSP Peripherals (Continued)

## Chapter 2

# **Analog-to-Digital Converter (ADC)**

The ADC is described in the *TMS320VC5509 DSP Analog-to-Digital Converter (ADC) Reference Guide* (literature number SPRU586).

## Chapter 3

## **Clock Generator**

This chapter describes the clock generator that is in TMS320VC5509, TMS320VC5509A, and TMS320VC5510 DSPs. This clock generator accepts an input clock at the CLKIN pin and enables you to modify that signal internally to produce an output clock with the desired frequency. The clock generator passes this output clock (the CPU clock) to the CPU, to peripherals, and to other modules inside the C55x<sup>™</sup> DSP. The CPU clock is also passed through a programmable clock divider to the CLKOUT pin. Check the device-specific data manual for additional clock-generation information.

#### Note:

For information about clock generation in TMS320VC5501 and TMS320VC5502 DSPs, see the device-specific data manuals.

### Topic

#### Page

| 3.1 | Introduction to the DSP Clock Generator             |

|-----|-----------------------------------------------------|

| 3.2 | Operational Flow of the DSP Clock Generator         |

| 3.3 | Bypass Mode 3-5                                     |

| 3.4 | Lock Mode                                           |

| 3.5 | Idle (Low-Power) Mode 3-8                           |

| 3.6 | The CLKOUT Pin and the Associated Clock Divider 3-9 |

| 3.7 | DSP Reset Conditions of the DSP Clock Generator     |

| 3.8 | Clock Mode Register (CLKMD) 3-12                    |

## 3.1 Introduction to the DSP Clock Generator

The DSP clock generator supplies the DSP with a clock signal that is based on an input clock signal connected at the CLKIN pin. Included in the clock generator is a digital phase-lock loop (PLL), which can be enabled or disabled. You can configure the clock generator to create a CPU clock signal that has the desired frequency.

The clock generator has a clock mode register, CLKMD (see section 3.8 on page 3-12), for controlling and monitoring the activity of the clock generator. For example, you can write to the PLL ENABLE bit in CLKMD to toggle between the two main modes of operation:

- □ In the bypass mode (see section 3.3 on page 3-5), the PLL is bypassed, and the frequency of the output clock signal is equal to the frequency of the input clock signal divided by 1, 2, or 4. Because the PLL is disabled, this mode can be used to save power.

- In the lock mode (see section 3.4 on page 3-6), the input frequency can be both multiplied and divided to produce the desired output frequency, and the output clock signal is phase-locked to the input clock signal. The lock mode is entered if the PLL ENABLE bit of the clock mode register is set and the phase-locking sequence is complete. (During the phase-locking sequence, the clock generator is kept in the bypass mode.)

The clock generator also has an idle mode (see section 3.5 on page 3-8) for power conservation. You place the clock generator into its idle mode by turning off the CLKGEN idle domain. For information on turning on and off idle domains, see Chapter 8, *Idle Configurations*.

The output of the clock generator or a divided down version of that output can be seen on the CLKOUT pin. For details, see section 3.6, *The CLKOUT Pin and the Associated Clock Divider*, on page 3-9.

## 3.2 Operational Flow of the DSP Clock Generator

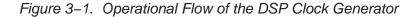

Figure 3–1 and Table 3–1 describe the operational states (A–F) of the DSP clock generator. The clock mode register (CLKMD) is loaded by software or by a DSP reset. If the write to CLKMD enables the PLL, the PLL begins its phase-locking sequence (state A). If the write disables the PLL, the clock generator enters its bypass mode (state D).

Clock Generator 3-3

Table 3–1. Operational States Shown in Figure 3–1

| State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A     | <b>Locking the phase.</b> The clock generator enters the bypass mode, and the PLL locks the phase of the output clock signal to that of the input clock signal. Once the phase is locked and the output signal is at the frequency defined by the PLL MULT bits and the PLL DIV bits of CLKMD, the clock generator enters its lock mode (state B). You can reconfigure the clock generator by writing to CLKMD.                                                                                                                                                           |

| В     | <b>Lock mode.</b> In the lock mode, the PLL is generating an output signal with the selected frequency. The output signal is phase-locked to the input signal. If the PLL loses the lock and the IOB bit of CLKMD is 1, the clock generator returns to the bypass mode and reacquires the lock (state A); if the IOB bit is 0, the clock generator does not reacquire the lock. An idle instruction can place the clock generator into its idle mode (state C). To change to the bypass mode or to reconfigure the clock generator in other ways, you can write to CLKMD. |

| С     | Idle mode (entered from the lock mode). An idle instruction has placed<br>the clock generator into its idle mode. If the idle mode is properly exited, the<br>clock generator starts again and reacquires the phase lock (state A). The<br>method used to reacquire the lock depends on the IAI bit of CLKMD.                                                                                                                                                                                                                                                             |

| D     | <b>Bypass mode.</b> The PLL is disabled, and the clock generator is in the bypass mode. The divider within the clock generator produces an output clock signal at the frequency defined by the BYPASS DIV bits of CLKMD. An idle instruction can place the clock generator into its idle mode (state E). To change to the lock mode or to reconfigure the clock generator in other ways, you can write to CLKMD.                                                                                                                                                          |

| E     | <b>Idle mode (entered from the bypass mode).</b> An idle instruction has placed the clock generator into its idle mode. If the idle mode is properly exited, the clock generator starts again in the bypass mode.                                                                                                                                                                                                                                                                                                                                                         |

### 3.3 Bypass Mode

When the DSP clock generator is in the bypass mode and the phase-lock loop (PLL) is disabled, the frequency of the output clock signal is equal to the frequency of the input clock signal divided by 1, 2, or 4.

#### 3.3.1 Entering and Exiting the Bypass Mode

To enter the bypass mode, write a 0 to the PLL ENABLE bit in the clock mode register (CLKMD). The PLL will be disabled.

To exit the bypass mode, write a 1 to the PLL ENABLE bit. The PLL will start up and enter its phase-locking sequence. After the PLL is generating the configured output frequency and the phase of the output clock signal is locked to the phase of the input clock signal, the clock generator enters the lock mode. Until then, the clock generator stays in the bypass mode.

If the clock generator is in the lock mode and the PLL must reacquire its phase lock (IOB = 1), the clock generator enters the bypass mode until the phase is locked again.

#### 3.3.2 CLKMD Bits Used in the Bypass Mode

Table 3–2 describes the bits of the clock mode register (CLKMD) that are used in the bypass mode. The reserved bits in CLKMD (Rsvd and TEST) should not be used in either the bypass mode or the lock mode. For a detailed description of CLKMD, see section 3.8 on page 3-12.

| CLKMD Bit Field | Role In The Bypass Mode                                                                               |

|-----------------|-------------------------------------------------------------------------------------------------------|

| PLL ENABLE      | Allows you to switch to the lock mode                                                                 |

| BYPASS DIV      | Determines how the input clock frequency is divided (if at all) to produce the output clock frequency |

| LOCK            | Is 0 in the bypass mode                                                                               |

Table 3–2. CLKMD Bits Used in the Bypass Mode

### 3.3.3 Setting the Output Frequency for the Bypass Mode

The output frequency is determined by the input frequency and the value in the BYPASS DIV bits. Load BYPASS DIV as required to divide the input frequency by 1, 2, or 4.

## 3.4 Lock Mode

In the lock mode, the input frequency can be both multiplied and divided to produce the desired output frequency, and the output clock signal is phase-locked to the input clock signal.

### 3.4.1 Entering and Exiting the Lock Mode

To enter the lock mode, write a 1 to the PLL ENABLE bit in the clock mode register (CLKMD). The PLL will start up and will enter its phase-locking sequence. After the PLL is generating the configured output frequency and the phase of the output clock signal is locked to the phase of the input clock signal, the clock generator enters the lock mode. Until then, the clock generator stays in the bypass mode.

If the clock generator is in the lock mode and the PLL must reacquire its phase lock (IOB = 1 in CLKMD), the clock generator will enter the bypass mode until the phase is locked again.

To exit the lock mode (enter the bypass mode), write a 0 to the PLL ENABLE bit. The PLL will be disabled.

#### 3.4.2 CLKMD Bits Used in the Lock Mode

Table 3–3 describes the bits of the clock mode register (CLKMD) that are used in the lock mode. The reserved bits (Rsvd and TEST) in CLKMD should not be used in either the lock mode or the bypass mode. For a detailed description of CLKMD, see section 3.8 on page 3-12.

Table 3–3. CLKMD Bits Used in the Lock Mode

| CLKMD Bit Field(s)   | Role In The Lock Mode                                                                                       |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| PLL ENABLE           | Allows you to switch to the bypass mode (disable the PLL)                                                   |

| PLL MULT and PLL DIV | Determine how the input clock frequency is modified (if at all) to produce the output clock frequency       |

| IAI                  | Determines whether the PLL restarts the phase-locking sequence when the clock generator exits its idle mode |

| BREAKLN              | Indicates when the phase lock has been broken                                                               |

| IOB                  | Determines whether the PLL will reacquire a lost phase lock                                                 |

| LOCK                 | Is 1 in the lock mode                                                                                       |

### 3.4.3 Setting the Output Frequency for the Lock Mode

The input frequency is multiplied by the PLL MULT value of CLKMD and is divided according to the PLL DIV value of CLKMD. PLL MULT can be a value from 2 to 31. PLL DIV can be a value from 0 (divide by 1) to 3 (divide by 4). The output frequency can be calculated with the following equation:

Output frequency =  $\frac{PLL MULT}{(PLL DIV + 1)} \times Input frequency$

Table 3–4 shows some examples of using PLL MULT and PLL DIV to select an output frequency.

| PLL MULT | PLL DIV         | Output Frequency                                 |

|----------|-----------------|--------------------------------------------------|

| 31       | 0 (divide by1)  | $31 \times Input$ frequency (maximum frequency)  |

| 10       | 1 (divide by 2) | $5 \times Input frequency$                       |

| 2        | 2 (divide by 3) | $2/3 \times Input frequency$                     |

| 2        | 3 (divide by 4) | $1/2 \times Input$ frequency (minimum frequency) |

| -        |                 |                                                  |

Table 3–4. Examples of Selecting a Lock Mode Frequency

### 3.4.4 Lock Time

The lock time is dependent on the multiply and divide factors chosen as well as the operating frequency. A good rule of thumb is to estimate 100 us for the lock time.

## 3.5 Idle (Low-Power) Mode

To save power, you can put the DSP clock generator into its idle mode by loading an idle configuration that turns off the CLKGEN idle domain. When the clock generator is idle, the output clock is stopped and held high. For more details, see Chapter 8, *Idle Configurations*.

When the clock generator exits its idle mode, the reaction of the clock generator depends on several factors. If the clock generator was in its bypass mode before the idle instruction was executed, the PLL returns to the bypass mode. If the clock generator was in its lock mode before the idle instruction was executed, the clock generator switches to its bypass mode, reacquires the phase lock, and then returns to the lock mode. The method used for reacquiring the phase lock depends on the IAI bit of CLKMD:

| IAI | Method Used For Reacquiring The Phase Lock                                                                                                                                           |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0   | The PLL does not restart the phase-locking sequence. Instead, the PLL reacquires the phase lock using the same lock settings that were in use just before the idle mode was entered. |  |  |

| 1   | The PLL restarts the phase-locking sequence. This option is recommended if the input clock has or may have changed while the clock generator was idle.                               |  |  |

## 3.6 The CLKOUT Pin and the Associated Clock Divider

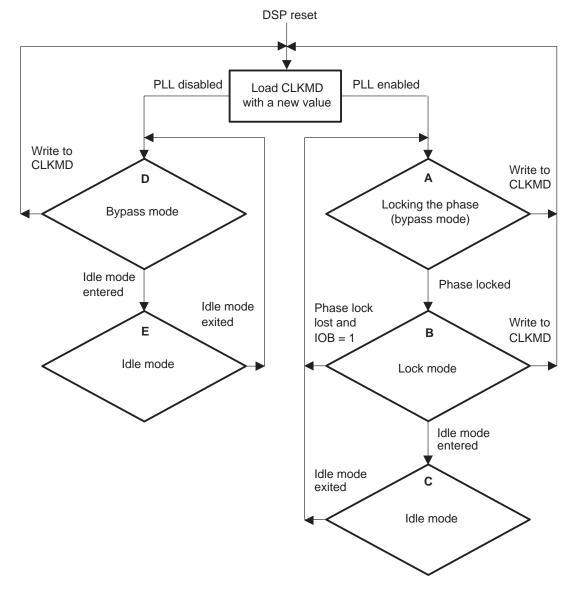

The DSP clock generator generates the CPU clock that is supplied to the CPU, to peripherals, and to other modules inside the DSP. As shown in Figure 3–2, the CPU clock is also passed to a clock divider that supplies a signal (CLKOUT) to the CLKOUT pin. The frequency of CLKOUT depends on the CLKDIV bits of the system register, SYSR (see Table 3–5). Consult the device-specific data manual to determine whether this clock divider feature is available on a particular C55x DSP.

Table 3–5. Effect of CLKDIV Bits on CLKOUT Frequency

| CLKDIV | Frequency of CLKOUT               |

|--------|-----------------------------------|

| 000b   | $1/1 \times CPU$ clock frequency  |

| 001b   | $1/2 \times CPU$ clock frequency  |

| 010b   | $1/4 \times CPU$ clock frequency  |

| 011b   | $1/6 \times CPU$ clock frequency  |

| 100b   | $1/8 \times CPU$ clock frequency  |

| 101b   | $1/10 \times CPU$ clock frequency |

| 110b   | $1/12 \times CPU$ clock frequency |

| 111b   | $1/14 \times CPU$ clock frequency |

|        |                                   |

### 3.7 DSP Reset Conditions of the DSP Clock Generator

The following sections describe the operation of the DSP clock generator when the DSP is held in its reset state and when the DSP is removed from its reset state.

#### 3.7.1 Clock Generator During Reset

The DSP can make use of the output clock signal during reset. While the DSP reset signal is held low:

- The clock generator is in the bypass mode.

- ☐ The output clock frequency is determined by the level of the signal on the CLKMD input pin:

| CLKMD Signal | Output Frequency             |

|--------------|------------------------------|

| Low          | Input frequency              |

| High         | $1/2 \times Input frequency$ |

#### 3.7.2 Clock Generator After Reset

On the rising edge of the DSP reset signal (when reset is deasserted), the clock mode register is loaded with a value determined by the level on the CLKMD pin:

| CLKMD Signal | Clock Mode Register Value |

|--------------|---------------------------|

| Low          | 2002h                     |

| High         | 2006h                     |

Table 3–6 summarizes the effects of this load to the clock mode register.

| Reset Value                                                                             | Effect                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAI = 0                                                                                 | Only applicable in the lock mode. Initialize-after-idle is<br>not selected. After the idle mode is exited, the PLL<br>reacquires the phase lock using the same lock settings<br>that were in use just before the idle mode was entered<br>(the phase-locking sequence is not restarted). |

| IOB= 1                                                                                  | Only applicable in the lock mode. Initialize-on-break is<br>selected. Any time the PLL loses its phase lock, the<br>clock generator switches to its bypass mode and starts<br>a new phase-locking sequence.                                                                              |

| PLL MULT= 00000b<br>PLL DIV= 00b                                                        | Only applicable in the lock mode. The output frequency is equal to the input frequency.                                                                                                                                                                                                  |

| PLL ENABLE = 0                                                                          | The PLL is disabled. The clock generator is in its bypass mode.                                                                                                                                                                                                                          |

| If CLKMD signal is low<br>BYPASS DIV= 00b<br>If CLKMD signal is high<br>BYPASS DIV= 01b | If CLKMD signal is low<br>Output frequency = Input frequency<br>If CLKMD signal is high<br>Output frequency = $1/2 \times$ Input frequency                                                                                                                                               |

| BREAKLN = 1                                                                             | The break-lock indicator is reset.                                                                                                                                                                                                                                                       |

| LOCK = 0                                                                                | The lock-mode indicator reflects the fact that the clock generator is in the bypass mode.                                                                                                                                                                                                |

## 3.8 Clock Mode Register (CLKMD)

You control the DSP clock generator with the clock mode register, CLKMD. Figure 3–3 and Table 3–7 describe the contents of CLKMD, which is accessible in I/O space. After the DSP reset signal becomes inactive, the CLKMD register is initialized with a predetermined value dependent only upon the state of the CLKMD input pin (the difference is in the BYPASS DIV bits):

| CLKMD Signal<br>Level at Reset | CLKMD Register<br>Reset Value |  |  |

|--------------------------------|-------------------------------|--|--|

| Low                            | 2002h                         |  |  |

| High                           | 2006h                         |  |  |

### Figure 3–3. Clock Mode Register (CLKMD)

|   | 15  | 14      | 13      | 12            | 11–7       |         |       |  |

|---|-----|---------|---------|---------------|------------|---------|-------|--|

| R | svd | IAI     | IOB     | TEST (keep 0) | PLL MU     | ILT     |       |  |

|   |     | R/W – 0 | R/W – 1 |               | R/W – 00   | 000     |       |  |

|   |     | 6–5     |         | 4             | 3–2        | 1       | 0     |  |

|   |     | PLL DI  | IV      | PLL ENABLE    | BYPASS DIV | BREAKLN | LOCK  |  |

| · |     | R/W – 0 | 00      | R/W – 0       | R/W – pin  | R – 1   | R – 0 |  |

Legend:

R Read-only access

R/W Read/write access

X is the value after a DSP reset. X = pin indicates that the reset value depends on the signal level on the CLKMD pin.

Table 3–7. Bit Field Descriptions for the Clock Mode Register (CLKMD)

| Bit(s) | Name | Description                                                                                                                                                                              | Reset Value |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 15     | Rsvd | This bit is reserved; it is not available for your use. This bit is always 0.                                                                                                            | -           |

| 14     | IAI  | Initialize after idle bit. IAI determines how the PLL reacquires the phase lock after the clock generator exits its idle mode (when the CLKGEN idle domain is reactivated):              | 0           |

|        |      | 0 The PLL does not restart the phase-locking sequence.<br>Instead the PLL reacquires the lock using the same lock<br>settings that were in use just before the idle mode was<br>entered. |             |

|        |      | 1 The PLL restarts the phase-locking sequence. This option<br>is recommended if the input clock has or may have<br>changed while the clock generator was idle.                           |             |

| Bit(s)        | Name | Description                                                                                                                                                                                                                 | Reset Value |                                                                                                                                                                                                                                                                                                                            |        |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 13 IOB        |      | Initialize on break bit. IOB determines whether the clock generator initializes the PLL phase-locking sequence whenever the phase lock is broken.                                                                           | 1           |                                                                                                                                                                                                                                                                                                                            |        |

|               |      | If the PLL indicates a break in the phase lock:                                                                                                                                                                             |             |                                                                                                                                                                                                                                                                                                                            |        |

|               |      | 0 The clock generator does not interrupt the PLL. The clock generator stays in the lock mode, and the PLL continues to output the current clock signal.                                                                     |             |                                                                                                                                                                                                                                                                                                                            |        |

|               |      | 1 The clock generator switches to its bypass mode and restarts the PLL phase-locking sequence.                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                            |        |

| 12            | TEST | This reserved test bit is cleared during a DSP reset and your program must be keep it 0 for proper operation of the clock generator. Make sure that whenever your program modifies CLKMD, it writes a 0 to bit 12.          | 0           |                                                                                                                                                                                                                                                                                                                            |        |

| 11–7 PLL MULT |      | 11–7                                                                                                                                                                                                                        | PLL MULT    | PLL multiply value. When the PLL is enabled (PLL ENABLE = 1), the frequency of the input clock signal is multiplied according to the value in PLL MULT. PLL MULT can be a value from 2 to 31. The input clock is multiplied by the unsigned integer in PLL MULT and is divided according to the value in the PLL DIV bits. | 00000b |

|               |      | The maximum frequency for the PLL output clock signal is 31 times the frequency of the input clock signal. To obtain this maximum frequency, load PLL MULT with 31 (multiply by 31), and load PLL DIV with 0 (divide by 1). |             |                                                                                                                                                                                                                                                                                                                            |        |

|               |      | The minimum frequency for the output clock signal is 1/2 the frequency of the input clock signal. To obtain this minimum frequency, load PLL MULT with 2 (multiply by 2) and load PLL DIV with 3 (divide by 4).             |             |                                                                                                                                                                                                                                                                                                                            |        |

Table 3–7. Bit Field Descriptions for the Clock Mode Register (CLKMD) (Continued)

Table 3–7. Bit Field Descriptions for the Clock Mode Register (CLKMD) (Continued)

| Bit(s) | Name       | Desc                             | ription                                                                                                                                                                                                                                                                                                                    | Reset Value                                                     |

|--------|------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 6–5    | PLL DIV    | the tw<br>follow                 | divide value. When the PLL is enabled (PLL ENABLE = 1),<br>wo PLL DIV bits select one of four divide options listed in the<br>ring table. The PLL also uses the multiply value supplied by<br>LL MULT bits.                                                                                                                | 00b                                                             |

|        |            |                                  | rogram the minimum or maximum frequency, see the iption for the PLL MULT bits (bits 11–7).                                                                                                                                                                                                                                 |                                                                 |

|        |            | 00b                              | No division/divide by 1<br>The input frequency is not divided.                                                                                                                                                                                                                                                             |                                                                 |

|        |            | 01b                              | Divide by 2<br>The input frequency is divided by 2.                                                                                                                                                                                                                                                                        |                                                                 |

|        |            | 10b                              | Divide by 3<br>The input frequency is divided by 3.                                                                                                                                                                                                                                                                        |                                                                 |

|        |            | 11b                              | Divide by 4<br>The input frequency is divided by 4.                                                                                                                                                                                                                                                                        |                                                                 |

| 4      | PLL ENABLE | PLL.<br>gener<br>enter<br>signal | PLL enable bit. Write to PLL ENABLE to enable or disable the PLL. When you set PLL ENABLE, you request the clock generator to enter the lock mode. The clock generator does not enter the lock mode until the PLL is creating a phase-locked signal with the frequency selected by the PLL MULT bits and the PLL DIV bits. |                                                                 |

|        |            | 0                                | Disable the PLL (enter the bypass mode).                                                                                                                                                                                                                                                                                   |                                                                 |

|        |            | 1                                | Enable the PLL and, when the correct output clock signal is generated, enter the lock mode.                                                                                                                                                                                                                                |                                                                 |

| 3–2    | BYPASS DIV | deteri<br>DSP i<br>reset         | ss-mode divide value. In the bypass mode, BYPASS DIV<br>mines the frequency of the output clock signal. During a<br>reset, if the level on the CLKMD pin is low, BYPASS DIV is<br>to 00b (no division). If the level on CLKMD is high, BYPASS<br>is reset to 01b (divide by 2).                                            | 00b if CLKMD<br>signal is low<br>01b if CLKMD<br>signal is high |

|        |            | 00b                              | No division/divide by 1<br>The frequency of the output clock signal is the same as the<br>frequency of the input clock signal.                                                                                                                                                                                             |                                                                 |

|        |            | 01b                              | Divide by 2<br>The frequency of the output clock signal is 1/2 the<br>frequency of the input clock signal.                                                                                                                                                                                                                 |                                                                 |

|        |            | 10b<br>or<br>11b                 | Divide by 4<br>The frequency of the output clock signal is 1/4 the<br>frequency of the input clock signal.                                                                                                                                                                                                                 |                                                                 |

| Bit(s) | Name    | Description                                                                                                                                                                              | Reset Value |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1      | BREAKLN | Break-lock indicator. BREAKLN indicates whether the PLL has<br>broken the phase lock. In addition, if you write to CLKMD,<br>BREAKLN is forced to 1.                                     | 1           |

|        |         | 0 The PLL has broken the phase lock.                                                                                                                                                     |             |

|        |         | 1 The phase lock is restored, or a write to CLKMD has occurred.                                                                                                                          |             |

| 0      | LOCK    | Lock-mode indicator. LOCK indicates whether the clock generator is in its lock mode:                                                                                                     | 0           |

|        |         | 0 The clock generator is in the bypass mode. The output<br>clock signal has the frequency determined by the<br>BYPASS DIV bits, or the PLL is in the process of getting<br>a phase lock. |             |

|        |         | 1 The clock generator is in the lock mode. The PLL has a phase lock, and the output clock has the frequency determined by the PLL MULT bits and the PLL DIV bits.                        |             |

Table 3–7. Bit Field Descriptions for the Clock Mode Register (CLKMD) (Continued)

## Chapter 4

# **Direct Memory Access (DMA) Controller**

The DMA controller that is in TMS320VC5501 and TMS320VC5502 DSPs is described in the *TMS320VC5501/5502 DSP Direct Memory Access (DMA) Controller Reference Guide* (literature number SPRU613). The DMA controller that is in TMS320VC5509, TMS320VC5509A, and TMS320VC5510 DSPs is described in the *TMS320VC5509/5510 DSP Direct Memory Access* (*DMA*) *Controller Reference Guide* (literature number SPRU587).

## Chapter 5

## **External Memory Interface (EMIF)**

For the EMIF information that applies to your C55x device, see the corresponding device-specific reference guide:

- □ TMS320VC5501/5502 DSP External Memory Interface (EMIF) Reference Guide (literature number SPRU621),

- □ TMS320VC5509 DSP External Memory Interface (EMIF) Reference Guide (literature number SPRU670), or

- □ TMS320VC5510 DSP External Memory Interface (EMIF) Reference Guide (literature number SPRU590).

## Chapter 6

# **General-Purpose I/O Port**

Information about the general-purpose I/O port has been moved to the device-specific data manuals.

## **Host Port Interface (HPI)**

For the HPI information that applies to your C55x device, see the corresponding device-specific reference guide:

- □ TMS320VC5501/5502 DSP Host Port Interface (HPI) Reference Guide (literature number SPRU620),

- □ TMS320VC5509 DSP Host Port Interface (HPI) Reference Guide (literature number SPRU619), or

- □ TMS320VC5510 DSP Host Port Interface (HPI) Reference Guide (literature number SPRU588).

The name "enhanced host port interface (EHPI)" has been reduced to "host port interface (HPI)" to align with a new peripheral naming convention.

## **Idle Configurations**

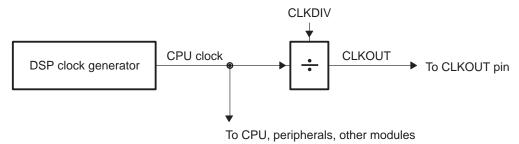

The TMS320C55x DSP is divided into the idle domains described in this chapter. To minimize power consumption, you can choose which domains are active and which domains are idle at any given time. The current state of all domains is collectively called the *idle configuration*.

#### Note:

Check the device-specific data manual for additional information about deactivating and reactivating idle domains of the DSP.

#### Topic

#### Page

| 8.1 | Idle Domains                                       |

|-----|----------------------------------------------------|

| 8.2 | Idle Configuration Process                         |

| 8.3 | Valid Idle Configurations 8-5                      |

| 8.4 | To Change Idle Configurations (Key Conditions) 8-6 |

| 8.5 | Interrupt Handling When the CPU is Reactivated     |

| 8.6 | Effect of a DSP Reset on the Idle Domains          |

| 8.7 | Idle Registers                                     |

#### 8.1 Idle Domains

The DSP is divided into the idle domains described in Table 8–1. You can control which of these idle domains are active and which are idle at any given time, as described in section 8.2.

#### Notes:

- The peripheral bus controller and the host port interface (HPI) on the DSP are not part of any idle domain. The only way to turn these modules off is to put the clock generator into its idle mode (make the CLKGEN domain idle).

- The internal memory blocks (SARAM and DARAM) and the external memory are shared by two domains (CPU and DMA). When both domains are idle, memory accesses are disabled.

| Table 8–1. Idle Domains in the DSF | Table 8–1. | Idle | Domains | in | the | DSP |

|------------------------------------|------------|------|---------|----|-----|-----|

|------------------------------------|------------|------|---------|----|-----|-----|

| Domain | Contents of the Domain                      | Configurability                                                                                                                                                                                                                                                                                                               |

|--------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU    | CPU and CPU buses                           | When the idle instruction is executed, the CPU remains active or becomes idle, depending on the chosen idle configuration.                                                                                                                                                                                                    |