# **KeyStone Architecture Serial Rapid IO (SRIO)**

## **User Guide**

Literature Number: SPRUGW1B November 2012

## **Release History**

| Release       | Date          | Description/Comments                                                                                                                                                                                                                                                |

|---------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPRUGW1B      | November 2012 | Changed ENRX to ENTX in SRIO_SERDES_CFGTX to match the SERDES spec sheet. (Page 3-38)                                                                                                                                                                               |

| 31 110 011 15 | November 2012 | • Changed the ENTX description in SRIO_SERDES_CFGTX to match the SERDES spec sheet. (Page 3-38)                                                                                                                                                                     |

|               |               | • Added more detailed description of EQHLD (Page 3-35)                                                                                                                                                                                                              |

|               |               | Added description of what happens when the RETRY exceeds the RETRY_COUNT in TX Response Handling                                                                                                                                                                    |

|               |               | (Page 2-47)                                                                                                                                                                                                                                                         |

|               |               | • Added SERDES registers to SRIO registers memory map (Page 3-2)                                                                                                                                                                                                    |

|               |               | • Changed ERR_RPT_BH register value to the correct value. (Page 2-83)                                                                                                                                                                                               |

|               |               | Changed PE_FEAT register value to the correct value. (Page 2-83)                                                                                                                                                                                                    |

|               |               | • Changed PLM_SP3_DISCOVERY_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                  |

|               |               | • Changed PLM_SP3_SILENCE_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                    |

|               |               | • Changed PLM_SP2_DISCOVERY_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                  |

|               |               | Changed PLM_SP2_SILENCE_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                      |

|               |               | • Changed PLM_SP1_DISCOVERY_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                  |

|               |               | Changed PLM_SP1_SILENCE_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                      |

|               |               | Changed PLM_SP0_DISCOVERY_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                    |

|               |               | • Changed PLM_SP0_SILENCE_TIMER register value to the correct value. (Page 2-83)                                                                                                                                                                                    |

|               |               | • Changed SP_RT_CTL register value to the correct value. (Page 2-83)                                                                                                                                                                                                |

|               |               | • Changed CC rows from N/A to empty to not confuse users (Page 2-42)                                                                                                                                                                                                |

|               |               | • Changed from cc to CC just to make more consistent with other Register Descriptions (Page 2-42)                                                                                                                                                                   |

|               |               | • Changed from cc to CC just to make more consistent with other Register Descriptions (Page 2-41)                                                                                                                                                                   |

|               |               | • Changed from mailbox to Mailbox just to make more consistent with other Register Descriptions (Page 2-41)                                                                                                                                                         |

|               |               | • Changed from pri to PRI just to make more consistent with other Register Descriptions (Page 2-42)                                                                                                                                                                 |

|               |               | Added cross-reference for value selection for CLKBYP to help readers. (Page 3-32)  Added reverse of hits Page and Aggregation (Page 3-45).                                                                                                                          |

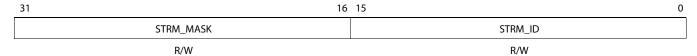

|               |               | Added number of bits Reserved occupies. (Page 2-45)  Added numbers of bits that Stream ID accuraics (Page 2-45)                                                                                                                                                     |

|               |               | <ul> <li>Added numbers of bits that StreamID occupies. (Page 2-45)</li> <li>Added register figures and tables for SERDES registers to Registers chapter of SRIO UG so users can look up registers</li> </ul>                                                        |

|               |               | more easily. They only have to look at the Registers table for ALL SRIO/SERDES registers instead of glancing back and forth between Registers and Functional Description chapters. (Page 3-31)                                                                      |

|               |               | • Changed bit field lengths to match SRIO Module Spec (Page 3-95)                                                                                                                                                                                                   |

|               |               | • Changed column to Amplitude to have it match SERDES Spec sheet. (Page 3-38)                                                                                                                                                                                       |

|               |               | Changed column to Common Mode to have it match SERDES Spec sheet and updated all common mode values in<br>the rows under it. (Page 3-38)                                                                                                                            |

|               |               | • Changed CPPI to CPDMA according to CPPI spec (Page 2-8)                                                                                                                                                                                                           |

|               |               | • Changed field Tt to TT to have a more consistent look in UG (Page 2-46)                                                                                                                                                                                           |

|               |               | <ul> <li>Changed SRIO Register Offset table to also include mention of SRIO SerDes Registers and Error Management<br/>Registers. Also, added cross-reference for all offsets to make user experience easier. (Page 3-1)</li> </ul>                                  |

|               |               | <ul> <li>Deleted all SERDES register figures and tables and added it to the Registers chapter to have a more consistent user<br/>guide. (Page 2-10)</li> </ul>                                                                                                      |

|               |               | • Added more description for MSYNC that matches SERDES spec sheet. (Page 3-38)                                                                                                                                                                                      |

|               |               | <ul> <li>Added note that users should look at another document if they are using SERDES on a Keystone II device. (Page 2-14)</li> <li>Added a more detailed description of the Descriptor Dry Out Condition to be more helpful for the user. (Page 2-39)</li> </ul> |

|               |               | • Changed example code to properly line up with brackets to have a nicer look and easier to read. (Page 2-84)                                                                                                                                                       |

|               |               | • Deleted code that dealt with SP_IP_Mode since there is no SP_IP_Mode register anymore. (Page 2-83)                                                                                                                                                                |

|               |               | <ul> <li>Added note to notify users that they can enable a subset of channels instead of enabling all the channels of RX.<br/>(Page 2-51)</li> </ul>                                                                                                                |

|               |               | • Added Usable Multiple Free Queues section to accurately portay RX Message Mapping (Page 2-39)                                                                                                                                                                     |

|               |               | <ul> <li>Removed RX CPPI Scheme for RapidIO figure because it was an incorrect image of what occurs in RX Message<br/>Mapping (Page 2-39)</li> </ul>                                                                                                                |

|               |               | • Updated SerDes Configuration Example based on the updated (Oct 2012) SerDes Implementation Guide for Keystone I Devices (Page 2-12)                                                                                                                               |

|               |               | • Added cross reference to loopback table to make UG easier to read. (Page 3-35)                                                                                                                                                                                    |

|               |               | • Added Data Streaming PDU Length Error to ERR_DET register to match SRIO specs. (Page 3-103)                                                                                                                                                                       |

|               |               | <ul> <li>Added deeper explanation of TestPattern field for SRIO_SERDES_CFGTX register. Explanation taken from SERDES spec<br/>sheet. (Page 3-38)</li> </ul>                                                                                                         |

|               |               | <ul> <li>Added deeper explanation of TestPattern field for SRIO_SERDES_CFGRX register. Explanation taken from SERDES<br/>spec sheet. (Page 3-35)</li> </ul>                                                                                                         |

www.ti.com

| Release     | Date          | Description/Comments                                                                                                                                                                                                                               |

|-------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPRUGW1B    |               | ·                                                                                                                                                                                                                                                  |

| (continued) | November 2012 | <ul> <li>Added Handling the SRCID Based LSU Error Interrupts in Software section for deeper explanations of Special<br/>Conditions (Page 2-32)</li> </ul>                                                                                          |

|             |               | • Added LSU n Interrupt Condition Routing Register Field Description. (Page 3-59)                                                                                                                                                                  |

|             |               | • Added Long Data Streaming Segment field to ERR_DET register to match SRIO specs. (Page 3-103)                                                                                                                                                    |

|             |               | • Added Missing Data Streaming Context field to ERR_DET register to match SRIO specs. (Page 3-103)                                                                                                                                                 |

|             |               | <ul> <li>Added No Context Available for Type9 Traffic Causing the Packet to be Dropped field to ERR_DET register to match<br/>SRIO specs. (Page 3-103)</li> </ul>                                                                                  |

|             |               | • Added Open Exisiting Data Streaming Context field to ERR_DET register to match SRIO specs. (Page 3-103)                                                                                                                                          |

|             |               | • Added Reserved field to ERR_DET register to match SRIO specs. (Page 3-103)                                                                                                                                                                       |

|             |               | • Added Short Data Streaming Segment field to ERR_DET register to match SRIO specs. (Page 3-103)                                                                                                                                                   |

|             |               | • Changed number of Reserved bits to match SRIO specs. (Page 3-103)                                                                                                                                                                                |

|             |               | • Changed LSU Interrupt Condition Routing Regsiter because the previous explanation was outdated. (Page 3-58)                                                                                                                                      |

|             |               | • Added Behavior of TGT_ID_DIS and MTC_TGT_ID_DIS table from IDT specs (Page 3-130)                                                                                                                                                                |

|             |               | • Added Behavior of TGT_ID_DIS and MTC_TGT_ID_DIS table from IDT specs (Page 3-130)                                                                                                                                                                |

|             |               | • Added description to PRESCALAR_SRV_CLK to discuss options for different ip_clk frequencies. (Page 3-155)                                                                                                                                         |

|             |               | • Added DS_TM and DS rows to match the module spec (Page 3-87)                                                                                                                                                                                     |

|             |               | Added greater drescription for Swap_TX (Page 3-119)                                                                                                                                                                                                |

|             |               | • Added more values and descriptions to have the table match the Interrupt_CTL register (Page 3-59)                                                                                                                                                |

|             |               | • Added more values and descriptions to have the table match the Interrupt_CTL register (Page 3-58)                                                                                                                                                |

|             |               | <ul> <li>Added RIO_SW_PORT CAR register because it was missing. Added Register Table and Register Field Description<br/>(Page 3-87)</li> </ul>                                                                                                     |

|             |               | • Added SR_PORT register table and register field description so added it in memory map. (Page 3-23)                                                                                                                                               |

|             |               | • Changed bit 8 from SBR to SRTC to have it match the module spec. (Page 3-85)                                                                                                                                                                     |

|             |               | • Changed PE_FEAT Field Descriptions table to have it match the module spec. (Page 3-86)                                                                                                                                                           |

|             |               | • Changed number of bits to 3 to match the bit column in the EQ row. (Page 3-35)                                                                                                                                                                   |

|             |               | <ul> <li>Added SerDes Macro Status Register (SRIO_SERDES_STSPLL) because the SERDES_STS register was mentioned above.<br/>(Page 3-31)</li> </ul>                                                                                                   |

|             |               | <ul> <li>Added SerDes Macro Status Register (SRIO_SERDES_STSPLL) Field Description because the SERDES_STS register was<br/>mentioned above. (Page 3-31)</li> </ul>                                                                                 |

|             |               | <ul> <li>Added the SerDes Macro Status Register (SRIO_SERDES_STSPLL) table because the SRIO_SERDES_STS register was<br/>mentioned previously (Page 3-31)</li> </ul>                                                                                |

|             |               | • Changed CDR explanation for 101b to match the SERDES specs. Changed to first order. (Page 3-35)                                                                                                                                                  |

|             |               | • Changed CDR explanation for 000b to match the SERDES specs (Page 3-35)                                                                                                                                                                           |

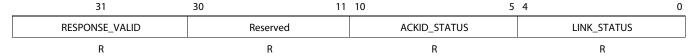

|             |               | • Added additional description for the RESPONSE_VALID field and added its corresponding value (Page 3-95)                                                                                                                                          |

|             |               | • Changed entire row in table to have it match the Garbage_Coll_QID2 figure and SRIO specs (Page 3-82)                                                                                                                                             |

|             |               | • Changed field access so that it matches the Garbage_QID_PROG (Page 3-82)                                                                                                                                                                         |

|             |               | • Changed field name from Reserved to Garbage_QID_PROG to have it match SRIO specs (Page 3-82)                                                                                                                                                     |

|             |               | • Added a description of what happens to the VRANGE with it is set high (Page 3-33)                                                                                                                                                                |

|             |               | • Added a description of what happens to the VRANGE with it is set low (Page 3-33)                                                                                                                                                                 |

|             |               | <ul> <li>Changd the description of the SWING field so it matches the SERDES datasheet (Page 3-38)</li> <li>Changed all steps of all interrupt functions because it use to have SP_IP_MODE and SPn_CTL_INDEP register values (Page 3-56)</li> </ul> |

|             |               | • Changed bit value of all values in LOS because it was only showing two bits at first (Page 3-36)                                                                                                                                                 |

|             |               | • Changed DC-coupled Amplitude voltages of all the values to have it match the SERDES datasheet (Page 3-38)                                                                                                                                        |

|             |               | • Added eight effect of RATE so that it would match Effect of RATE bits table (Page 3-38)                                                                                                                                                          |

|             |               | • Added eight rate operation to RATE to have it match Effect of RATE bits table (Page 3-36)                                                                                                                                                        |

|             |               | • Added MHz to Freq column to verify which units (Page 3-45)                                                                                                                                                                                       |

|             |               | Added MSYNC field to have it match SerDes Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL)     Field Descriptions table (Page 3-37)                                                                                                  |

|             |               | • Changed figure to have it match PER_SET_CNTL1 (Address offset 0x0018) table (Page 3-46)                                                                                                                                                          |

|             |               | Changed FIRUPT field to 19th bit to have it match SerDes Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL) Field Descriptions table (Page 3-37)                                                                                       |

|             |               | • Changed number of bits of SWING to 4 to match Field column of table (Page 3-38)                                                                                                                                                                  |

|             |               | • Changed number of data samples to four so that it would match Effect of RATE bits table (Page 3-36)                                                                                                                                              |

|             |               | Changed number of data samples to one per PLL clock cycle so that it would match Effect of RATE bits table (Page 3-38)                                                                                                                             |

www.ti.com

| Release     | Date          | Description/Comments                                                                                                                                |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| SPRUGW1B    | November 2012 | •Changed number of data samples to two so that it would match Effect of RATE bits table (Page 3-36)                                                 |

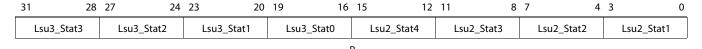

| (continued) |               | • Changed numbering of LSU2_Stat to 3 (Page 2-25)                                                                                                   |

|             |               | • Changed to eighth and added effect so that it would match Effect of RATE bits table (Page 3-38)                                                   |

|             |               | • Changed TWPSTI value to 5 bits instead of 4 bits (Page 3-38)                                                                                      |

|             |               | • Deleted BLK9_EN column from the table because it is not AMU supported. Had to resize table also (Page 2-65)                                       |

|             |               | <ul> <li>Deleted line of code after this<br/>(SRIO REGS-&gt;SW_PORT = 32'h00000400 // 4 ports) because it was not applicable (Page 2-83)</li> </ul> |

|             |               | • Changed sentence to more clearly demonstrate what the multicast operation does and how to enable it (Page 2-2)                                    |

|             |               | • Changed table reference to table EQ Bits because that describes the EQ field more clearly (Page 3-35)                                             |

|             |               | <ul> <li>Deleted all Local DeviceID (under DeviceID Type) cells because they are not appicable to the SRIO Keystone.<br/>(Page 2-2)</li> </ul>      |

|             |               | • Deleted SP_IP_Mode bit 5 because there is no SP_IP_Mode in Keystone. (Page 2-2)                                                                   |

| SPRUGW1A    | October 2011  | • Changed BUSWIDTH field description (Page 3-36)                                                                                                    |

|             |               | • Changed description to reflect packet type functionality (Page 2-36)                                                                              |

|             |               | • Updated LTR description for automatic letter selection (Page 2-41)                                                                                |

|             |               | • Updated section to reflect RX free descriptor queue selection (Page 2-36)                                                                         |

|             |               | • Updated SSIZE field description (Page 2-45)                                                                                                       |

|             |               | • Added the list of logical blocks in the SRIO module (Page 2-66)                                                                                   |

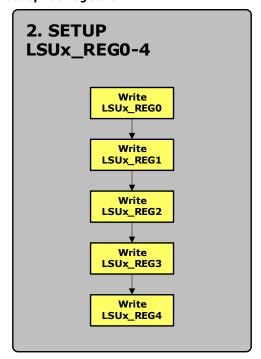

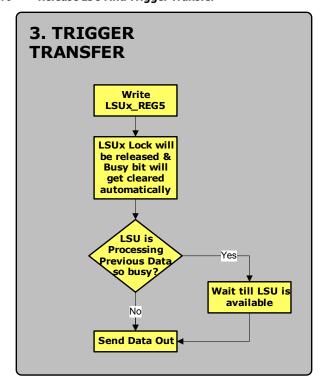

|             |               | • Added the procedure "Writing to LSU_SETUP_REGO" (Page 2-18)                                                                                       |

|             |               | • Added the section "Optimization Techniques" (Page 2-84)                                                                                           |

|             |               | • Added the table "SerDes Lane Configurations for Various Port Widths" (Page 2-14)                                                                  |

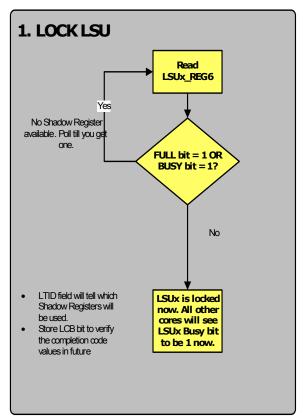

|             |               | • Modified the figure "Lock LSU Registers" (Page 2-22)                                                                                              |

|             |               | • Updated the figure "Programming Details of the LSU" (Page 2-35)                                                                                   |

|             |               | • Updated the Packet Types table (Page 2-7)                                                                                                         |

|             |               | • Updated the table "Line Rate Versus PLL Output Clock Frequency" (Page 3-33)                                                                       |

| SPRUGW1     | November 2010 | Initial Release                                                                                                                                     |

www.ti.com Contents

#### **Contents**

|           | Release History. Ø-in List of Tables Ø-xv. List of Figures Ø-xv. List of Examples Ø-xx.                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

|           | PrefaceØ-xxiiiAbout This Manualø-xxiiiNotational Conventionsø-xxiiiRelated Documentation from Texas Instrumentsø-xxivTrademarksø-xxiv |

| Chapter 1 |                                                                                                                                       |

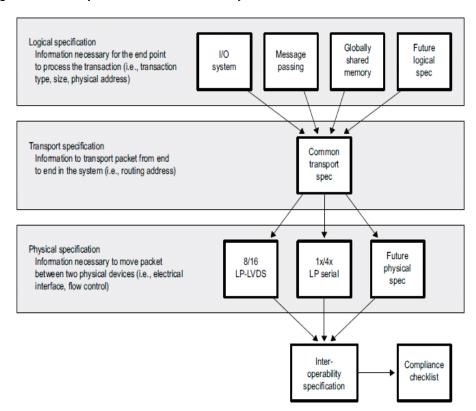

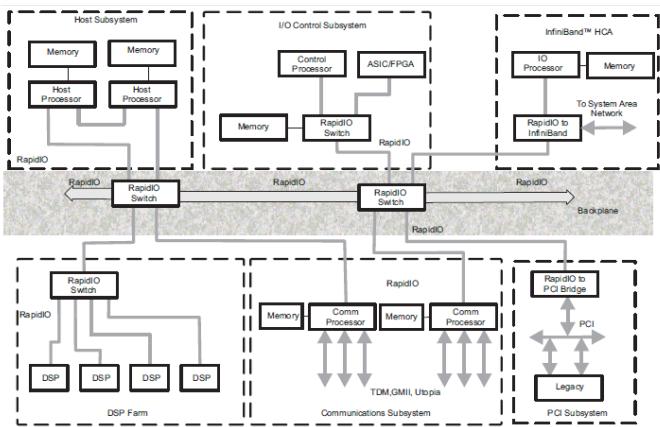

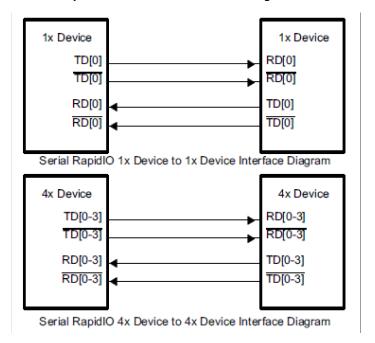

| ·         | Introduction 1-1  1.1 General RapidlO System. 1-2  1.1.1 RapidlO Architectural Hierarchy 1-2                                          |

|           | 1.1.2 RapidlO Interconnect Architecture                                                                                               |

|           | 1.3 Standards1-71.4 External Devices Requirements1-8                                                                                  |

| Chapter 2 |                                                                                                                                       |

|           | SRIO Functional Description 2-1                                                                                                       |

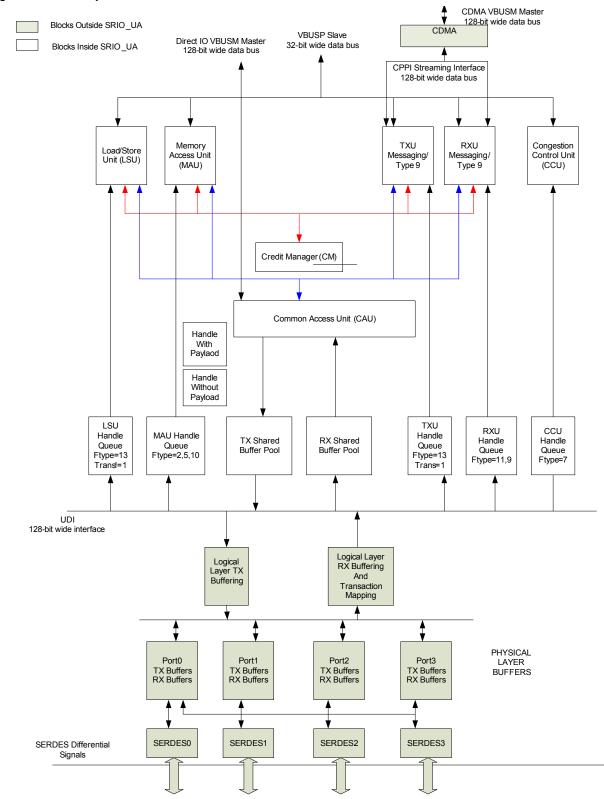

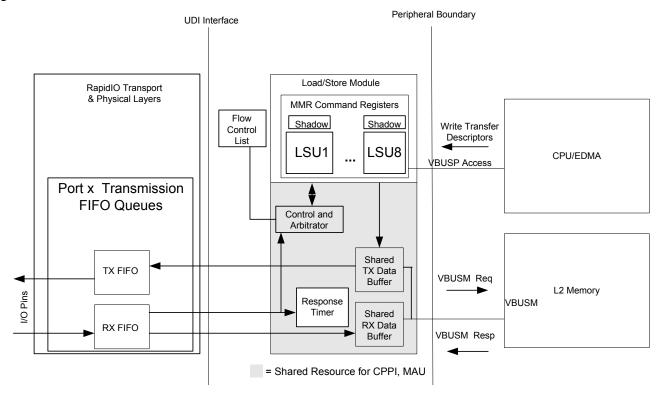

|           | 2.1 Overview                                                                                                                          |

|           | 2.1.1 Peripheral Data Flow2-2                                                                                                         |

|           | 2.1.2 SRIO Packets2-5                                                                                                                 |

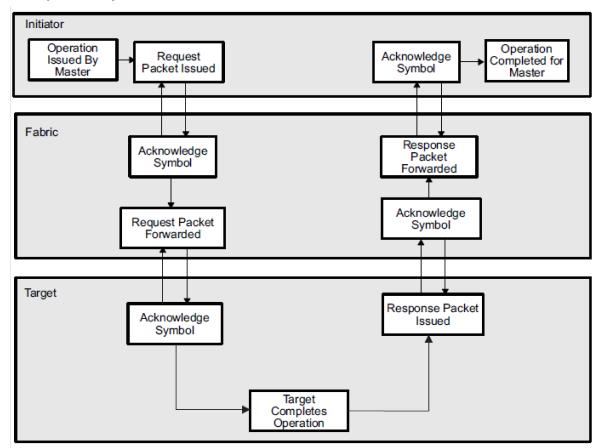

|           | 2.1.2.1 Operation Sequence2-5                                                                                                         |

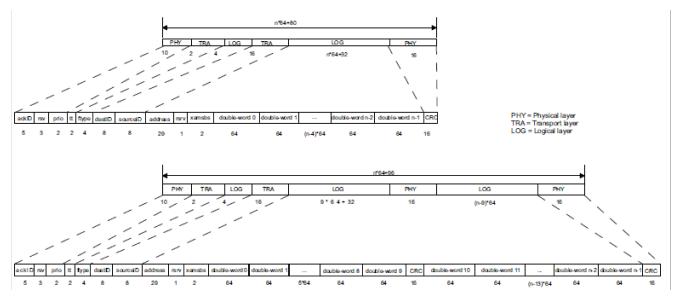

|           | 2.1.2.2 Example Packet—Streaming Write2-6                                                                                             |

|           | 2.1.2.3 Control Symbols                                                                                                               |

|           | 2.1.2.4 SRIO Packet Type                                                                                                              |

|           | 2.2 SRIO Pins                                                                                                                         |

|           | 2.3 Functional Operation                                                                                                              |

|           | 2.3.1.1 Enabling the PLL                                                                                                              |

|           | 2.3.1.2 Enabling the Receiver                                                                                                         |

|           | 2.3.1.3 Enabling the Transmitter2-12                                                                                                  |

|           | 2.3.1.4 SerDes Configuration Example2-12                                                                                              |

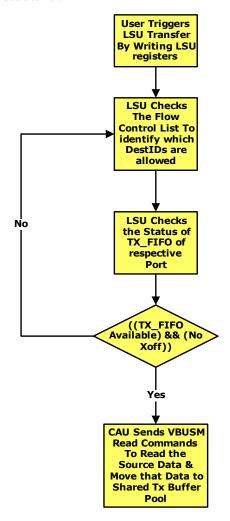

|           | 2.3.2 Direct I/O Operation2-14                                                                                                        |

|           | 2.3.2.1 Detailed Data Path Description                                                                                                |

|           | 2.3.2.2 TX Operation                                                                                                                  |

|           | 2.3.2.3 RX Operation                                                                                                                  |

|           | 2.3.2.4 Reset and Powerdown                                                                                                           |

|           | 2.3.2.5 Special Conditions.       2-31         2.3.2.6 Scheduling.       2-33                                                         |

|           | 2.3.2.7 Error Handling                                                                                                                |

|           | 2.3.2.8 DirectlO Programming Considerations                                                                                           |

|           | 2.3.3 Message Passing                                                                                                                 |

|           | 2.3.3.1 RX Operation                                                                                                                  |

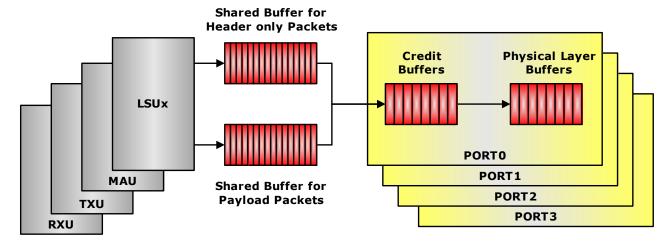

|           | 2.3.3.2 TX Operation2-43                                                                                                              |

|           | 2.3.3.3 Message Passing Software Requirements2-48                                                                                     |

|           | 2.3.4 Maintenance                                                                                                                     |

www.ti.com

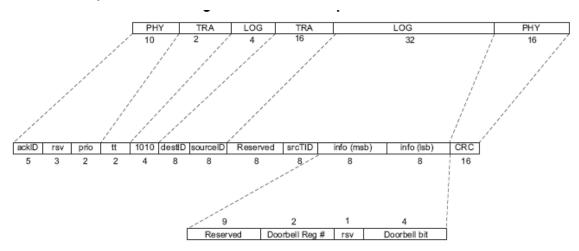

|     | 2.3.5 Doorbell Operation                                     |     |

|-----|--------------------------------------------------------------|-----|

|     | 2.3.6 Atomic Operations                                      |     |

|     | 2.3.7 Congestion Control                                     |     |

|     | 2.3.7.1 Detailed Description                                 |     |

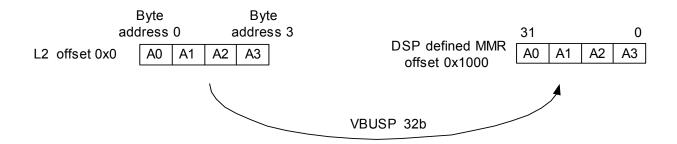

|     | 2.3.8 Endianness                                             |     |

|     | 2.3.8.1 Translation for Memory Mapped Register Space         |     |

|     | 2.3.8.2 Translation for Payload Data                         |     |

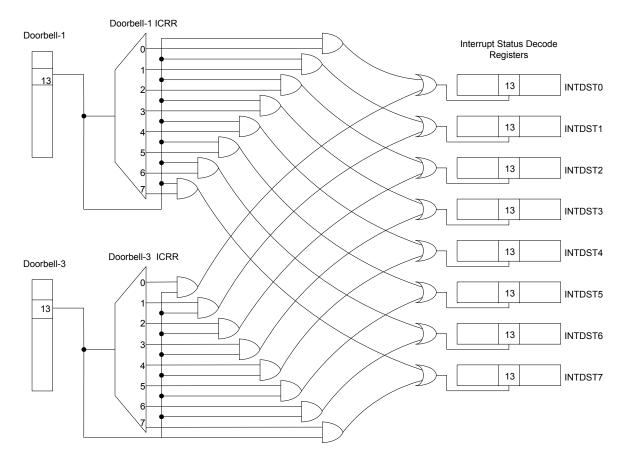

|     | 2.3.9 Interrupt Operation                                    |     |

|     | 2.3.9.1 General Description                                  |     |

|     | 2.3.9.2 Interrupt Registers.                                 |     |

|     | 2.3.9.3 Interrupt Handling.                                  |     |

|     | 2.3.9.4 Interrupt Pacing                                     |     |

|     |                                                              |     |

|     | 2.3.10.1 Reset and Powerdown Summary.                        |     |

|     | 2.3.10.2 Software Shutdown Details                           |     |

|     | 2.3.11.1 Device Reset with Continued RapidIO Operation       |     |

|     | 2.3.11.2 RapidIO Reset with Continued Device Operation       |     |

|     | 2.3.12 Rx Multicast and Multiple DestID Support              |     |

|     | 2.3.12 TX Multicast and Multiple Destild Support             |     |

|     | 2.3.12.2 Promiscuous ID and DestID support.                  |     |

|     | 2.3.13 Daisy Chain Operation and Packet Forwarding.          |     |

|     | 2.3.14 Error Handling and Logging                            |     |

|     | 2.3.15 Initialization Example                                |     |

|     | 2.3.15.1 Enabling SRIO Peripheral                            |     |

|     | 2.3.15.2 PLL, Ports, Device ID and Data Rate Initialization. |     |

|     | 2.3.15.3 Peripheral Initializations                          |     |

|     | 2.3.16 Optimization Techniques                               |     |

|     | 2.3.16.1 Overview                                            |     |

|     | 2.3.16.2 Packet Segmentation.                                |     |

|     | 2.3.16.3 Packet DMA Channel Configuration.                   |     |

|     | 2.3.16.4 Context Allocation                                  |     |

|     | 2.3.16.5 Receive Flow Configuration.                         |     |

|     | 2.3.16.6 Priority Scheduling                                 |     |

|     | 2.3.16.7 Transmit and Receive Operations                     |     |

|     |                                                              |     |

| SRI | IO Registers                                                 | 3-1 |

|     | SerDes Macro Registers                                       |     |

| 3.1 | 3.1.1 SerDes Macro Status Register                           |     |

|     | 3.1.2 SerDes Macro Configuration Register                    |     |

| 2 2 | SerDes Receive/Transmit Channel Configuration Registers      |     |

| 3.2 | 3.2.1 SerDes Receive Channel Configuration Register[0-3]     |     |

|     | 3.2.2 SerDes Transmit Channel Configuration Register[0-3]    |     |

| 2 2 | Required Peripheral Registers                                |     |

| 3.3 | 3.3.1 Peripheral ID Register (PID)                           |     |

|     | · · · · · · · · · · · · · · · · · · ·                        |     |

| 2 4 | 3.3.2 Peripheral Control Register                            |     |

| 5.4 | Peripheral Setting Control Registers                         |     |

|     | 3.4.1 Peripheral Setting Control Register (PER_SET_CNTL)     |     |

| эг  | 3.4.2 Peripheral Settings Control Register 1                 |     |

| 3.5 | Global and Block Enable Registers                            |     |

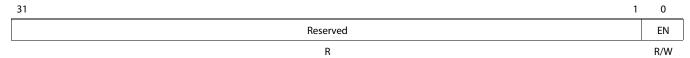

|     | 3.5.1 Global Enable Registers                                |     |

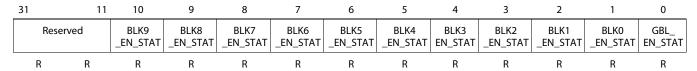

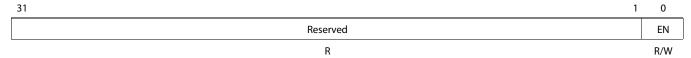

| 2.  | 3.5.2 Block Enable Registers (0-9)                           |     |

| 3.6 | ID Registers                                                 |     |

|     | 3.6.1 RapidIO MultiID Register 1                             |     |

| 2 7 | 3.6.2 RapidIO MultiID Register 2–8                           |     |

| 3./ | Hardware Packet Forwarding Registers                         | 3-5 |

Chapter 3

www.ti.com Contents

| 3.7.1 PF_16b_CNTL[0-7]                                                                                                                     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.7.2 PF_8b_CNTL[0-7]                                                                                                                      |      |

| 3.8 Interrupt Registers                                                                                                                    |      |

| 3.8.1 DOORBELLn Interrupt Condition Status Register (DOORBELL[0-3]_ICSR)                                                                   |      |

| 3.8.2 DOORBELLn Interrupt Condition Clear Register (DOORBELL[0-3]_ICCR)                                                                    |      |

| 3.8.3 LSU0 Interrupt Status and Clear Register                                                                                             |      |

| 3.8.4 LSU1 Interrupt Status and Clear Register                                                                                             |      |

| 3.8.5 Error, Reset and Special Event Interrupt                                                                                             |      |

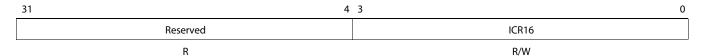

| 3.8.6 DOORBELLn Interrupt Condition Routing Registers (DOORBELLn_ICRR and DOORBELLn_ICRR2) 3.8.7 LSU Interrupt Condition Routing Registers |      |

| 3.8.8 Error, Reset, and Special Event Interrupt Condition Routing Registers                                                                |      |

| 3.8.9 Interrupt Control Register                                                                                                           |      |

| 3.8.9.1 Interrupt Status Decode Register                                                                                                   |      |

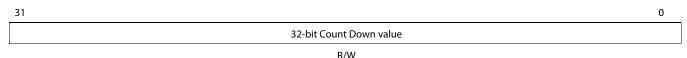

| 3.8.9.2 Interrupt Rate Counter Register                                                                                                    |      |

| 3.9 RXU Registers                                                                                                                          |      |

| 3.9.1 Type 11 Message Mapping Registers.                                                                                                   |      |

| 3.9.1.1 RIO_RXU_MAPxx_L                                                                                                                    |      |

| 3.9.1.2 RIO_RXU_MAPxx_H                                                                                                                    |      |

| 3.9.2 Type 9 Message Mapping Registers                                                                                                     |      |

| 3.9.2.1 RIO_RXU_TYPE9_MAPxx_0                                                                                                              |      |

| 3.9.2.2 RIO_RXU_TYPE9_MAPxx_1                                                                                                              |      |

| 3.9.2.3 RIO_RXU_TYPE9_MAPxx_2                                                                                                              |      |

| 3.9.3 Common Message Mapping Registers                                                                                                     | 3-68 |

| 3.9.3.1 RIO_RXU_MAPxx_QID                                                                                                                  | 3-68 |

| 3.10 LSU/MAU Registers                                                                                                                     | 3-69 |

| 3.10.1 LSUx_Reg0                                                                                                                           | 3-69 |

| 3.10.2 LSUx_Reg1                                                                                                                           |      |

| 3.10.3 LSUx_Reg2                                                                                                                           |      |

| 3.10.4 LSUx_Reg3                                                                                                                           |      |

| 3.10.5 LSUx_Reg4                                                                                                                           |      |

| 3.10.6 LSUx_Reg5                                                                                                                           |      |

| 3.10.7 LSUx_Reg6                                                                                                                           |      |

| 3.10.8 LSU_SETUP_REGO                                                                                                                      |      |

| 3.10.9 LSU_SETUP_REG1                                                                                                                      |      |

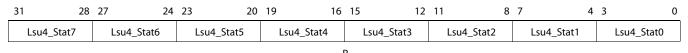

| 3.10.10 LSU_STAT_REGO                                                                                                                      |      |

| 3.10.11 LSU_STAT_REG1                                                                                                                      |      |

| 3.10.12 LSU_STAT_REG2                                                                                                                      |      |

| 3.10.13 LSU_STAT_REG3                                                                                                                      |      |

| 3.10.14 LSU_STAT_REG4                                                                                                                      |      |

| 3.10.15 LSU_STAT_REG5                                                                                                                      |      |

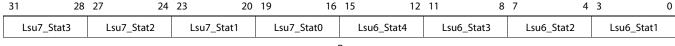

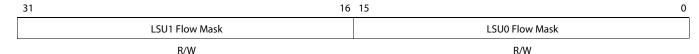

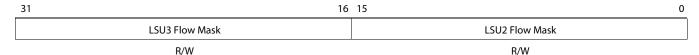

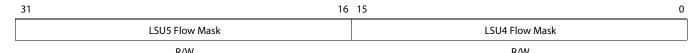

| 3.10.17 LSU_FLOW_MASKS1                                                                                                                    |      |

| 3.10.18 LSU_FLOW_MASKS2                                                                                                                    |      |

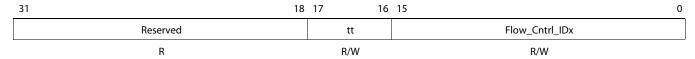

| 3.10.19 LSU_FLOW_MASKS3                                                                                                                    |      |

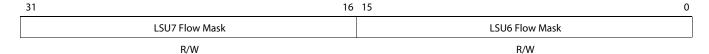

| 3.10.20 SUPRVSR_ID (MAU)                                                                                                                   |      |

| 3.11 Flow Control Registers                                                                                                                |      |

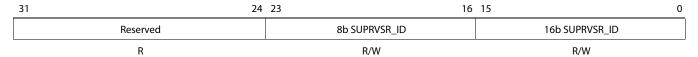

| 3.11.1 FLOW CONTLX                                                                                                                         |      |

| 3.12 TXU Registers                                                                                                                         |      |

| 3.12.1 TX_CPPI_FLOW_MASKSx                                                                                                                 |      |

| 3.12.2 TX_QUEUE_SCH_INFOx                                                                                                                  |      |

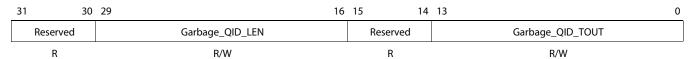

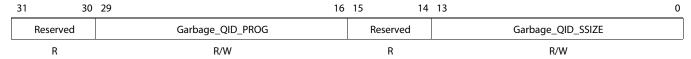

| 3.12.3 Garbage_Coll_QID0.                                                                                                                  |      |

| 3.12.4 Garbage_Coll_QID1                                                                                                                   |      |

| 3.12.5 Garbage_Coll_QID2.                                                                                                                  |      |

| 3.13 PKTDMA Registers                                                                                                                      |      |

| 3.14 CSR/CAR Registers                                                                                                                     |      |

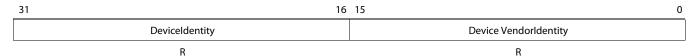

| 3.14.1 DEV_ID                                                                                                                              |      |

| 3.14.2 DEV_INFO                                                                                                                            |      |

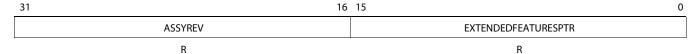

| 3.14.3 ASBLY_ID                                                                                                                            |      |

|                                                                                                                                            |      |

www.ti.com

| 3.14.4 ASBLY_INFO                                                                    |       |

|--------------------------------------------------------------------------------------|-------|

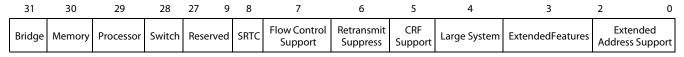

| 3.14.5 PE_FEAT                                                                       |       |

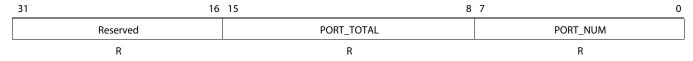

| 3.14.6 SW_PORT                                                                       |       |

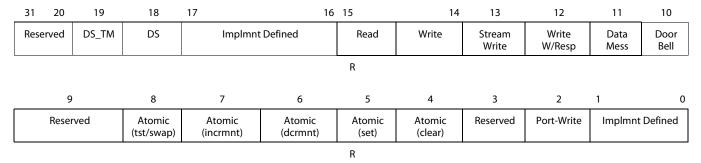

| 3.14.7 SRC_OP                                                                        |       |

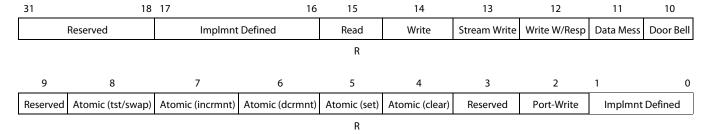

| 3.14.8 DEST_OP                                                                       |       |

| 3.14.9 DS_INFO                                                                       |       |

| 3.14.10 DS_LL_CTL                                                                    |       |

| 3.14.11 PE_LL_CTL                                                                    |       |

| 3.14.12 LCL_CFG_HBAR                                                                 |       |

| 3.14.13 LCL_CFG_BAR                                                                  |       |

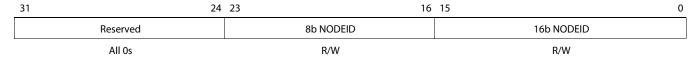

| 3.14.14 BASE_ID                                                                      |       |

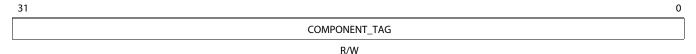

| 3.14.16 COMP_TAG                                                                     |       |

| 3.14.17 SP_MB_HEAD                                                                   |       |

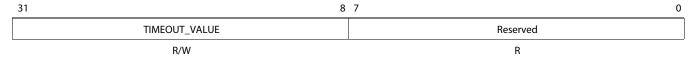

| 3.14.18 SP_LT_CTL                                                                    |       |

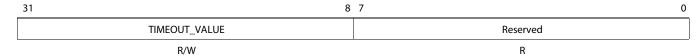

| 3.14.19 SP_RT_CTL                                                                    |       |

| 3.14.20 SP_GEN_CTL                                                                   |       |

| 3.14.21 SPn_LM_REQ                                                                   |       |

| 3.14.22 SPn_LM_RESP                                                                  |       |

| 3.14.23 SPn_ACKID_STAT                                                               |       |

| 3.14.24 SP(n)_CTL2                                                                   |       |

| 3.14.25 SPn_ERR_STAT                                                                 |       |

| 3.14.26 SPn_CTL                                                                      |       |

| 3.15 Error Management Registers                                                      |       |

| 3.15.1 ERR_RPT_BH.                                                                   |       |

| 3.15.2 ERR_DET                                                                       |       |

| 3.15.3 ERR_EN                                                                        |       |

| 3.15.4 H_ADDR_CAPT                                                                   |       |

| 3.15.5 ADDR_CAPT                                                                     |       |

| 3.15.6 ID_CAPT                                                                       |       |

| 3.15.7 CTRL_CAPT                                                                     | 3-107 |

| 3.15.8 PW_TGT_ID                                                                     | 3-108 |

| 3.15.9 SPx_ERR_DET                                                                   | 3-108 |

| 3.15.10 SPx_RATE_EN                                                                  | 3-110 |

| 3.15.11 SPx_ERR_ATTR_CAPT_DBG0                                                       |       |

| 3.15.12 SPx_ERR_CAPT_0_DBG1                                                          |       |

| 3.15.13 SPx_ERR_CAPT_1_DBG2                                                          |       |

| 3.15.14 SPx_ERR_CAPT_2_DBG3                                                          |       |

| 3.15.15 SPx_ERR_CAPT_3_DBG4                                                          |       |

| 3.15.16 SPx_ERR_RATE                                                                 |       |

| 3.15.17 SPx_ERR_THRESH                                                               |       |

| 3.16 Extended Features Block                                                         |       |

| 3.16.1 LANEn_STATO                                                                   |       |

| 3.16.2 LANEn Status 1 CSR (LANE n_STAT1).                                            |       |

| 3.17 Physical Layer Implementation Specific Registers                                |       |

| 3.17.1 PLM IDT-Specific Block Header Register (PLM_BH)                               |       |

| 3.17.2 PLM Port(n) Implementation Specific Control Register (PLM_SP(n)_IMP_SPEC_CTL) |       |

| 3.17.3 PLM Port Powerdown Control Register (PLM_SP(n)_PWDN_CTL)                      |       |

| 3.17.4 PLM Port(n) Event Status Register(PLM_SP(n)_Status)                           |       |

| 3.17.5 PLM Port(n) Interrupt Enable Register (PLM_SP(n)_INT_ENABLE)                  |       |

| 3.17.6 PLM Port(n) Port-Write Enable Register (PLM_SP(n)_PW_ENABLE)                  |       |

| 3.17.7 PLM Port(n) Event Generate Register (PLM_SP(n)_EVENT_GEN)                     |       |

| 3.17.8 PLM Port(n) All Interrupts Enable Register (PLM_SP(n)_ALL_INT_EN)             |       |

| 3.17.9 PLM Port(n) All Port-Writes Enable Register (PLM_SP(n)_ALL_PW_EN)             |       |

| 3.17.10 PLM Port(n) Path Control Register (PLM_SP(n)_PATH_CTL)                       |       |

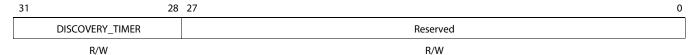

| 3.17.11 PLM Port(n) Discovery Timer Register (PLM_SP(n)_DISCOVERY_TIMER)             |       |

| 3.17.12 Port (n) Silence Timer                                                       |       |

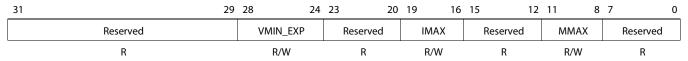

| 3.17.13 FLIVI FUIT(II) VIIIIII EXPUHEIIT NEGISTEI (FLIVI_3P(II)_VIVIIIV_EAP)         | 5-125 |

www.ti.com Contents

| 3.17.14  | PLM Port(n) Lane Polarity Control Register (PLM_SP(n)_POL_CTL)                                                         | 3-126 |

|----------|------------------------------------------------------------------------------------------------------------------------|-------|

| 3.17.15  | PLM Port(n) Packet Denial Control Register (PLM_SP(n)_DENIAL_CTL)                                                      | 3-127 |

| 3.17.16  | PLM Port(n) Received MECS Status Register (PLM_SP(n)_RCVD_MECS)                                                        | 3-127 |

| 3.17.17  | PLM Port(n) MECS Forwarding Register (PLM_SP(n)_MECS_FWD)                                                              | 3-128 |

| 3.17.18  | PLM Port(n) Control Symbol Transmit 1 (PLM_SP(n)_LONG_CS_TX1)                                                          | 3-128 |

| 3.17.19  | PLM Port(n) Control Symbol Transmit 2 (PLM_SP(n)_LONG_CS_TX2)                                                          | 3-129 |

| 3.17.20  | Transport Layer Block Header Register (TLM_BH)                                                                         | 3-129 |

| 3.17.21  | TLM Port(n) Control Register (TLM_SP(n)_CONTROL)                                                                       | 3-130 |

|          | TLM Port(n) Status Register (TLM_SP(n)_STATUS)                                                                         |       |

|          | TLM Port(n) Interrupt Enable Register (TLM_SP(n)_INT_ENABLE)                                                           |       |

|          | TLM Port(n) Port-Write Enable Register (TLM_SP(n)_PW_ENABLE)                                                           |       |

|          | TLM Port(n) Event Generate Register (TLM_SP(n)_EVENT_GEN)                                                              |       |

|          | TLM Port(n) Base Routing Register 0 Control Register (TLM_SP(n)_BRR_0_CTL)                                             |       |

|          | TLM Port(n) Base Routing Register 0 Pattern & Match Register                                                           |       |

|          | (TLM_SP(n)_BRR_O_PATTERN_MATCH)                                                                                        | 3-133 |

| 3.17.28  | TLM Port(n) Base Routing Register 1 Control Register (TLM_SP(n)_BRR_1_CTL)                                             |       |

|          | TLM Port(n) Base Routing Register 1 Pattern & Match Register                                                           |       |

|          | (TLM_SP(n)_BRR_1_PATTERN_MATCH)                                                                                        | 3-134 |

| 3.17.30  | TLM Port(n) Base Routing Register 2 Control Register (TLM_SP(n)_BRR_2_CTL)                                             |       |

|          | TLM Port(n) Base Routing Register 2 Pattern & Match Register                                                           |       |

|          | (TLM_SP(n)_BRR_2_PATTERN_MATCH)                                                                                        | 3-135 |

| 3.17.32  | TLM Port(n) Base Routing Register 3 Control Register (TLM_SP(n)_BRR_3_CTL)                                             |       |

|          | TLM Port(n) Base Routing Register 3 Pattern & Match Register                                                           |       |

|          | (TLM_SP(n)_BRR_3_PATTERN_MATCH)                                                                                        | 3-136 |

| 3.17.34  | Packet Buffer Module Block Header Register (PBM_BH)                                                                    |       |

|          | PBM Port(n) Control Register (PBM_SP(n)_CONTROL)                                                                       |       |

|          | PBM Port(n) Status Register (PBM_SP(n)_STATUS)                                                                         |       |

|          | PBM Port(n) Interrupt Enable Register (PBM_SP(n)_INT_ENABLE)                                                           |       |

|          | PBM Port(n) Port-Write Enable Register (PBM_SP(n)_Port-Write_ENABLE)                                                   |       |

|          | PBM Port(n) Event Generate Register (PBM_SP(n)_EVENT_GEN)                                                              |       |

|          | PBM Port(n) Ingress Resources Register (PBM_SP(n)_IG_RESOURCES)                                                        |       |

|          | PBM Port(n) Egress Resources Register (PBM_SP(n)_EG_RESOURCES)                                                         |       |

|          | PBM Port(n) Ingress Watermarks 0 Register (PBM_SP(n)_IG_WATERMARK0)                                                    |       |

|          | PBM Port(n) Ingress Watermarks 1 Register (PBM_SP(n)_IG_WATERMARK1)                                                    |       |

|          | PBM Port(n) Ingress Watermarks 2 Register (PBM_SP(n)_IG_WATERMARK2)                                                    |       |

|          | PBM Port(n) Ingress Watermarks 3 Register (PBM_SP(n)_IG_WATERMARK3)                                                    |       |

|          | IDT-Specific Event Management Block Header (EM_BH)                                                                     |       |

|          | Event Management Interrupt Status Register (EM_INT_STAT)                                                               |       |

|          | Event Management Interrupts Enable Register (EM_INT_ENABLE)                                                            |       |

|          | Event Management Interrupts Eriable Register (EM_INT_ENABLE)                                                           |       |

|          | Event Management Port-Write Status Register (EM_PW_STAT)                                                               |       |

|          | Event Management Port-Write Enable Register (EM_PW_ENABLE)                                                             |       |

|          | Event Management Port-Write Port Status Register (EM_PW_PORT_STAT)                                                     |       |

|          | Event Management Device Interrupt Enable Register (EM_DEV_INT_EN)                                                      |       |

|          | Event Management Device Interrupt Enable Register (EM_DEV_INT_EN)                                                      |       |

|          | Event Management MECS Status Register (EM_MECS_STAT)                                                                   |       |

|          | Event Management MECS Status Register (EM_MECS_STAT)  Event Management MECS Interrupt Enable Register (EM_MECS_INT_EN) |       |

|          |                                                                                                                        |       |

|          | Event Management MECS Capture Out Register (EM_MECS_CAP_EN)                                                            |       |

|          |                                                                                                                        |       |

|          | Event Management MECS Request Register (EM_MECS_REQ)                                                                   |       |

|          |                                                                                                                        |       |

|          | Event Management MECS Event Generate Register (EM_MECS_EVENT_GEN)                                                      |       |

|          | Event Management Reset Request Interrupt Feable Register (EM_RST_PORT_STAT)                                            |       |

|          | Event Management Reset Request Interrupt Enable Register (EM_RST_INT_EN)                                               |       |

|          | Event Management Reset Request Port-Write Enable Register (EM_RST_PW_EN)                                               |       |

|          | IDT-Specific Port-Write Block Header (PW_BH)                                                                           |       |

|          | Port-Write Control Register (PW_CTL)                                                                                   |       |

|          | Port-Write Routing Register (PW_ROUTE)                                                                                 |       |

| า เ / กห | FULL-WHILE DECEDIBION STATUS CONTROL FAN AND AND AND AND AND AND AND AND AND A                                         | コーココノ |

|            |                                                                                    | www.ti.com |

|------------|------------------------------------------------------------------------------------|------------|

|            | 3.17.69 Port-Write Reception Event Generate Register (PW_RX_EVENT_GEN)             | 3-152      |

|            | 3.17.70 Port-Write Reception Capture(n) CSR (PW_RX_CAPT(n))                        | 3-153      |

|            | 3.17.71 IDT-Specific LLM Module Block Header (LLM_BH)                              | 3-153      |

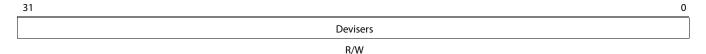

|            | 3.17.72 Whiteboard CSR (WHITEBOARD)                                                |            |

|            | 3.17.73 Port Number CSR (PORT_NUMBER)                                              |            |

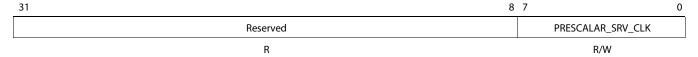

|            | 3.17.74 Port IP Prescalar for SRV_CLK Register (PRESCALAR_SRV_CLK)                 | 3-155      |

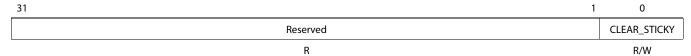

|            | 3.17.75 Register Reset Control CSR (REG_RST_CTL)                                   |            |

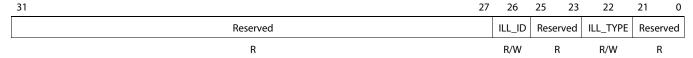

|            | 3.17.76 Local Logical/Transport Layer Error Detect CSR (LOCAL_ERR_DET)             | 3-156      |

|            | 3.17.77 Local Logical/Transport Layer Error Enable CSR (LOCAL_ERR_EN)              |            |

|            | 3.17.78 Local Logical/Transport Layer High Address Capture CSR (LOCAL_H_ADDR_CAPT) | 3-157      |

|            | 3.17.79 Local Logical/Transport Layer Address Capture CSR (LOCAL_ADDR_CAPT)        |            |

|            | 3.17.80 Local Logical/Transport Layer deviceID Capture CSR (LOCAL_ID_CAPT)         |            |

|            | 3.17.81 Local Logical/Transport Layer Control Capture CSR (LOCAL_CTRL_CAPT)        |            |

|            | 3.17.82 IDT-Specific Fabric Module Block Header (FABRIC_BH)                        | 3-159      |

|            | 3.17.83 Fabric Control and Status Register (FABRIC_CSR)                            |            |

|            | 3.17.84 Port(n) Fabric Status Register (SP(n)_FABRIC_STATUS)                       |            |

| Appendix A |                                                                                    |            |

|            | Examples                                                                           | A-1        |

|            | A.1 Channel Operations                                                             | A-2        |

|            | A.2 Queue Operations                                                               |            |

|            | 7.2 Queue operations                                                               |            |

|            | Index                                                                              | IX-1       |

#### **List of Tables**

www.ti.com

| T 11 24    |                                                                                           | 2.2  |

|------------|-------------------------------------------------------------------------------------------|------|

| Table 2-1  | Registers Checked for DeviceID                                                            |      |

| Table 2-2  | Packet Types                                                                              |      |

| Table 2-3  | Pin Description                                                                           |      |

| Table 2-4  | SerDes Lane Configurations for Various Port Widths                                        |      |

| Table 2-5  | Control/Command Register Field Description                                                |      |

| Table 2-6  | Status Register Field Descriptions Read Only View                                         |      |

| Table 2-7  | Status Register Field Descriptions Write Only View.                                       |      |

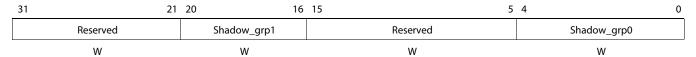

| Table 2-8  | Shadow Register Combinations                                                              |      |

| Table 2-9  | RIO_LSU_SETUP_REG0 (WO View) Field Descriptions                                           |      |

| Table 2-10 | RIO_LSU_SETUP_REGO (RO View) Field Descriptions                                           |      |

| Table 2-11 | Maximum LTID per LSU                                                                      |      |

| Table 2-12 | LSU_STATUS (LSUx_STAT)                                                                    |      |

| Table 2-13 | RIO_LSU_STAT_REG0-6 & RIO_LSU_STAT_REG3-5                                                 |      |

| Table 2-14 | RIO_LSU_SETUP_REG1 Field Descriptions                                                     |      |

| Table 2-15 | RX RapidIO Protocol Specific Packet Descriptor Fields (Type 11)                           |      |

| Table 2-16 | RX RapidIO Protocol Specific Packet Descriptor Fields (Type 9)                            |      |

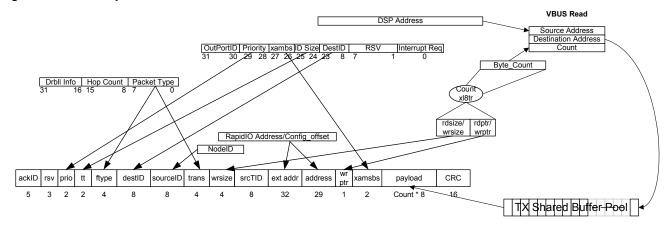

| Table 2-17 | TX RapidIO Protocol Specific Packet descriptor Field Definitions                          |      |

| Table 2-18 | TX RapidIO Protocol Specific Packet descriptor Field Definitions                          |      |

| Table 2-19 | Flow Control Table Entry Registers (Address offset 0x07D0 — 0x080C)                       |      |

| Table 2-20 | Transmit Source Flow Control Masks                                                        |      |

| Table 2-21 | Reset Hierarchy                                                                           |      |

| Table 2-22 | Dest ID Checking for Multicast Operations                                                 |      |

| Table 2-23 | RapidIO Packet Types                                                                      |      |

| Table 2-24 | RapidIO Packet Type Behaviors                                                             | 2-74 |

| Table 2-25 | Hardware Packet Forwarding Mapping Entries Register Fields                                |      |

| Table 2-26 | Hardware Packet Forwarding Mapping Entries Register Field                                 |      |

| Table 2-27 | Error Case Handling                                                                       | 2-77 |

| Table 3-1  | SRIO Register Offsets                                                                     | 3-1  |

| Table 3-2  | SRIO Registers                                                                            | 3-2  |

| Table 3-3  | SerDes Macro Status Register (SRIO_SERDES_STS — 0x02620154) Field Description             | 3-31 |

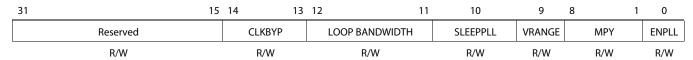

| Table 3-4  | SerDes Macro Configuration Register (SRIO_SERDES_CFGPLL — 0x02620360) Field Description   | 3-32 |

| Table 3-5  | Line Rate Versus PLL Output Clock Frequency                                               | 3-33 |

| Table 3-6  | Effect of the RATE Bits                                                                   | 3-33 |

| Table 3-7  | Frequency Range versus MPY Value                                                          | 3-34 |

| Table 3-8  | Clock Bypass                                                                              | 3-34 |

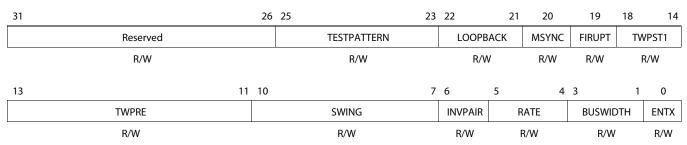

| Table 3-9  | SerDes Receive Channel Configuration Register (SRIO_SERDES_CFGRX[0-3]) Field Descriptions | 3-35 |

| Table 3-10 | EQ Bits                                                                                   | 3-37 |

| Table 3-11 | Loopback—cfgrxi[24-23]                                                                    | 3-37 |

| Table 3-12 | SerDes Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL) Field Descriptions  | 3-38 |

| Table 3-13 | SWING Bits—cfgtxi [10-7]                                                                  | 3-38 |

| Table 3-14 | Pre-cursor Transmit Tap Weights—cfgtxi [13-11]                                            | 3-39 |

| Table 3-15 | Post-cursor Transmit Tap Weights—cfgtxi [18-14]                                           | 3-39 |

| Table 3-16 | Loopback—cfgtxi [22-21]                                                                   | 3-40 |

| Table 3-17 | Peripheral ID Register (Address Offset 0x0000)                                            | 3-41 |

| Table 3-18 | Peripheral Control Register (Address offset 0x0004)                                       |      |

| Table 3-19 | Peripheral Settings Control Register (Address offset 0x0014)                              |      |

| Table 3-20 | PER_SET_CNTL1 (Address offset 0x0018)                                                     |      |

| Table 3-21 | EN/EN_STAT Bit Field Descriptions                                                         |      |

| Table 3-22 | RapidIO MultiID Register 1 (Address offset 0x00A0)                                        |      |

| Table 3-23 | RapidIO MultiID Register 2 – 8 (Address offset 0x00A4)                                    |      |

| Table 3-24 | PF_16b_CNTL[0-7]                                                                          |      |

| Table 3-25 | PF_8b_CNTL[0-7].                                                                          |      |

|            |                                                                                           |      |

| LIST OF TADIES | www.ti.com |

|----------------|------------|

|                |            |

|            |                                                                                       | www.ti.com |

|------------|---------------------------------------------------------------------------------------|------------|

| Table 3-26 | Doorbell n Interrupt Condition Status Register Field Descriptions                     |            |

| Table 3-27 | Doorbell n Interrupt Condition Clear Register Field Descriptions                      |            |

| Table 3-28 | Interrupt Clearing Sequence for Special Event Interrupts                              |            |

| Table 3-29 | Doorbell n Interrupt Condition Routing Register Field Descriptions                    |            |

| Table 3-30 | LSU n Interrupt Condition Routing Register Field Descriptions                         |            |

| Table 3-31 | INTERRUPT_CTL                                                                         |            |

| Table 3-32 | Interrupt Condition Routing Options for General Purpose Interrupts                    | 3-61       |

| Table 3-33 | Interrupt Condition Routing Options for Dedicated Doorbell Interrupts Only            | 3-61       |

| Table 3-34 | ISDRn Register                                                                        |            |

| Table 3-35 | RIO_RXU_MAPxx_L                                                                       | 3-65       |

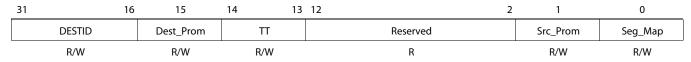

| Table 3-36 | RIO_RXU_MAPxx_H Field Descriptions                                                    | 3-66       |

| Table 3-37 | RIO_RXU_TYPE9_MAPxx_0 Field Descriptions                                              | 3-66       |

| Table 3-38 | RIO_RXU_TYPE9_MAPxx_1 Field Descriptions                                              | 3-67       |

| Table 3-39 | RIO_RXU_Type9_MAPxx_2 Field Descriptions                                              | 3-67       |

| Table 3-40 | RIO_RXU_MAPxx_QID Field Descriptions                                                  | 3-68       |

| Table 3-41 | LSUx_Reg0 Field Descriptions                                                          |            |

| Table 3-42 | LSUx_Reg1 Field Descriptions                                                          |            |

| Table 3-43 | LSUx_Reg2 Field Descriptions                                                          |            |

| Table 3-44 | LSU_Reg3 Field Descriptions                                                           | 3-70       |

| Table 3-45 | LSU_Reg4 Field Descriptions                                                           | 3-71       |

| Table 3-46 | LSU_Reg5 Field Descriptions                                                           | 3-72       |

| Table 3-47 | LSU_Reg6 (RO) Field Descriptions                                                      | 3-72       |

| Table 3-48 | LSU_Reg6 (WO) Field Descriptions                                                      | 3-73       |

| Table 3-49 | LSU_SETUP_REG0 (RO) Field Descriptions                                                | 3-73       |