# **AM263x ADC PSPICE Models**

2023-11-08

# **Summary**

- Assembled PSPICE based models of the AM263x SAR ADC

- Parasitics based on datasheet typical values

- Models can be used to test attached op-amp and RC charge-bucket filter circuit performance to minimize sampling error

- Various sample-rate, acquisition and hold timings can be setup

- Single-ended model available now, can be extended to differential mode model

- PSPICE models assembled using the Cadence PSPICE for TI toolset

- See: <a href="https://www.ti.com/tool/PSPICE-FOR-TI">https://www.ti.com/tool/PSPICE-FOR-TI</a>

- Comprehensive SAR ADC circuit selection guide (applicable to AM263x devices) is available here:

- https://www.ti.com/lit/an/spract6a/spract6a.pdf

- Written with TINA-TI SPICE simulator in mind, but the concepts are all applicable

# **Model Description**

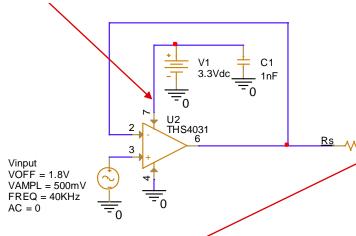

#### **AC Source**

- Typical op-amp driver circuit should be replaced with whatever driver is present in target system

- Should output signal range compatible with datasheet voltage limits

## Package Capacitance

330pF

Typical value within datasheet input parasitics tolerances

### **ADC Hold Capacitance**

- Typical value within datasheet input tolerances

- Acquisition logic samples this voltage during conversion

## **ADC Discharge Switch**

Modeling discharge timing for Chold

S\_Discharge

VON = 1.0V

V Discharge

V1 = 0 V2 = 1.2V

TD = 248nS

TR = 100p

TF = 100p

PW = 2nS

PER = 250nS

VOFF = 0.0V

Rdischarge

0.001

Ideal switch – near zero leakage

## RC Charge-Bucket Circuit

- Providing local store of charge for sample phase

- · Charge current limiting

- Usually not anti-alias bandwidth limiting

## **ADC Discharge Switch**

- Modeling sample/hold timing for Chold

- Ideal switch near zero leakage

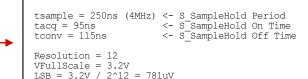

## **ADC Config Info**

Used to inform expected settling noise targets

V1 = 0 < V2 = 1.2V

TR = 100p

TF = 100p

PW = 95nS

PER = 250nS

TD = 0

Settling target = 1/2 LSBs = 390uV

**ADC On Resistance**

AM263x SAR ADC Input Model

Ron AAA

Cpkg

$\frac{1}{2}$  7pF

Typical value within datasheet

input parasitics tolerances

Rhold

S\_SampleHold

VON = 1.0V

V SampleHold

VOFF = 0.0V

0.001

Chold

8pF

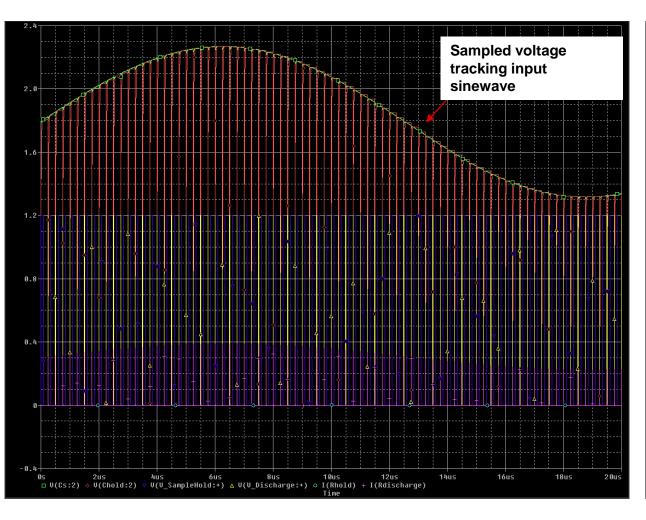

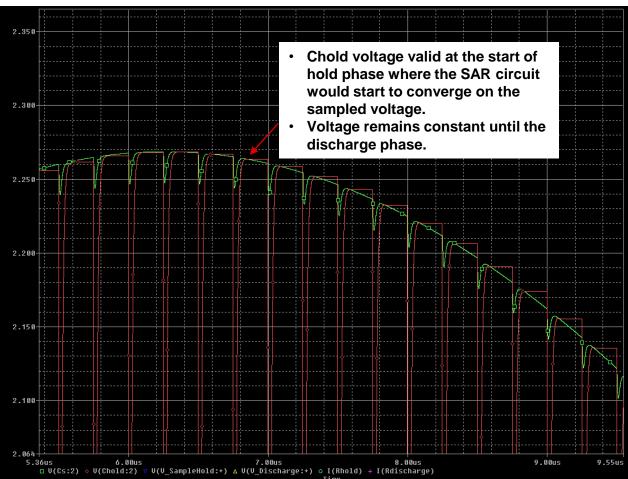

# **Model Output Example**

# **Model Output Example**

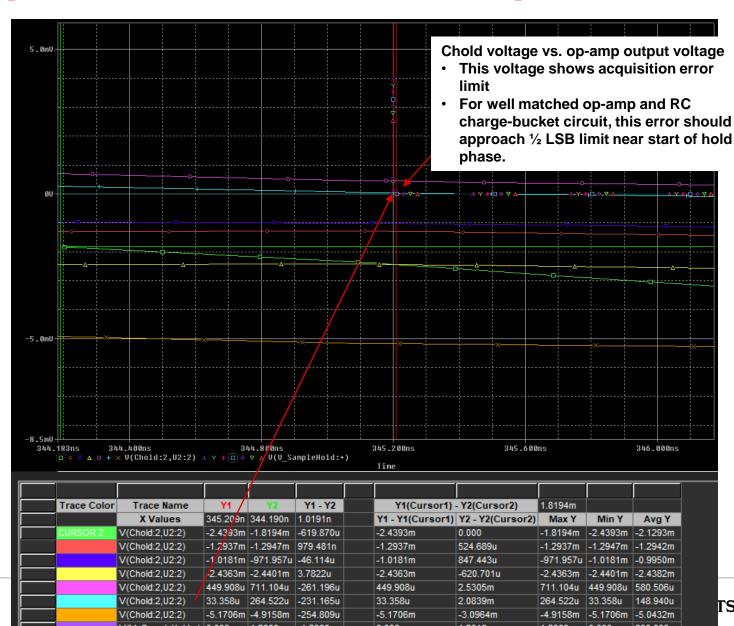

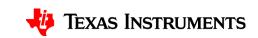

- Simulated ADC settling error can be evaluated by measuring the difference in voltage from op-amp output to the Chold capacitor after the sample and hold switch has opened.

- This would be the beginning of the conversion phase

- In the example shown, the settled acquisition error is show to be close to 1mV (no RC charge-bucket circuit optimizations were made)

- If further reduction in settled error is needed a parametric sweep of Rs and Cs values van be run

# **Model Output Example – Parametric Sweep**

- For best value sweep starting points See SAR ADC circuit selection guide (applicable to AM263x devices) available here:

- https://www.ti.com/lit/an/spra ct6a/spract6a.pdf

- Keeping Cs constant at 200pF and sweeping across Rs values from 1mOhm to 100Ohm

- Rs = 80 minimized error after sample and hold switch closed to less than 33uV

- Specific RC values are dependent on op-amp driver and timing selected since both with change the settling behavior during sample phase