# TMS570LC4357: What is the correct mechanism to use when receiving a data stream of unknown size bursts on an SCI link?

<u>Intellectual</u> 1790 points Texas Instruments

Part Number: TMS570LC4357

Hi Team,

I am contacting you because my customers have a problem with the use of the DMA on the TMS570LC4357 processor.

In our use case, they want to receive a serial data stream using the SCI component and transfer the data to RAM in masked time with DMA.

To do this, they program a transfer to a buffer in RAM with auto-initiation activated, and on the software side they empty the buffer like a circular buffer.

<u>To know where the DMA is, they consult the Current Destination Address Register (CDADDR), but the value of the register does not seem to be updated systematically.</u>

# Highlight of the bug:

To highlight this, they used 2 buffers, the DMA switches from one buffer to the other when it reaches the end (via a BTC interrupt, they write a new control packet to point to the next buffer). they set a frame size of one byte and activate the FTC interrupt to know if a transfer has taken place or not.

What they observe is that when the DMA changes buffer and a transfer has taken place in the new buffer (validated via the FTC interrupt and the new data is in RAM), the CDADDR register always points to the end of the previous buffer. Worse, it can point to an old address during 2 or 3 FTC interrupts.

## back to their use case:

In their operational case (with a buffer and auto-initiation), they have data bursts arriving on the serial. What they observe is that at the end of the burst, CDADDR points to the second last byte received and that is still the case, even several tens of milliseconds later. The CDADDR register will only be updated when the next burst starts to arrive.

About this register, the documentation (SPNU563A - March 2018) says: "These bits are only updated after a channel is arbitrated out of the priority queue."

This is not extremely clear and suggests that it is not possible to use the CDADDR register to track reception as it happens, since it is only updated on non-predictable events.

So my question is, what is the correct mechanism to use when receiving a data stream of unknown size bursts on an SCI link?

Regards,

Geoffrey

9 months ago

jagadish gundavarapu 192.163.5.9 <u>9 months ago</u> Hi Geoffrey, TI\_Mastermind 35305 points

Geoffrey Ficara said:

So my question is, what is the correct mechanism to use when receiving a data stream of unknown size bursts on an SCI link?

The SCI doesn't support any character time out interrupt. So, SCI with DMA could not change the packet size dynamically.

So, you have to implement some protocol in application level, like the transmitter should needs to tell the receiver about the packet size it is going to send(this packet length is fixed), and receiver can change the DMA packet settings for the new packet size. In this way you can receive variable size of data using UART with DMA. Once it receives unknown length packet again it should need to change DMA packet settings to the known length packet to receive next unknown length of the packet and should continue the process.

Thanks & regards, Jagadish.

Geoffrey Ficara 192.91.60.14 9 months ago in reply to jagadish gundavarapu Hi Jagadish,

TI\_Intellectual 1790 points

Buffer en ran AIBICIDIEIFIG

I don't think I understood your way, can you elaborate?

Here is the description of the problem, at the end of a received burst, the CDADDR register doesn't point to the last value received, but to the one before. So I don't know the last value of a burst until the next burst arrives.

How does you wau solve this issue?

Regards

Geoffrey

Geoffrey Ficara 192.91.60.14 9 months ago in reply to Geoffrey Ficara Hi.

TI\_Intellectual 1790 points

Any info?

Geoffrey

TI\_Mastermind 35305 points jagadish gundavarapu 192.163.5.9 <u>8 months ago</u> in reply to <u>Geoffrey Ficara</u> Hi Geoffrey,

## Geoffrey Ficara said:

Here is the description of the problem, at the end of a received burst, the CDADDR register doesn't point to the last value received, but to the one before

(+) TMS570LC4357: What is the correct mechanism to use when receiving a data stream of unknown size bursts on an SCI link? -...

The CDADDR register will not provide valid address of the last received value, this is because the CDADDR register value will get updated only when arbitration condition occurs.

## For example:

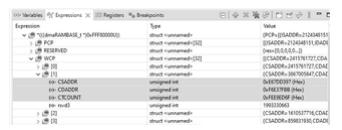

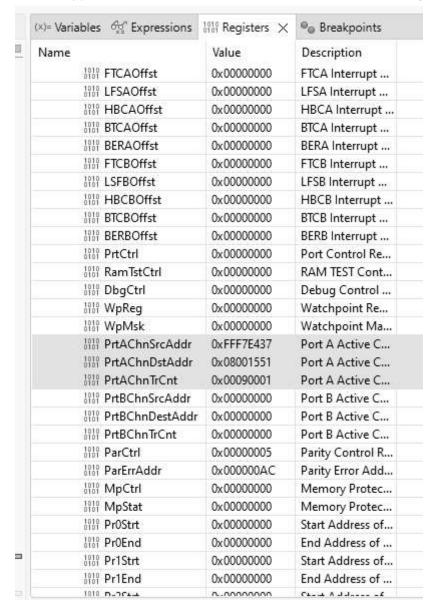

If one channel trigger comes then DMA will initialize corresponding channel primary control packet information to the

either port A or port B registers, now DMA will move data and changes this port A registers for each element it shifts. If any high priority DMA channel triggered in between this process then this Port registers current configuration will get moved into the Working control packet at its arbitration, so that now DMA can move new channel primary control packet information to the Port registers.

Now after completion of this high priority channel execution by DMA, then DMA will again get the working control packet information of previous channel and it copies that into the port registers to resume the previous operation.

So, because of this reason i won't recommend customer to use the CDADDR register for to get unknown bytes shifted by DMA.

--

Thanks & regards, Jagadish.

<u>jagadish gundavarapu</u> 192.163.5.9 <u>8 months ago</u> in reply to <u>jagadish gundavarapu</u>TI\_Mastermind 35305 points Hi Geoffrey,

So, my suggestion here is that

Ask customer to use Active port registers or FIFO registers i mentioned.

Thanks & regards, Jagadish.

<u>Geoffrey Ficara</u> 192.91.60.15 <u>8 months ago</u> in reply to <u>jagadish gundavarapu</u> Hi Jagadish, TI\_Intellectual 1790 points

Thank you for the help. Can you just elaborate, how will active port registers or FIFO registers solve the problem?

Regards

Geoffrey

jagadish gundavarapu 192.163.5.9 8 months ago in reply to Geoffrey Ficara Tl\_Mastermind\_35305 points

Hi Geoffrey,

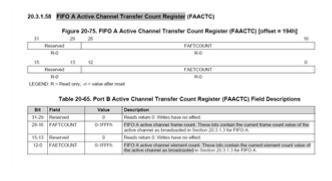

FIFO A Active Channel Transfer Count Register:

2/21/24, 5:50 PM (+) TMS570LC4357: What is the correct mechanism to use when receiving a data stream of unknown size bursts on an SCI link? -... This register value get decrement each time a element/frame transferred by DMA, so i guess the

customer can use this register value to calculate number of elements/frames transferred by DMA as he already has data of how many elements/frames he willing to transfer.

Thanks & regards, Jagadish.

| About TI        |  |  |  |

|-----------------|--|--|--|

| Quick links     |  |  |  |

| Buying          |  |  |  |

| Connect with us |  |  |  |

|                 |  |  |  |

Texas Instruments has been making progress possible for decades. We are a global semiconductor company that designs, manufactures, tests and sells analog and embedded processing chips. Our products help our customers efficiently manage power, accurately sense and transmit data and provide the core control or processing in their designs.

Accessibility Cookie policy Privacy policy Terms of sale Terms of use Trademarks

Website feedback

© Copyright 1995-2024 Texas Instruments Incorporated. All rights reserved.

**Previewing Staged Changes**