## TMS470R1x Platform Class II Serial Interface B (C2SIb) Reference Guide

April 2005

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and application s using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different form or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### Products Amplifiers Data Converters DSP

DSP Interface Logic Power Mgmt Microcontrollers amplifier.ti.com dataconverter.ti.com dsp.ti.com interface.ti.com logic.ti.com power.ti.com microcontroller.ti.com Applications

Audio Automotive Broadband Digital Control Military Optical Networking Security Telephony Video & Imaging Wireless www.ti.com/automotive www.ti.com/broadband www.ti.com/broadband www.ti.com/broadband www.ti.com/broadband www.ti.com/pticalnetwork www.ti.com/security www.ti.com/telephony

www.ti.com/video www.ti.com/wireless

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

(SPNU160)

#### **REVISION HISTORY**

REVISION

\*

**DATE** 9/04 AUTHOR

NOTES

R. Haley

Initial version

September 2004

# Figures

| 1  | C2SIb Pin Connection Diagram                              |

|----|-----------------------------------------------------------|

| 2  | C2SIb Block Diagram                                       |

| 3  | Simplest 1 Byte Message                                   |

| 4  | Typical C2SIb Data Frame Format Without In-Frame Response |

| 5  | Typical C2SIb Data Frame Format With In-Frame Response    |

| 6  | Byte Transmission                                         |

| 7  | Global Control Register 0 (C2SIGCRO)                      |

| 8  | Global Control Register 1 (C2SIGCR1) 31                   |

| 9  | Normalization Bit/Control Bit                             |

| 10 | Control Register (C2SIGCTR) 35                            |

| 11 | Interrupt Control Register (C2SIICR)                      |

| 12 | Interrupt Status Register (C2SIISR) 41                    |

| 13 | Global Status Register (C2SIGSR) 47                       |

| 14 | Completion Code Status Register (C2SIGSR) 49              |

| 15 | Peripheral Control Register (C2SIBRK) 54                  |

| 16 | Offset Register (C2SIOFFSET) 55                           |

| 17 | Transmit Data Buffer Register (C2SITDB) 56                |

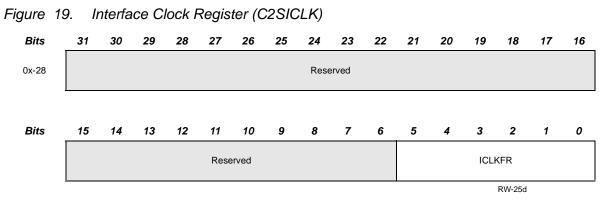

| 18 | Interface Clock Register (C2SICLK) 57                     |

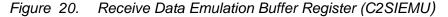

| 19 | Receive Data Emulation Buffer Register (C2SIEMU) 60       |

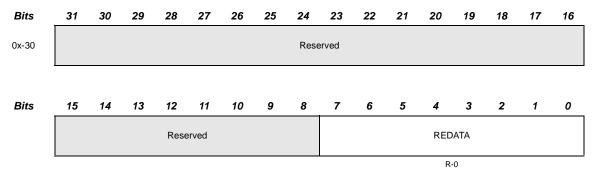

| 20 | Receive Data Buffer Register (C2SIRDB) 61                 |

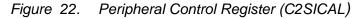

| 21 | Peripheral Control Register (C2SICAL) 62                  |

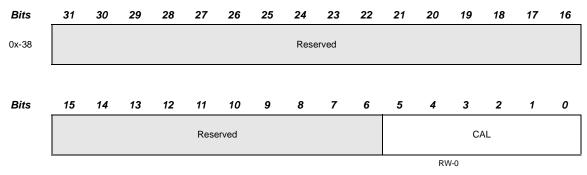

| 22 | Transmit Byte Counter Register (C2SIMTBC) 64              |

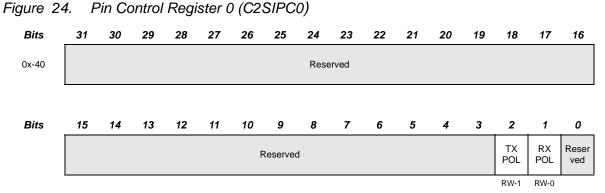

| 23 | Pin Control Register 0 (C2SIPC0) 66                       |

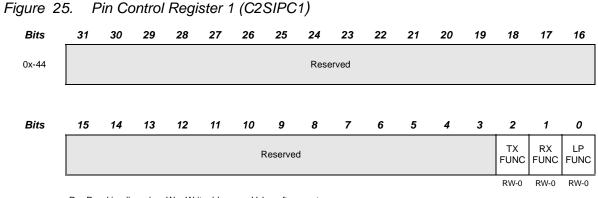

| 24 | Pin Control Register 1 (C2SIPC1)                          |

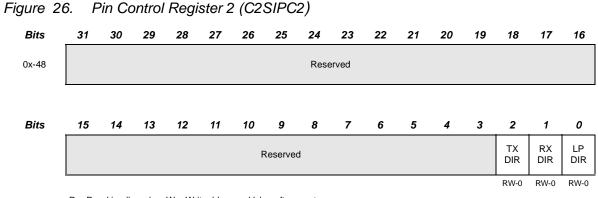

| 25 | Pin Control Register 2 (C2SIPC2) 69                       |

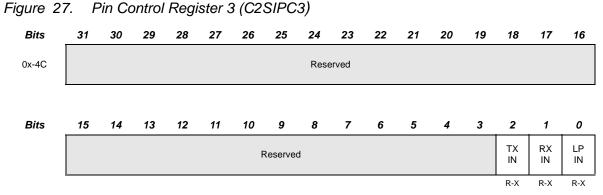

| 26 | Pin Control Register 3 (C2SIPC3)                          |

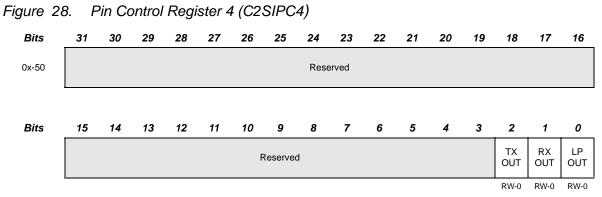

| 27 | Pin Control Register 4 (C2SIPC4)                          |

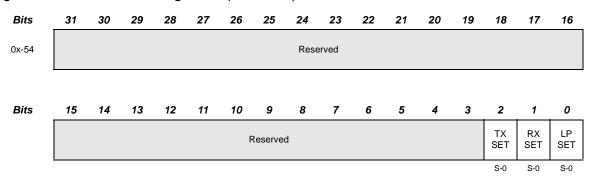

| 28 | Pin Control Register 5 (C2SIPC5)                          |

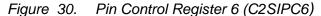

| 29 | Pin Control Register 6 (C2SIPC6)                          |

| 30 | Pin Control Register 7 (C2SIPC7)                          |

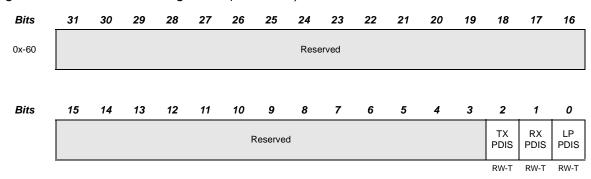

| 31 | Pin Control Register 8 (C2SIPC8) | 76 |

|----|----------------------------------|----|

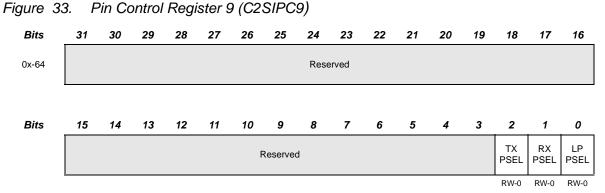

| 32 | Pin Control Register 9 (C2SIPC9) | 77 |

### **Tables**

| 1  | C2SIb Internal Registers 5                                          |

|----|---------------------------------------------------------------------|

| 2  | C2SIb Message Time Duration                                         |

| 3  | Interrupt Index Table                                               |

| 4  | Interrupt Bits and Associated Registers 22                          |

| 5  | Global Control Register 0 (C2SIGCRO) Field Descriptions             |

| 6  | Global Control Register 1 (C2SIGCR1) Field Descriptions 31          |

| 7  | Control Register (C2SICTR) Field Descriptions 35                    |

| 8  | Interrupt Control Register (C2SIICR) Field Descriptions             |

| 9  | Interrupt Status Register (C2SIISR) Field Descriptions 41           |

| 10 | Global Status Register (C2SIGSR) Field Descriptions 47              |

| 11 | Completion Code Status Register (C2SIGSR) Field Descriptions        |

| 12 | Completion Code Descriptions                                        |

| 13 | Peripheral Control Register (C2SIBRK) Field Descriptions            |

| 14 | Offset Register (C2SIOFFSET) Field Descriptions                     |

| 15 | Transmit Data Buffer Register (C2SITDB) Field Descriptions          |

| 16 | Interface Clock Register (C2SICLK) Field Descriptions               |

| 17 | Clock Frequencies and Values for the Interface Clock Register       |

| 18 | Receive Data Emulation Buffer Register (C2SIEMU) Field Descriptions |

| 19 | Receive Data Buffer Register (C2SIRDB) Field Descriptions           |

| 20 | Peripheral Control Register (C2SICAL) Field Descriptions            |

| 21 | Transmit Byte Counter Register (C2SIMTBC) Field Descriptions        |

| 22 | Pin Control Register 0(C2SIPC0) Field Descriptions                  |

| 23 | Pin Control Register 1 (C2SIPC1) Field Descriptions                 |

| 24 | Pin Control Register 2 (C2SIPC2) Field Descriptions                 |

| 25 | Pin Control Register 3 (C2SIPC3) Field Descriptions                 |

| 26 | Pin Control Register 4 (C2SIPC4) Field Descriptions                 |

| 27 | Pin Control Register 4 (C2SIPC4) Field Descriptions                 |

| 28 | Pin Control Register 6 (C2SIPC6) Field Descriptions                 |

|    |                                                                     |

| 29 | Pin Control Register 7 (C2SIPC7) Field Descriptions. | 75 |

|----|------------------------------------------------------|----|

| 30 | Pin Control Register 8 (C2SIPC8) Field Descriptions. | 76 |

| 31 | Pin Control Register 4 (C2SIPC4) Field Descriptions. | 77 |

## Contents

| 1 | Overv  | <i>r</i> iew                                        |

|---|--------|-----------------------------------------------------|

| 2 | Funct  | ional Description of the C2SIb                      |

|   | 2.1    | C2SIb Internal Registers                            |

| 3 | Data   | Format                                              |

|   | 3.1    | Start Of Frame (SOF)                                |

|   | 3.2    | Data Bits and IFR Bits (when an IFR is used)        |

|   | 3.3    | Cyclic Redundancy Check (CRC)9                      |

|   | 3.4    | End Of Data (EOD)9                                  |

|   | 3.5    | Normalization Bit.                                  |

|   | 3.6    | End Of Frame (EOF)9                                 |

|   | 3.7    | Break                                               |

| 4 | Trans  | mitting C2Slb Messages                              |

|   | 4.1    | Transmitting Non-IFR Messages                       |

|   | 4.2    | Transmitting IFR Messages                           |

|   | 4.3    | Transmitting BREAK Messages                         |

|   | 4.4    | Transmission Arbitration                            |

|   | 4.5    | Byte Boundary Loss of Arbitration when Transmitting |

|   | 4.6    | Bus Error Conditions                                |

|   |        | 4.6.1 Short-to-Voltage 17                           |

|   |        | 4.6.2 Short-to-Ground 17                            |

|   |        | 4.6.3 Open Bus 18                                   |

|   |        | 4.6.4Other Bus Errors Not Discussed18               |

| 5 | Recei  | iving C2SIb Messages                                |

|   | 5.1    | Receiving Normal Messages 19                        |

|   | 5.2    | Receiving IFR Messages 19                           |

|   | 5.3    | Receiving BREAK Messages 20                         |

|   | 5.4    | Receiving Digital Filters                           |

| 6 | Interr | upts                                                |

|   | 6.1    | Proper Handling of Events 21                        |

|   | 6.2    | Handling interrupt sources                          |

| 7 |        | ral Purpose I/O                                     |

| 8 |        | Interface                                           |

|   | 8.1    | DMA Transactions                                    |

|   | 8.2    | Non-DMA Transactions                                |

|   | 8.3    | TX Mode                                             |

|   | 8.4    | Low Power Mode                                      |

|   |        |                                                     |

|   | 8.5    | Emulation Mode                                      |

v

| 9  |        | Internal Registers                                 |

|----|--------|----------------------------------------------------|

|    | 9.1    | Global Control Register 0 (C2SIGCR0)               |

|    | 9.2    | Global Control Register 1 (C2SIGCR1)               |

|    | 9.3    | Control Register 1 (C2SICTR)                       |

|    | 9.4    | Interrupt Control Register (C2SIICR)               |

|    | 9.5    | Interrupt Status Register (C2SIISR)41              |

|    | 9.6    | Global Status Register (C2SIGSR)47                 |

|    | 9.7    | Completion Code Status Register (C2SICCSR)         |

|    | 9.8    | Peripheral Control Register (C2SIBRK)54            |

|    | 9.9    | Offset Register (OFFSET)55                         |

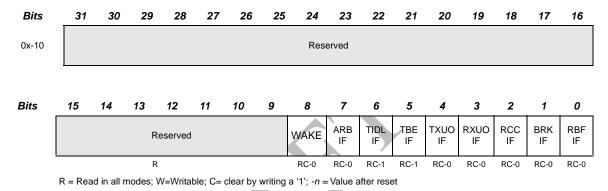

|    | 9.10   | Transmit Data Buffer Register (C2SITDB)56          |

|    | 9.11   | Interface Clock Register (C2SICLK)                 |

|    | 9.12   | Reserved Register                                  |

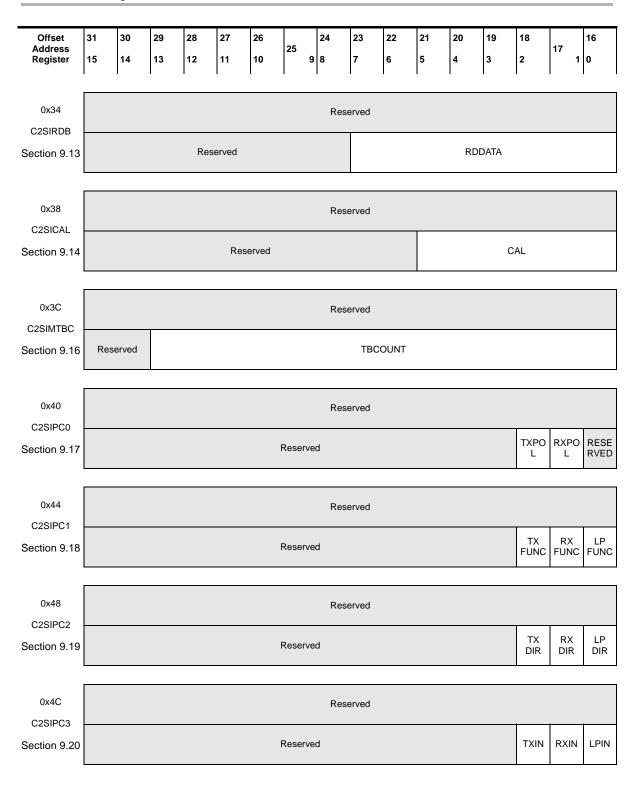

|    | 9.13   | Receive Data Emulation Buffer Register (C2SIEMU)60 |

|    | 9.14   | Receive Data Buffer Register (C2SIRDB)61           |

|    | 9.15   | Peripheral Control Register (C2SICAL)              |

|    | 9.16   | Transmit Byte Counter Register (C2SIMTBC)64        |

|    | 9.17   | Pin Control Register 0 (C2SIPC0)66                 |

|    | 9.18   | Pin Control Register 1 (C2SIPC1)67                 |

|    | 9.19   | Pin Control Register 2 (C2SIPC2)                   |

|    | 9.20   | Pin Control Register 3 (C2SIPC3)71                 |

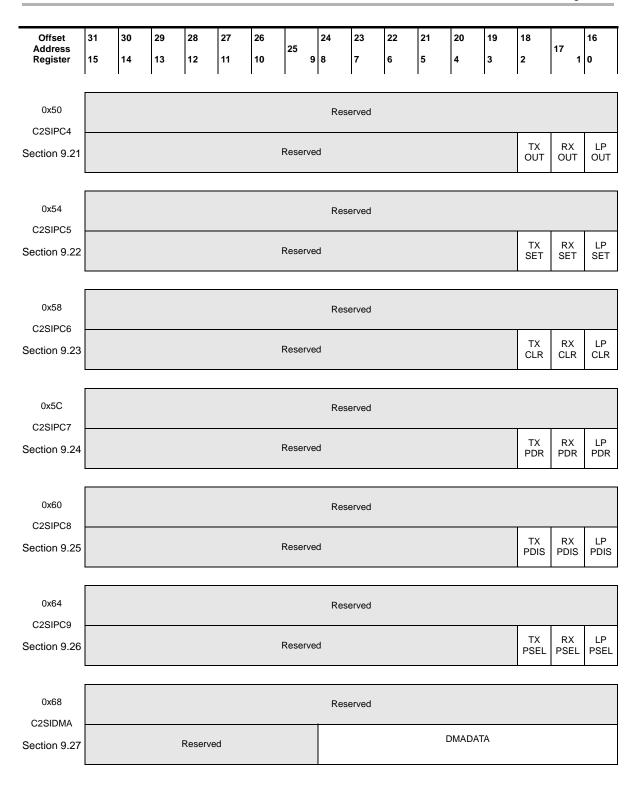

|    | 9.21   | Pin Control Register 4 (C2SIPC4)72                 |

|    | 9.22   | Pin Control Register 5 (C2SIPC5)73                 |

|    | 9.23   | Pin Control Register 6 (C2SIPC6)74                 |

|    | 9.24   | Pin Control Register 7 (C2SIPC7)75                 |

|    | 9.25   | Pin Control Register 8 (C2SIPC8)                   |

|    | 9.26   | Pin Control Register 9 (C2SIPC9)                   |

|    | 9.27   | DMA Read Register (C2SIRDMA)78                     |

| 10 | Timing | Examples                                           |

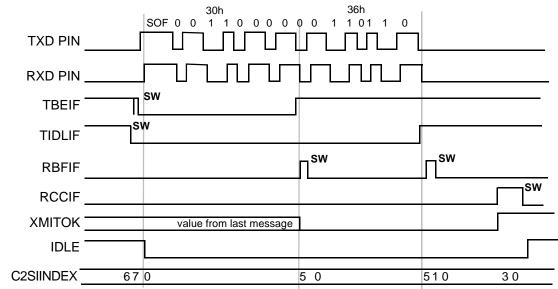

|    | 10.1   | Simple Transmit Example                            |

|    | 10.2   | Send Message and Receive IFR Example               |

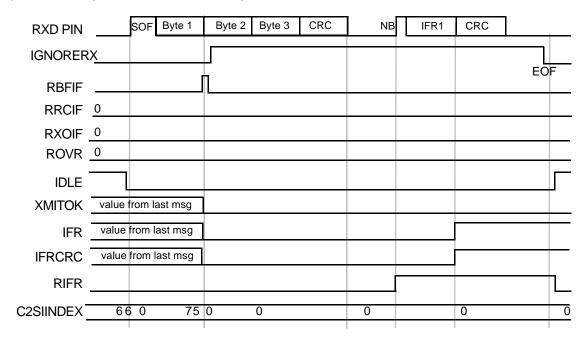

|    | 10.3   | Ignore Receiver Bit Timing Example                 |

|    | 10.4   | Long Break Timing Example                          |

|    | 10.5   | Loss of Arbitration Timing Example                 |

## TMS470 Platform Class II Serial Interface B (C2SIb)

The platform class II serial interface B (C2SIb) is a communication module used for transmitting and receiving data over a multi-master network. The C2SIb module is the interface from the digital logic of the 470R1x family of microcontrollers to an external, analog interface chip. Class II communications follow the J1850 Class B protocol established by the Society of Automotive Engineers (SAE). This reference guide covers C2SIb modules version 5.x and later.

| Topio |                                     | Pa | age |

|-------|-------------------------------------|----|-----|

| 1     | Overview                            |    | . 2 |

| 2     | Functional Description of the C2SIb |    | . 3 |

| 3     | Data Format                         |    |     |

| 4     | Transmitting C2SIb Messages         |    | 11  |

| 5     | Receiving C2Slb Messages            |    | 19  |

| 6     | Interrupts                          |    | 21  |

| 7     | General Purpose I/O                 |    | 24  |

| 8     | DMA Interface                       |    | 25  |

| 9     | C2SIb Internal Registers            |    | 30  |

| 10    | Timing Examples                     |    | 81  |

|       |                                     |    |     |

#### 1 Overview

The class II serial interface B (C2SIb) is designed to handle all of the class II digital logic functions and operations between the host CPU and the class II bus interface (analog interface).

The C2SIb module has the following features:

- Three external device pins

- C2SITX (C2SIb transmit data output)

- C2SIRX (C2SIb receive data input)

- C2SILPN (C2SIb loop-back enable)

- Two selectable data rates

- Normal mode: 10.4 Kbps

- 4X mode: 41.6 Kbps

- Multiple error detection flags

- Break detect error

- Overrun error

- Incomplete byte error

- Bit timing error causing data to be corrupted

- Cyclic redundancy check (CRC) error

- Transmission errors

- Short to ground errors

- Double-buffered receive and transmit functions

- Separate transmitter and receiver interrupts that can be interrupt driven or polled through the use of status flags

- Enable bits for interrupts

- Automatic CRC generation

- □ Low-power mode

- □ Automatic or manual calibration with external analog interface device.

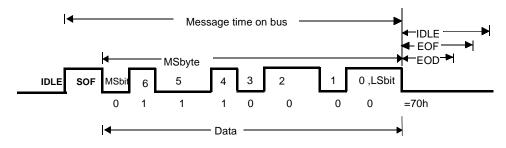

#### 2 Functional Description of the C2SIb

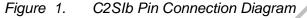

The C2SIb is contained within the TMS470. The C2SIb connects externally to an analog interface chip which is outside of the TMS470 as shown in Figure 1. This analog interface chip is required and acts as a buffer between the digital signals of the C2SIb and analog signals recognized by the C2SIb bus. The analog interface chip can be implemented with either a commercially available chip, such as the Harris HIP7020, or can be designed by the end-user.

The C2SIb is a serial interface that supports SAE J1850 class B protocol with selectable data transmissions at either normal or 4X operational mode. The C2SIbs receiver and transmitter are double buffered, and each has its own interrupt flags and bits.

Each individual C2SIb on the bus is referred to as a node as shown in Figure 1. For information on the flow of data through the C2SIb to bus interface pins and the related pin control registers see section 9.17 through section 9.26.

The C2SIb bus is a serial data communications link. The nondestructive contention protocol of the Class II bus requires that there be an active (high) voltage and a passive (low) voltage state of the bus. The function of the analog interface is to actively drive the bus to a high voltage when signaled by the C2SI, and passively let an RC network pull the bus down to a low voltage. It also monitors the class II data-bus state for received data that is transferred to the C2SIb. The bus is a wired OR arrangement.

The class II bus protocol includes a sleep mode in which any nodes can remain in a low-power standby condition until a node goes active and starts to send a message. The active state is detected by the others, which wake up in time to receive the message if voltage and clock signal are available to the analog interface.

The class II bus is intended to work in a relatively noisy environment. The analog interface (i.e., the Harris HIP7020, Motorola MC33390) is required to filter out the higher frequency noise. However, lower-frequency noise is generally caused by ground offset between the nodes. The C2SIb includes a digital filter to remove some of the lower frequency noise.

For a detailed description of the operation of the C2SIb bus, refer to the SAE J1850, Class B Data Communications Network Interface specification.

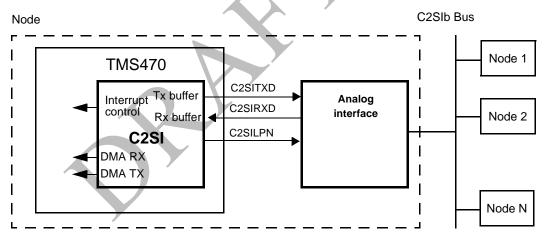

Figure 2. C2SIb Block Diagram

#### 2.1 C2SIb Internal Registers

A general description of the C2SIb internal registers is shown in Table 1. For a more detailed description of the individual bytes, see section 9.

| Address<br>Offset <sup>(1)</sup> | Mnemonic  | Name                               | Description                                                                    |

|----------------------------------|-----------|------------------------------------|--------------------------------------------------------------------------------|

| 0x00                             | C2SIGCRO  | Global Control Register 0          | Contains control bit for resetting the C2SIb module registers                  |

| 0x04                             | C2SIGCR1  | Global Control Register 1          | Contains bits for controlling the different modes of the C2SIb module          |

| 0x08                             | C2SICTR   | Control Register                   | Contains read/write bits for enabling control functions                        |

| 0x0C                             | C2SIICR   | Interrupt Control Register         | Contains transmit/receive interrupt enable control bits                        |

| 0x10                             | C2SIISR   | Interrupt Status Register          | Contains transmit/receive interrupt status flags                               |

| 0x14                             | C2SIGSR   | Global Status Register             | Contains bus status flags                                                      |

| 0x18                             | C2SICCSR  | Completion Code Status<br>Register | Contains read-clear transmit/receive completion status flags                   |

| 0x1C                             | C2SIBRK   | Break Status Register              | Contains the current status of the break register                              |

| 0x20                             | C2SIINDEX | Index Register                     |                                                                                |

| 0x24                             | C2SITDB   | Transmit Data Buffer               | Contains data bits to be transmitted out of the C2SITXD pin                    |

| 0x28                             | C2SICLK   | Interface Clock Register           | Set to the frequency of the interface clock                                    |

| 0x2C                             | Reserved  | Reserved                           | Reserved. Writes have no effect and reads return a 0.                          |

| 0x30                             | C2SIEMU   | Emulation Buffer Regis-<br>ter     | Mirror of C2SIRDB, but read does not clear interrupt                           |

| 0x34                             | C2SIRDB   | Receive Data Buffer                | Contains the current data from the receiver shift register                     |

| 0x38                             | C2SICAL   | Calibration Register               | Contains the calibration constant                                              |

| 0x3C                             | C2SIMTBC  | Transmit Byte Counter              | Determines the number of bytes to be transmitted                               |

| 0x40                             | C2SIPC0   | Pin Control Register 0             | Controls the polarity of the C2SIb TX and RX pins                              |

| 0x44                             | C2SIPC1   | Pin Control Register 1             | Determines if individual pins are used as general I/O or C2SIb functional pins |

| 0x48                             | C2SIPC2   | Pin Control Register 2             | Determines whether the individual pins are general purpose outputs or inputs   |

| 0x4C                             | C2SIPC3   | Pin Control Register 3             | Reflects the value on the pins                                                 |

### Table 1. C2SIb Internal Registers

(1) The actual address of these registers is device specific and CPU specific. See the specific device data sheet to verify the C2SIb register addresses.

#### Functional Description of the C2SIb

| 0x50 | C2SIPC4  | Pin Control Register 4 | Controls the logic value that is put on the individual pins when output |

|------|----------|------------------------|-------------------------------------------------------------------------|

| 0x54 | C2SIPC5  | Pin Control Register 5 |                                                                         |

| 0x58 | C2SIPC6  | Pin Cntrol Register 6  |                                                                         |

| 0x5C | C2SIPC7  | Pin Control Register 7 |                                                                         |

| 0x60 | C2SIPC8  | Pin Control Register 8 |                                                                         |

| 0x64 | C2SIPC9  | Pin Control Register 9 |                                                                         |

| 0x68 | C2SIRDMA |                        |                                                                         |

(1) The actual address of these registers is device specific and CPU specific. See the specific device data sheet to verify the C2SIb register addresses.

#### 3 **Data Format**

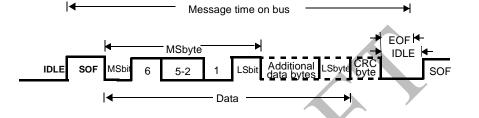

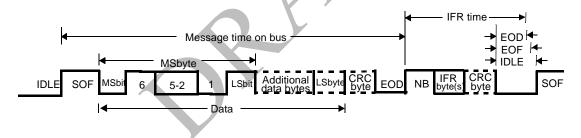

The C2SIb receive and transmit data formats are shown in Figure 4 and Figure 5. For an explanation of the various forms and effects of an in-frame response, refer to SAE J2178/1.

#### 3.1 **Basic Bit times**

The basic bit of the C2SI format consists of long and short data bits that change polarity with every bit. The bit length has different values that depend on whether the line is passive or active at the time. Other bit lengths have special meanings.

| Message Components  |   | Level    | Normal                  | Mode           | 4x Mo                   | ode            |

|---------------------|---|----------|-------------------------|----------------|-------------------------|----------------|

| incosage components |   | Level    | <b>ΤΧ</b> (μ <b>s)</b>  | <b>RX</b> (µs) | <b>ΤΧ</b> (μs)          | <b>RX</b> (μs) |

| SOF                 |   |          | 192-208                 | 163-239        | 48-52                   | 41-60          |

| Data Bits / CRC     | 0 | J        | 60-68                   | 34-96          | 14-18                   | 9-24           |

|                     | 1 |          | 122-134                 | 97-163         | 30-34                   | 24-41          |

|                     | 0 | <u></u>  | 122-134                 | 97-163         | 30-34                   | 24-41          |

|                     | 1 | л        | 60-68                   | 34-96          | 14-18                   | 9-24           |

| EOD                 |   | 7        | 193-207                 | 164-239        | 48-52                   | 41-60          |

| NB <sup>(1)</sup>   |   | <u></u>  | 122-134                 | 97-163         | 30-34                   | 24-41          |

|                     |   | Л        | 60-68                   | 34-96          | 14-18                   | 9-24           |

| EOF                 | 7 | ٦        | 271-289                 | 240-320        | 67-73                   | 60-80          |

| Break               |   | <u>_</u> | >290 short<br>>758 long | >239           | >290 short<br>>758 long | >60            |

C2SIb Message Time Duration Table 2

(1) There are two different conventions used for the normalization bit. One type is an active long, indicating that the in-frame response contains a CRC, and an active short indicating that it does not contain a CRC. The other type is vice versa: An active short indicating that the in-frame response contains a CRC, and an active long indicating it does not contain a CRC. The NBPOL bit (C2SIGCR.8) is used to determine which type of convention is to be used. See the NBPOL bit description in section 9.2.

> The C2SIb transmits data bits via variable pulse width modulation (VPM) at either the normal mode or the 4x mode (this can be controlled by the 4XMODE bit (C2SIGCR.2)). The following are descriptions of each of the message components.

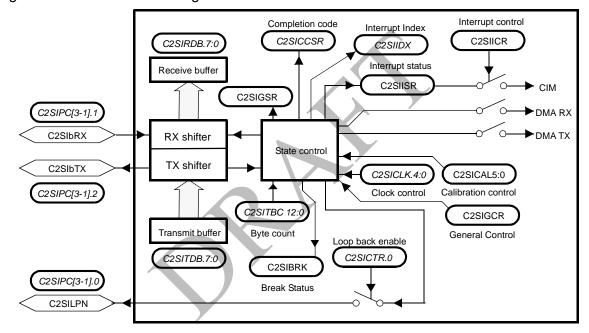

#### 3.2 Start Of Frame (SOF)

The start of every message is initiated when the transmitter drives the bus high for approximately 200  $\mu$ s (normal mode) or 50  $\mu$ s (4x mode), which is referred to as the start of frame (SOF).

#### 3.3 Data Bits and IFR Bits (when an IFR is used)

Once the SOF duration has been established, the data bits are transmitted on alternating high-low levels. Whether a data bit is a 0 or a 1 is designated by the time between two consecutive transitions. A pulse duration of approximately 64  $\mu$ s (normal mode) or 16  $\mu$ s (4x mode) represents a data 0 bit if the pulse is low, or a data 1 bit if the pulse is high. Likewise, a pulse duration of approximately 128  $\mu$ s (normal mode) or 32  $\mu$ s (4x mode) represents a data 0 bit if the pulse is the pulse is high, or a data 1 bit if the pulse is low. Refer to section 3.2.

#### 3.4 Cyclic Redundancy Check (CRC)

The CRC is optional. When this option is used, the C2SIb will automatically generate a CRC and append it to the end of the data bytes in a message, and to the end of an in-frame response.

There is no CRC for type I and II in-frame responses. Only type III in-frame responses include the CRC. For more information on the types of in-frame responses and CRC value calculations, see the SAE J2178/1 specification.

The generation of CRC in transmitted messages (normal messages and inframe response messages) and the expectation of CRC in received messages is controlled by the CRCDIS bit (C2SIGCR.3).

#### 3.5 End Of Data (EOD)

Once all data bits including CRC are sent, a falling edge occurs to generate a low level of approximately 200  $\mu$ s (normal mode) or 50  $\mu$ s (4x mode). This signifies the end of data (EOD).

An EOD will always appear after the last data byte in a message. Refer to Figure 2 and Figure 3.

#### 3.6 Normalization Bit

When there is an in-frame response from a responding device, the EOD duration ends when the responder sends its normalization bit before the start of the first in-frame response byte (refer to Figure 3).

3 TMS470 Peripheral Module User Guide

The normalization bit is always an active high level. The duration of the normalization bit is the same as a high level data 0 or data 1 bit time. When the normalization bit is 1, the in-frame response message ends with a CRC byte. When the normalization bit is 0, the in-frame response message does not end with a CRC byte. The NBPOL bit (C2SIGCR1.8) will switch to meaning of 1 and 0 (1 = NO CRC) in order to conform to specific manufacturers conventions.

#### 3.7 End Of Frame (EOF)

An end of frame (EOF) signifies the end of a message and appears at the end of all messages. If there is no in-frame response from a responding device, then the low level end of data (EOD) duration at the end of the data bytes will eventually stretch into an end of frame (EOF). Refer to Figure 3 or Figure 4. If there is an in-frame response, then the EOF appears after the last in-frame response byte (or CRC byte, if the CRC is used). Refer to Figure 5.

The EOF is a falling edge that lasts approximately 280  $\mu$ s (normal mode) or 70  $\mu$ s (4x mode). Once EOF reaches 320  $\mu$ s (normal mode) or 80  $\mu$ s (4x mode), the device that transmitted the previous message may begin transmitting a new start of frame (SOF) since no other nodes are trying to access the C2SI bus.

Other C2SIs desiring bus access may try to arbitrate as early as between  $280\mu s$  and  $320\ \mu s$  (normal mode). When all other devices that desire bus access detect this rising edge on the bus, they send their start of frame (SOF) almost immediately. If a device loses arbitration (the high voltage level is dominant in arbitration), it removes itself from the bus and its transmission is stopped.

#### 3.8 Break

When a break signal is sent onto the bus, all nodes on the bus stop transmission immediately and go back into a reset condition. A break signal is initiated upon a rising edge and has a duration of at least 240  $\mu$ s. The C2SIb can transmit two different lengths depending on the LONGBRK bit. If this bit is a 1, then the break is 768  $\mu$ s else the break is 300  $\mu$ s. In 4X mode, the receiver recognizes a break if the RXD pin is active for over 60  $\mu$ s. It will transmit a standard 1X break in both the 1X and the 4X mode.

#### 3.9 Examples

The following examples give some simple messages and have the various bit types labeled.

#### Data Format

#### Figure 3. Simplest 1 Byte Message

Figure 4. Typical C2SIb Data Frame Format Without In-Frame Response

Figure 5. Typical C2SIb Data Frame Format With In-Frame Response

10

### 4 Transmitting C2SIb Messages

C2SIb transmission data must be transferred to the C2SITDB transmit data buffer by using the CPU or the DMA controller. For DMA-based operations, see section 8.1 and the DMA controller specification.

All messages can be transmitted with or without a CRC appended, and is controlled by the CRCDIS bit in the C2SIGCR1 register (C2SIGCR1.3).

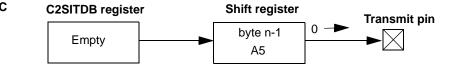

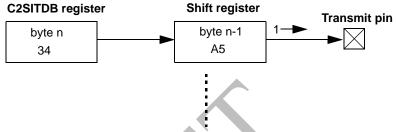

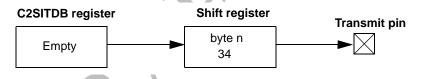

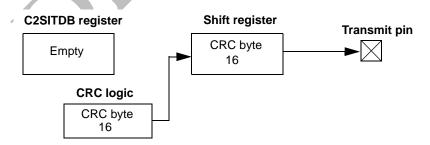

Internal to the C2SIbs transmitter is a shift register that holds the contents of a byte as it is physically shifted out MS bit first on the C2SITXD pin. User software continues to supply data to the C2SITDB register until the entire message has been transferred. Figure 5 shows the transmission of the last 2 bytes of an n-byte message plus an appended CRC byte.

#### Figure 6. Byte Transmission

The C2SITDB register is empty as the shift register shifts out byte n-1.

Write the last byte, n, into the C2SITDB buffer. Note that C2SIb TBC decrements to zero when C2SITDB is written. Data shifts out MSB first.

As soon as the shift register has completely shifted out byte n-1, byte n is loaded from the C2SITDB register into the shift register. The C2SITDB is now empty.

Once byte n is completely shifted out of the shift register and the transmit byte counter (C2SITBC) has counted down to zero, if CRCDIS = 0 (C2SIGCR.3), then the CRC byte is calculated and loaded into the shift register.

12

During transmission, the C2SIbs receiver and transmitter monitor each bit that the transmitter delivers to the C2SIb bus to detect loss of arbitration. Since an active voltage is the dominant level, arbitration is lost when the transmitter attempts to deliver a passive to the C2SIb bus and the receiver detects an active voltage on the data link. This event forces the transmitter to immediately enter the idle state. It also causes the arbitration lost bit (ARBIF), transmit idle bit (TIDLIF), and transmit buffer empty bit (TBEIF) (C2SIISR.7, 6, 5)

to be set to 1 and the transmit DMA enable bit (TXDMAEN) (C2SICTR.3) to be cleared to 0.

A start bit (SOF) is neither a data 1 nor a data 0 and is not subject to arbitration. The C2SI's transmitter will place the start bit on an idle bus or begin following another module's start bit already in progress.

#### Note: Transmission with Lost Arbitration

The C2SIb module does not attempt to retransmit a message that lost arbitration during a transmission attempt except in the case of a type II inframe response. See the T2IFR bit (C2SIGCR1.1) description in section 9.2.

Detection of lost arbitration is handled by monitoring the ARBIF bit (C2SIISR.7). If the ARBIE bit (C2SIICR.7) = 1, a transmit interrupt request can be generated on this event.

While the ARBIF bit is set, the transmitter does not attempt to communicate on the link. User software must guarantee that ARBIF is cleared before attempting to transmit on the bus.

The C2SIb blocks writes to the transmit buffer, C2SITDB, if one of the following conditions are present.

- ARBIF arbitration flag set.

- BRKIF bit set or break is in progress

- TBCOUNT is zero

- C2SICCSR register is full, indicated by the RCCIF flag set

- TXUOIF flag is set

In addition to blocking the write, the C2SIb will set the TXUOIF bit to indicate a failed write.

#### 4.1 Transmitting Non-IFR Messages

Non-IFR messages are sent when the TIFR bit (C2SIGCR.1) = 0. Before beginning a transmission, the following steps are recommended:

- Set the C2SITBC register to a non-zero value.

- Read the C2SICCSR register.

- Read the C2SIRDB register.

- Check that Arbitration bit (ARBIF) is cleared (C2SIISR.0 = 0).

- Load the C2SITDB register with either the CPU or with a DMA transfer. This last step starts the transmission.

The C2SIb monitors the C2SIb bus until it has become IDLE. Transmission of an SOF sequence prefixes a normal messages packet of data bytes. Following the SOF, the shift register is loaded from the C2SITDB register and the transmission of data bytes continues until the C2SITDB register and the shift register are empty and C2SITBC is 0. A CRC is appended to the end of the packet of data bytes if the CRCDIS bit is 0 (C2SIGCR.7 = 0).

When you start a message, the first byte put into the C2SITDB will quickly move to the empty shift register and the TBEIF bit will indicate that the C2SITDB is ready for the second byte. Always wait for the TBEIF bit to be set before loading into the C2SITDB.

Put a new byte into the C2SITDB buffer after checking for errors and after checking if the TBEIF bit is set. If you clear the TBEIE bit after the writing the last byte you wont get an extraneous interrupt when the message finishes.

#### 4.2 Transmitting IFR Messages

In-frame response messages are sent when TIFR bit (C2SIGCR.0) is 1. Before beginning a transmission, the following steps are recommended:

- Set the TIFR bit.

- Check for message errors.

- Set C2SITBC register has to a non-zero value.

- Read the C2SICCSR register.

- Read the C2SIRDB register.

- Check Arbitration lost interrupt bit (ARBIF) is cleared (C2SIISR.7 = 0).

- Load C2SITDB register with either the CPU or with a DMA transfer. This last step starts the transmission.

The responder of the message begins transmitting an in-frame response after the occurrence of an EOD. A normalization bit (NB), which reflects whether or not a CRC follows the in-frame response, prefixes the in-frame response packet of data bytes. Following the NB, the shift register is loaded by the C2SITDB register and the transmission of data bytes continues until the C2SITDB register and the shift register are empty. A CRC is appended to the end of the packet of the in-frame response bytes if CRCDIS bit is 0 (C2SIGCR.4 = 0).

The TIFR bit (C2SIGCR.0) controls whether or not the C2SIb is transmitting an in-frame response or a normal start-of-frame message. The TIFR bit (C2SIGCR.0) is automatically cleared if the receiver detects any errors during reception. This guarantees that an in-frame response is not transmitted in response to a corrupt message. When a receiver detects any errors during reception, the C2SIb will:

- Clear the TIFR bit (C2SIGCR.0)

- Reset the transmitter

- Clear the TXDMAEN bit (C2SICTR.16)

- Set the TBEIF (C2SIISR.5) and TIDLIF (C2SIISR.6) bits.

The application is responsible for recognizing that the message currently being received is expecting an in-frame response to be transmitted as a response. This may require the application to monitor each incoming byte of a message to detect this condition. The application must make sure that the in-frame response is ready for transmission before the received packets EOD sequence is completed.

#### 4.3 Transmitting BREAK Messages

The transmission of a BREAK sequence is forced by setting the TBRK bit (C2SICTR.0) to 1. This results in the current transmit/receive condition of the link being overridden by the BREAK sequence. The duration of the BREAK sequence is independent of the state of the 4XMODE bit (C2SIGCR1.3). If the LONGBRK bit (C2SICTR.1) is set, the break will be ~768  $\mu$ s long. Otherwise, if it is cleared the break will be ~300  $\mu$ s long.

Transmitting/receiving a BREAK disables all transmissions/transmitters on the link. It also automatically clears the 4XMODE bit. When the BREAK occurs, all transmitters transmitting a message other than BREAK will be forced off the bus.

You must wait for the break to finish before writing to the transmit data buffer (C2SITDB). See section 5.3 for an explanation on how the receiving devices react to a BREAK.

#### 4.4 Transmission Arbitration

When a message is transmitted by the C2SIb module, a copy of the bit stream is redirected back to the received section so it can monitor its arbitration progress. If the C2SIbs transmitter sends a passive data level and the C2SIbs receiver returns an active data level, then the transmitter has lost arbitration.

When arbitration is lost, the transmitter removes itself from the data link, and the C2SIb will:

- Clear the XMITOK bit (C2SICCSR.8) in the Completion Code register.

- Set the ARBIF bit (C2SIISR.7)

- Clear the TXDMAEN bit (C2SICTR.16) and go into a transmitter idle state

- Mark the internal shift register and the C2SITDB register as empty, therefore, setting the TIDLIF and TBEIF bits (C2SIISR.6, 5).

#### Transmission with Lost Arbitration

The C2SIb module does not attempt to retransmit a message that lost arbitration during a transmission attempt (except during a type II in-frame response). Detection of loss arbitration is correctly handled by monitoring the ARBIF bit (C2SIISR.7). An interrupt request can be generated on this event if ARBIF = 1 and ARBIE bit = 1 (C2SIICR.7).

While the ARBIF bit is set, the transmitter does not attempt to communicate on the link. User software must guarantee that ARBIF is 0 (C2SIISR.7) before attempting to retransmit on the link.

If arbitration is not lost, the transmitter naturally idles itself at the end of a message. The transmitter is idle when the TXDMAEN bit (C2SICTR.16) is cleared and when TIDLIF and TBEIF bits (C2SIISR.6, 5) go high. In addition, the C2SIbs receiver and transmitter collectively determine whether the XMITOK bit (C2SICCSR.8) should be set. It is set if the transmitter wins arbitration and the receiver has not detected any errors during the reception of the transmitted message.

#### 4.5 Byte Boundary Loss of Arbitration when Transmitting

If arbitration is lost on the last bit of a byte being transmitted, the transmitter does not immediately remove itself from the data link. Instead it transmits two additional 1s. If arbitration is lost again on the first 1, the transmitter immediately stops transmitting.

If this loss of arbitration was caused by noise, the extra two 1s are intended to corrupt a potentially acceptable, but erroneously short message generated by the transmitter. If loss of arbitration was caused by a higher priority message, then the 1s have no effect on that message.

#### 4.6 Bus Error Conditions

Conditions can occur in a system that will temporarily or permanently cause the C2SIb bus to fail. Three of the more common failure modes are:

- □ Short-to-voltage

- □ Short-to-ground

- Bus open, broken wire

The commercially available bus interface devices will handle the physical strain of short to ground and short to power without damaging either device. The interface device however will not directly inform the C2SIb module of the fault condition. The C2SIb module must determine the fault through indirect means.

#### 4.6.1 Short-to-Voltage

The following conditions will make the bus appear to be shorted to a voltage source.

- Bus shorted to voltage source

- TX pin stuck high

- □ RX pin stuck high

- □ TX signal between C2SIb module and interface device shorted to voltage

- RX signal between C2SIb module and interface device shorted to voltage

Each of these conditions will cause a BREAK condition on the C2SIb and set the break flag bit, BRKIF. If the break interrupt enable bit, BRKIE, is also set and device interrupts enabled then the BREAK will cause an interrupt. See section 5.3 for break handling. The problem can be isolated to a bus problem if the C2SIb enables the loop back mode of the device. The C2SIb will still be able to send and receive in loop back mode if the bus shorts to voltage.

#### 4.6.2 Short-to-Ground

The follow conditions will make the bus appear to be shorted to ground.

- Bus shorted to ground

- TX pin stuck low (may still receive from other devices)

- RX pin stuck low

- TX signal between C2SIb module and interface device shorted to ground (may still receive from other devices).

- RX signal between C2SIb module and interface device shorted to ground

If the C2SIb transmitter begins a message under these conditions the TXD pin will be set high and the receive pin will wait to see this high signal. If the receiver does not see a high for a certain time the C2SIb will declare a bus short condition and stop the transmitter, set the SHORTGND bit and set the

TXERR bit. The short declaration comes about 80  $\mu s$  after the transmitter sets the TXD pin high.

If the short comes after the SOF, the message will be corrupted and can be detected in two different ways.

- 1) If it is before the first good byte, the TIDLIF and TXERR bits get set.

- If it is after the first good byte, the RCCIF bit sets in addition to the previous bits and some combination of BITERR, BYTERR, or CRCERR will be set depending on the short location in the message.

The C2SIb module cannot detect a short-to-ground condition unless it is transmitting. Higher levels of software must detect the absence of bus traffic and attempt to isolate the cause.

The problem can be isolated to a bus problem if the C2SIb enables the loop back mode of the device. The C2SIb will still be able to send and receive in loop back mode if the bus shorts to ground or voltage.

#### 4.6.3 Open Bus

The following conditions will make the bus appear to be open.

- Bus open or

- Bus wire broken

In this instance, the transmitter appears to be working if no in-frame responses are expected. The data sent out the TXD pin will return through the RXD pin in the normal manner. Lack of an expected IFR will point to this condition as a possible problem. (Problems with the device generating the IFR is another cause.)

The C2SIb will receive no data from some or none other devices during this time so bus protocols should be set up to identify this type of problem.

#### 4.6.4 Other Bus Errors Not Discussed

Some other bus errors are possible, but are not discussed:

- □ The intermittent error. You should determine how long are the errors and how often do they occur?

- Open signals between C2SIb and interface device. This error may look like either a short-to-ground, short-to-power, or an intermittent error, depending on the interface device.

- □ Bus with too much load or capacitance—slow bus.

- □ Combination of several of the above problems.

### 5 Receiving C2SIb Messages

The following sections discuss receiving C2SIb messages.

#### 5.1 Receiving Normal Messages

The reception of a normal message is preceded by an SOF sequence. Data bytes are received through the receivers shift register, and then transferred into the C2SIRDB register. Reception of a normal message continues until a non-data bit sequence is received (for example, EOD, EOF, BREAK, noise). When this occurs after receiving one good byte then a completion code for the message is updated in the C2SICCSR register. Messages received with errors in the first byte are ignored and no interrupts generated.

The state of the CRCDIS bit (C2SIGCR.4) controls the formation of a CRC for transmitted data, and whether the receiver should expect a CRC at the end of the incoming data. If a CRC is expected and there is a CRC error, the CRCERR bit (C2SICCSR.16) in the completion code is set.

#### 5.2 Receiving IFR Messages

The reception of an in-frame response (IFR) follows after the C2SIb successfully transmitted a normal message which ended with an end of data (EOD). What sets it apart from the reception of a normal message is the lack of an end of frame (EOF).

Reception of an in-frame response continues until a *non-data bit* sequence is received (for example, EOD, EOF, BREAK, noise). When this occurs, a completion code for the message is updated in the C2SICCSR register.

The reception of an in-frame response sets the IFR bit (C2SICCSR.0) in the completion code register. The state of the NB bit is reflected in the completion codes IFRCRC bit (C2SICCSR.1). The IFRCRC bit is set when an in-frame response with a CRC byte appended to the end of it has been received. The CRCERR bit (C2SICCSR.16) in the completion code will be set if there are any errors in this appended CRC byte.

If the software needs to determine if a message is normal or IFR on the first byte, it may be best to use the RIFR bit (C2SIGSR.4). Reading the IFR bit in C2SICCSR register could clear the RCCIF flag, causing a missed interrupt.

If you need to know the IFR status after receiving a byte (RBFIF) then use the RIFR bit. To get the IFR status after reading a completion code (RCCIF) use the IFR bit (C2SICCSR.0).

Note that the receiver can receive an IFR without a CRC even if CRCDIS bit = 0 (C2SIGCR1.3).

#### 5.3 Receiving BREAK Messages

A BREAK on the data link causes any messages on the link to be aborted. The BREAKs corruption of a message in process is detected when a symbol has been overridden. The receivers reaction to a BREAK depends on conditions at the time of the BREAK.

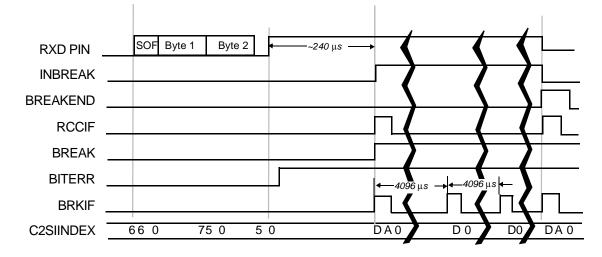

The BRKIF flag (C2SIISR.1) will set when the C2SIb bus has been active for over the minimum break time of 240  $\mu$ s. This break resets the transmitter which sets the TIDLIF and TBEIF bits. It stops the receiver and clears the 4XMODE bit (C2SIGCR1.2).

If a message was in process, a symbol could get corrupted and the receiver posts a completion code with errors (BREAK and possibly BTYERR, BITERR or CRCERR). This sets the RCCIF bit (C2SIISR.2) and, if RCCIE bit is 1, a receive interrupt request is generated.

When the software sees the BRKIF bit set it should read the C2SIRK register to determine the current status of the break and to clear the BRKIF bit. If the BREAKEND bit is set, then the current break is over and the C2SIb can begin any new transmissions. If the INBREAK bit is set, then the C2SIb must suspend C2SIb messages until either the break ends or software determines a short-to-voltage condition exists.

To help in determining short-to-voltage conditions, the BRKIF bit will set every 4096  $\mu$ s while a break continues. Software needs to count these breaks flags and determine the point between the two possible conditions.

When the break ends, two interrupts sources will occur. The first is the BRKIF bit caused by the BREAKEND bit setting in C2SIRK register. The second interrupt source is the RCCIF bit setting with the BREAK bit set in the C2SICCSR register. The RCCIF can interrupt with BREAK bit set at either the end of a break corrupted message or at the end of the break.

#### 5.4 Receiving Digital Filters

A digital filter internal to the C2SIb is used to filter noise pulses from the class II receiver driver module that are smaller/shorter than the analog interface chips filter time constant.

#### 6 Interrupts

The C2SIb has two main interrupt-related registers—one is an interrupt status register (C2SIISR), and the other is an interrupt control register (C2SIICR). The C2SIb module generates one interrupt request back to the CIM. When an interrupt generating event occurs, its corresponding interrupt status register (C2SIISR) bit is set (for example, ARBIF = 1). If the corresponding interrupt control register (C2SIICR) bit is enabled (for example, ARBIE = 1), then an interrupt request is sent to the CIM.

If multiple interrupt conditions occur either at the same time or during the time the interrupt service routine is being executed, multiple interrupt status flags will be set, but only one interrupt will be generated back to the CIM. User software must read the C2SIISR register to determine which event caused the interrupt and to determine which C2SIb interrupt condition has priority; the C2SIb allows the user to determine priority.

If the interrupt is caused by a wake from sleep mode, however, the WAKE bit (C2SIISR.8) is set, and will generate an interrupt.

#### 6.1 Proper Handling of Events

The interrupt index register, C2SIINDEXprovides a means to quickly handle interrupts generated by the C2SIb module. This register contains a value that corresponds to the source of the interrupt. The index value has two zeros appended to the beginning so that the program can use this value in a jump table.

The table below gives the highest priority source of the **enabled** interrupts. If multiple sources are present, the highest priority will output first. When the proper interrupt flags, enables or registers are dealt with, the value will change to the next highest priority.

| INDEX | Conditions                                   | Description                         |

|-------|----------------------------------------------|-------------------------------------|

| 0     | None of below                                | No interruptslowest priority        |

| 1     | TIDLIF and TIDLIE                            | Transmitter idle                    |

| 2     | RCCIF and RCCIE                              | Completion code for good RX         |

| 3     | RCCIF and RCCIE and XMITOK                   | Completion code for good TX         |

| 4     | RBFIF and RBFIE                              | RX ready, IFR                       |

| 5     | RBFIF and RBFIE and IFR                      | RX ready, not IFR                   |

| 6     | TBEIF and TBEIE                              | TX ready for next character         |

| 7     | TBEIF and TBEIE and TBCOUNT=1                | TX ready for last character         |

| 8     | ARBIF and ARBIE                              | Arbitration conflict                |

| 9     | RXOIF and RXOIE                              | RX underflow                        |

| A     | RCCIF and RCCIE and (C2SIERR) <sup>(1)</sup> | Error in completion code- RX and TX |

| В     | TXUOIF and TXUOIE                            | TX under/over flow                  |

| С     | TIDLIF and TIDLIE and TXERROR                | Transmit error (useful in 1st byte) |

| D     | BRKIF and BRKIE                              | Break found or continues.           |

| Е     | WAKE and WAKEEN                              | Wake up—highest priority            |

| F     | Reserved                                     |                                     |

#### Table 3. Interrupt Index Table

(1) C2SIERR = (BITERR or BYTERR or CRCERR or ROVR)

### 6.2 Handling interrupt sources

Some interrupt generating events, such as the transmit buffer empty interrupt are persistent and can occur continuously unless their cause is handled. Each interrupt bit should be cleared by either reading its associated register or by writing a 1 to the bit.

| Table 4.Interrupt Bits and Associated Registers |

|-------------------------------------------------|

|-------------------------------------------------|

| Bit | Name of Register | Comments                    |

|-----|------------------|-----------------------------|

| 0   | RBFIF            | Read the C2SIRDB register.  |

| 1   | BRKIF            | Read the C2SIBRK register.  |

| 2   | RCCIF            | Read the C2SICCSR register. |

| 3   | RXOIF            | Write 1 to clear.           |

| 4   | TXUOIF           | Write 1 to clear.           |

| Bit | Name of Register | Comments                                        |

|-----|------------------|-------------------------------------------------|

| 5   | TBEIF            | Read the C2SITDB register.                      |

| 6   | TIDLIF           | Read the C2SITDB register.                      |

| 7   | ARBIF            | Write 1 to clear.                               |

| 8   | WAKE             | Read the C2SIGSR register (also clears WAKEEN). |

Table 4. Interrupt Bits and Associated Registers (Continued)

When writing ones to the bits, make sure all other bits are zeros. Do not use C commands, such as "ARBIF.bit = 1". Such commands usually result in a read of the register followed by an AND operation and finally writing the result back. If an interrupt occurs in the middle of this, then the final write will clear the interrupt and it will be missed. Instead use writes to the registers such as "C2SIISR = 0x80" to clear the ARBIF bit.

All these bits can be cleared by writing ones to the bits, but it is strongly recommended to read the associated register instead. In addition, it is also strongly recommended to only read the interrupts flags associated register only when the flag is set. If you read the associated register just after flag gets set then the flag will clear and an interrupt will be missed. This caveat would not apply while initializing after a reset.

#### **General Purpose I/O** 7

Each of the C2SIb pins may be programmed via the C2SIb pin control registers (C2SIPC0–9) to be a general-purpose I/O pin.

When the C2SIb module is not used, the C2SIb pins may be programmed to be either general input or general output pins. This function is controlled via the C2SIPC1 register. The xxDIN bits in the C2SIPC3 register always read the unfiltered values on the pins. When turning a pin into an output, first write the data to the xxOUT bit and then write to the xxDIR bit to turn on the output driver.

#### 8 DMA Interface

#### 8.1 DMA Transactions

If handling the C2SIb message traffic on a byte-by-byte basis requires too much CPU overhead and if the particular device is equipped with the DMA controller, the C2SIb may use the DMA controller to receive or transmit data directly to memory. The C2SIb module contains two DMA request enable bits: a transmit DMA enable (TXDMAEN) and a receive DMA enable (RXDMAEN); see (C2SICTR.17, 16).

When a byte is being transmitted or received, the C2SIb will signal the DMA via a DMA request signal. The DMA controller will then perform the needed data manipulation.

For DMA-based transmissions, all messages (other than a BREAK) are assembled in RAM, and DMA transfers move the message, byte-by-byte, from RAM into the C2SITDB register. See the DMA controller specification for more information. All messages transferred via DMA contain only data received via the receive buffer; the contents of the completion code status register (C2SICCSR) are not transferred to RAM. See section 9.7.

The application is responsible for programming the C2SITBC to the desired number of bytes to be transferred. If the C2SITBC contains a different value than the DMA byte count register, a transmit under-run or overrun condition can occur. For specific DMA features, refer to the DMA controller specification.

Writing to the TXDMAEN bit will automatically request a DMA action, so it should be the last action when initializing. After that, the setting of the TBEIF will trigger the DMA action. The receive DMA action is triggered by the setting of the RBFIF bit. Of course, these two bits should have their interrupts disabled via the TBEIE and RBFIE bits to take advantage of the DMA.

#### 8.2 Non-DMA Transactions

When the application performs data transfers via the CPU, the application is responsible for guaranteeing that the C2SITDB register is kept full and that the C2SIRDB register is read in accordance with class II data communication rates. Failure to do so results in truncated transmissions or overrun during reception.

#### 8.3 4X Mode

The C2SIb module has the ability to function in the normal mode or 4X clock mode. In the 4X clock mode, timing constants for the generation/reception of signals on the data link are effectively divided by four.

Changing the state of the 4XMODE bit (C2SIGCR.6) resets the class II statemachine status, thereby aborting any transmissions or reception in progress. The receipt of a BREAK sequence automatically clears the 4XMODE bit and resets the class II state machine.

If the state of the 4XMODE bit is changed during the reception of a message, the C2SICCSR register is updated to mark the end of the aborted message.

The C2SIb should calibrate before transmitting in 4X mode. See section 8.6.

#### 8.4 Low Power Mode

The C2SIb module has two means to be placed in a low-power mode: a global low-power mode from the system and a local low-power mode via the LPM bit (C2SIGCR1.8). The net effect on the C2SIb is the same, independent of the source.

A low-power mode in effect shuts down all the clocks to the module. During a global low-power mode, nothing will be written to any register. A local lowpower mode has the same effect, with the exception that the LPM bit may be written to, and hence able to place the module into a functional mode.

Since entering a low-power mode has the effect of suspending all statemachine activities, care must be taken when entering such modes to insure that a valid state is entered when low-power mode is active. For example, if a low power mode is entered during a transmission on the Class II bus before the message is complete, a completion code will never be sent out, and hence the integrity of the bus is corrupted. As a result, application software must insure that a low power mode is not entered during a transmission.

Low-power mode may be used in conjunction with the WAKEEN bit (C2SIICR.8) to allow C2SIb bus activity to wake the device and exit the low-power mode.

To enter low-power mode and wake up on any C2i bus activity:

- □ Wait for idle bus by checking the IDLE bit (C2SIGSR.0)

- □ Service all interrupt sources or disable bits in the C2SIICR register

- □ Set the WAKEEN bit (C2SIICR.8)

- Set the LPM bit (C2SIGCR1.16). This is now local low-power mode.

Please refer to the TMS470 Platform Architecture Specification for information about entering low power modes. The global C2SIb interrupt does not have to be enabled to wake up the device.

To enter low-power mode and ignore all C2SIb bus activity:

- □ Wait for idle bus by checking the IDLE bit (C2SIGSR.0)

- □ Clear the WAKEEN bit (C2SIICR.8). Clear C2SIICR bit 8.

- Set the LPM bit (C2SIGCR1.8). This is now local low-power mode.

- Unlike some other modules, you do not have to be in a privilege mode to set the LPM bit.

To exit the low-power mode, you must first clear the LPM bit. No other C2SIb bit is writable until the LPM bit is cleared. The internal C2SIb counters and state machine will not start until the LPM bit is cleared. This means the time from the LPM cleared to the end of the OSF starting bit must meet the minimum SOF time to receive a good message. In many instances the wake-up message will be lost because this time could not be met.

#### 8.5 Emulation Mode

The C2SIb module may be placed in a suspend mode by the TMS470 system. This is usually when the TMS470 is being used as an emulator or being debugged via the test access port (TAP). When being used by a monitor program, the receive data buffer (C2SIRDB) has a mirror register called C2SIEMU. This register contains the same contents as the C2SIRDB, but a read of this register will not cause the receive buffer full interrupt flag (RBFIF) to clear. This allows the user to keep a memory window open for the receive buffer, without having the monitor program clear the interrupt automatically.

The software has the choice via the ESPEN bit (C2SIGCR.17) as to the statemachine action taken during a suspend mode. If the ESPEN bit (C2SIGCR.17) is active, the C2SIb will immediately suspend its activity. Once again, the users software must ensure that suspending the transmission or reception of data will not corrupt the class II bus. If ESPEN is inactive, the C2SIb will continue operating normally.

#### 8.6 Calibration Mode

Calibration allows the C2SIb module to know the expected time delay between sending a bit out of the TXD pin and receiving the same bit back into the RXD pin. Because of the variations among different analog designs, the C2SIb module should be calibrated to the actual bus load. An improperly calibrated C2SIb will have transmit bits times outside the ideal values and

may not arbitrate correctly when the C2SIb bus is already operating at very marginal levels. The J1850 protocol allows for variation but this tolerance is better used solving C2SIb bus degradation.

The calibration constants do not affect the C2SIbs reception of data from other devices. The value is used mainly for transmission and arbitration.

On reset, the C2SIb will place default value of 23 into the C2SICAL register. Changing to 4X mode with the 4XMODE bit will place a default value of 7 in the register. Changing back to normal mode will again put 23 in the calibration register.

The C2SIb module calibration constant can be set automatically or manually. Use the formulas below to manually set the calibration value in the C2SICAL register.

cal register = TX/RX delay  $\mu$ s + 4 iclks + 7  $\mu$ s ; normal mode (total  $\mu$ s) cal register = TX/RX delay  $\mu$ s + 4 iclks ; 4X mode (total  $\mu$ s)

For example, with a delay of 16  $\mu$ s between the TXD and RXD pins and running with an ICLK speed of 10 Mhz, the C2SICAL register should contain 16 + 0.4 + 7 or 23.

Where iclk is the peripheral bus clock frequency. At higher speeds, this term becomes insignificant. Digitizing errors ranging from 0 to 1  $\mu$ s apply to both calculations and will affect output values.

To find the TX/RX delay measure the time from the TXD changes to the time the change is observed on the RXD pin. This is a function of the external interface chip and to a lesser extent on the bus loading. Measure across the operating temperature range. The normal start bit measured at the TXD pin should ideally be 200  $\mu$ s.

To use the automatic mode the software must transmit at least one byte of code with the CALEN bit (C2SIGCR.25) set. After sending the message the CALEN bit will clear and the measured value will be in the C2SICAL register. A counter in the C2SIb will measure the delay and adjust the transmit timings automatically according to the results of the calibration cycle.

If possible, it is recommended that you first calibrate using the loop-back mode to get close to the final value and then send a calibration message on the loaded bus. It is also possible to calibrate using ONLY the loop-back mode on some external transceivers, but this will need to be determined on a system-by-system basis.

If you calibrate on a busy bus, then you may lose arbitration to another device. If this happens you must repeat the loop-back cycle before attempting

another calibration cycle on the bus. Keep trying until the C2SIb returns a XMITOK status after a bus calibration.

# B9C2SIb Internal Registers

## Figure 7 summarizes the internal registers. The following sections provide detailed information.

Figure 7. C2SIb Internal Register Summary

|                   |    |          | •       |         | -  |            |           |                          |              |      |       |       |             |           |           |           |

|-------------------|----|----------|---------|---------|----|------------|-----------|--------------------------|--------------|------|-------|-------|-------------|-----------|-----------|-----------|

| Offset<br>Address | 31 | 30       | 29      | 28      | 27 | 26         | 25        | 24                       | 23           | 22   | 21    | 20    | 19          | 18        | 17        | 16        |

| Register          | 15 | 14       | 13      | 12      | 11 | 10         |           | 8                        | 7            | 6    | 5     | 4     | 3           | 2         |           | 0         |

|                   | 1  | I        | I       | I       | 1  | 1          | 1         | 1                        | I            | 1    | 1     | 1     | 1           | 1         | I         | 1         |

| 0x00              |    |          |         |         |    |            |           | Rese                     | erved        |      |       |       |             |           |           |           |

| C2SGCR0           |    |          |         |         |    |            |           |                          |              |      |       |       |             |           |           |           |

| Section 9.1       |    |          |         |         |    |            | 1         | Reserve                  | d            |      |       |       |             |           |           | RE<br>SET |

|                   |    |          |         |         |    |            |           |                          |              |      |       |       |             |           |           | 361       |

|                   | 1  |          |         |         |    |            | 1         | 1                        |              |      |       |       |             |           |           |           |

| 0x04              |    |          | Reserve | ed      |    | TX<br>RESE | CALE<br>N | NBPO<br>L                |              |      | Rese  | erved |             |           | ESPE<br>N | LPEN      |

| C2SIGCR1          |    |          |         |         |    | Т          |           |                          |              | 1    |       | 1     | 1           |           |           |           |

| Section 9.2       |    |          |         | Reserve | ed |            |           | LPM                      | Reser<br>ved |      |       |       | CRC-<br>DIS | 4X<br>MOD | T2IFR     | TIFR      |

|                   |    |          |         |         |    |            |           |                          |              |      |       |       |             | E         |           |           |

|                   |    |          |         |         |    | IGNO       |           |                          |              |      |       |       |             |           |           | ТХ        |

| 0x08              |    |          | Reserve | ed      |    | RE         |           | Reserved RXI MAE         |              |      |       |       |             |           |           | DMAE<br>N |

| C2SIGCTR          |    |          |         |         |    |            |           |                          |              |      |       |       |             |           |           |           |

| Section 9.3       |    |          | Res     | erved   |    |            | SOFX      | X ARBI Reserved LONG BRK |              |      |       |       |             |           |           | TBRK      |

|                   |    |          |         |         |    |            | I         | <u> </u>                 |              |      |       |       |             |           |           |           |

| 0x0C              |    |          |         |         |    |            |           |                          |              |      |       |       |             |           |           |           |

| C2SIICR           |    |          |         |         |    |            |           | Rese                     | erved        |      |       |       |             |           |           |           |

| Section 9.4       |    |          |         | Reserve | hd |            |           | EN                       | ARBI         | TID- | TBEIE | тхио  |             | RCC       | BRKI      | RBFIE     |

| Section 9.4       |    | Reserved |         |         |    |            |           | WAKE                     | E            | LIE  |       | IE    | IE          | IE        | Е         |           |

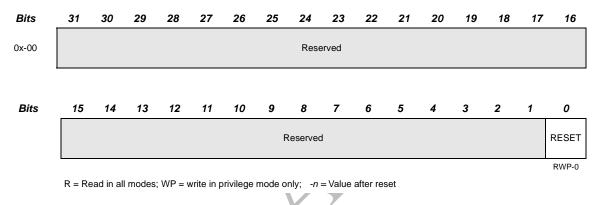

| 0x10<br>C2SIISR |          | Rese | erved |             |       |            |            |           |       |       |

|-----------------|----------|------|-------|-------------|-------|------------|------------|-----------|-------|-------|

| Section 9.5     | Reserved | WAKE | ARBIF | TID-<br>LIF | TBEIF | TXUO<br>IF | RXUO<br>IF | RCC<br>IF | BRKIF | RBFIF |

# C2Slb Internal Registers

| Offset                  | 31 | 30                                 | 29  | 28      | 27    | 26    | 05               | 24               | 23         | 22 | 21 | 20  | 19   | 18  | 47              | 16  |  |

|-------------------------|----|------------------------------------|-----|---------|-------|-------|------------------|------------------|------------|----|----|-----|------|-----|-----------------|-----|--|

| Address<br>Register     | 15 | 14                                 | 13  | 12      | 11    | 10    | 25<br>9          | 8                | 7          | 6  | 5  | 4   | 3    | 2   | 17<br>1         | 0   |  |

| 0x14                    |    |                                    | Res | erved   | ·     |       | TX<br>ACTIV<br>E | RX<br>ACTIV<br>E | / Reserved |    |    |     |      |     |                 |     |  |

| C2SIISR<br>Section 9.6  |    |                                    | Res | erved   |       |       | SHOR<br>T<br>GND | NOIS<br>E        | Reserved   |    |    |     |      |     |                 |     |  |

| 0x18                    |    | Reserved ROVR Reserved BIT BYT ERR |     |         |       |       |                  |                  |            |    |    |     |      |     | CRC<br>ERR      |     |  |

| C2SICCSR<br>Section 9.7 |    |                                    |     | Reserve | d     |       |                  | XMIT<br>OK       |            |    |    |     |      |     | IFR<br>CRC      | IFR |  |

| 0x1C<br>C2SIBRK         |    | Reserved                           |     |         |       |       |                  |                  |            |    |    |     |      |     |                 |     |  |

| Section 9.8             |    | Reserved BREA<br>K<br>END          |     |         |       |       |                  |                  |            |    |    |     |      |     | IN<br>BREA<br>K |     |  |

| 0x20<br>C2SIINDEX       |    | Reserved                           |     |         |       |       |                  |                  |            |    |    |     |      |     |                 |     |  |

| Section 9.9             |    |                                    |     |         |       |       | Reserve          | d                |            |    |    |     |      |     | INDEX           |     |  |

| 0x24<br>C2SITDB         |    |                                    |     |         |       |       |                  | Rese             | erved      |    |    |     |      |     |                 |     |  |

| Section 9.10            |    |                                    |     | Rese    | erved |       |                  |                  |            |    |    | TDE | DATA |     |                 |     |  |

| 0x28                    |    |                                    |     |         |       |       |                  | Rese             | erved      |    |    |     |      |     |                 |     |  |

| C2SICLK<br>Section 9.11 |    |                                    |     |         | Res   | erved |                  |                  |            |    |    |     | ICL  | KFR |                 |     |  |

| 0x30                    |    |                                    |     |         |       |       |                  | Rese             | erved      |    |    |     |      |     |                 |     |  |

| C2SIEMU<br>Section 9.12 |    | Reserved REDATA                    |     |         |       |       |                  |                  |            |    |    |     |      |     |                 |     |  |

TMS470 Platform Class II Serial Interface B (C2Slb)

#### C2SIb Internal Registers

NOTE: For all registers, reading reserved locations returns zeros and writes to reserved location have no effect.

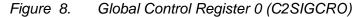

## 9.1 Global Control Register 0 (C2SIGCR0)

Figure 8 and Table 5 describe the global control register.

# Table 5. Global Control Register 0 (C2SIGCR0) Field Descriptions

| Bit | Name  | Description                                                                                                                                                                                                                             |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | RESET | Reset writing '1' reset the C2SI module to the reset condition.<br>All bits and registers except the RESET bit will be at reset value.<br>Only privileged writes will set this bit and this is the only bit that<br>requires privilege. |

# 9.2 Global Control Register 1 (C2SIGCR1)

Figure 9 and Table 6 describe this register.

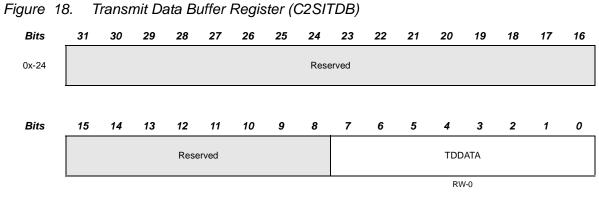

## Figure 9. Global Control Register 1 (C2SIGCR1)

| Bits  | 31 | 30       | 29 | 28     | 27  | 26   | 25        | 24        | 23 | 22 | 21   | 20   | 19          | 18         | 17    | 16   |

|-------|----|----------|----|--------|-----|------|-----------|-----------|----|----|------|------|-------------|------------|-------|------|

| 0x-04 |    | Reserved |    |        |     |      | CAL<br>EN | NB<br>POL |    |    | Rese | rved |             |            | ESPEN | LPEN |

|       | R  |          |    |        |     | RS-0 | RW-0      | RW-0      |    |    | F    | R    |             |            | RW-0  | RW-0 |

| Bits  | 15 | 14       | 13 | 12     | 1   | 1 10 | 9         | 8         | 7  | 6  | 5    | 4    | 3           | 2          | 1     | 0    |

|       |    |          |    | Reserv | ved |      |           | LPM       |    |    |      |      | CRC-<br>DIS | 4x<br>MODE | T2IFR | TIFR |

| -     |    |          |    |        |     |      |           | RW-0      | •  |    |      |      | RW-0        | RW-0       | RW-0  | RW-0 |

R = Read in all modes; S = Set only, no clear; W = Write, -n = Value after reset

# Table 6. Global Control Register 1 (C2SIGCR1) Field Descriptions

| Bit | Name    | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |